⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Производство CPU. Планы на 2003-2007-й год

- И почему люди не летают, как птицы?

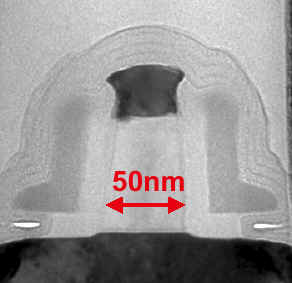

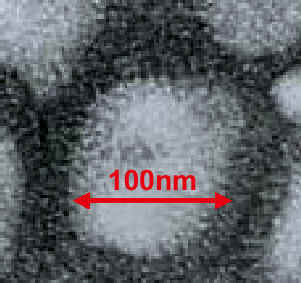

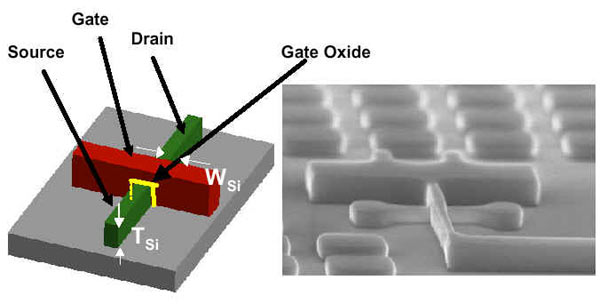

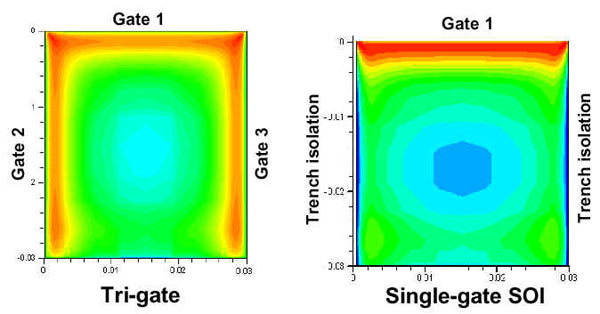

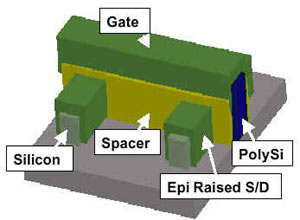

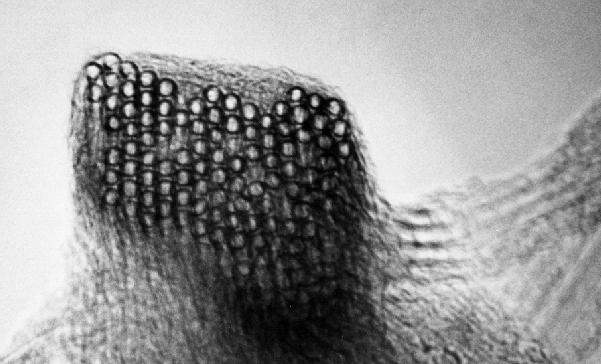

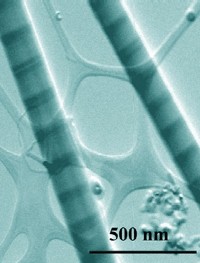

- Техпроцесс не позволяет. Задачи индустрии CPUПочему двигатели автомобилей потребляют литры бензина на сто километров, а не граммы, и почему вообще бензина, а не воды? Почему нет портативного установки холодного термояда в каждом доме? Почему, наконец, процессоры содержат всего-навсего миллионы транзисторов, работающих на частотах в единицы гигагерц? Просто потому, что большего техпроцесс на данный момент не позволяет. Технические возможности производителя, проще всего говоря. Причем, не надо путать их с потенциально возможными техническими возможностями: при желании, тот же Intel уже сегодня мог бы производить 65 нм процессоры, только объем выпуска измерялся бы в единицах или десятках, и стоили бы они на порядки больших денег. Так что, поскольку мы живем в рынке, то можно сформулировать следующим образом: техпроцесс - это результат компромисса между теоретически возможным уровнем какой либо технологии, и ценой, устраивающей массового потребителя продукции, изготовленной с ее использованием. Есть такой компромисс, разумеется, и в области центральных процессоров для PC, хотя его на данный момент трудно назвать полностью естественным: наблюдается некоторый дисбаланс в сторону превалирования производительности над ценой, во многом обусловленный успехом многомиллионных рекламных компаний производителей процессоров. Так, в последнее время Intel вкладывает в раскрутку каждого своего нового процессора (Pentium 4, Pentium-M) порядка 300 и более миллионов долларов. Однако, есть планы по продажам, есть маркетинговый цикл, закон Мура, наконец, служащий своеобразным погонным механизмом для всей процессорной индустрии, причем, надо отметить, что закон этот, сформулированный, а главное, разрекламированный и возведенный с простого, не слишком точного в данный момент наблюдения, до уровня закона, самой компанией Intel, в основе своей на благо именно этой компании и работает, поскольку полезен он главным образом для того, кто обладает на данный момент времени наибольшим техническим и производственным потенциалом. К тому же, относительная легкость, с которой до сих пор выполнялся этот закон, сослужила не самую добрую службу индустрии, поскольку инженеры работали в условиях, когда им не приходилось заботиться об эффективности функционирования отдельных модулей процессора - зачем, если можно просто выделить под каждый из них столько транзисторов, сколько заблагорассудится. Ну, или в какой-то мере так. По крайней мере, сегодня, когда стало очевидно, что в обозримом будущем закон Мура перестанет действовать, а ток утечки и тому подобные эффекты уже нельзя не замечать, вдруг начали говорить о необходимости более тщательно подходить к созданию архитектур процессоров. Это радует. Естественно, когда речь заходит о техпроцессах, применяемых при создании центральных процессоров PC, в первую очередь необходимо вспомнить Intel. Компанию, обладающую на сегодняшний день самым мощным производственным потенциалом: 25 фабрик, из них как минимум десяток занимаются выпуском процессоров. И одним из самых технически совершенных на сегодняшний день техпроцессов. И об этом - поподробнее, но сначала разберемся с несколькими базовыми понятиями. Начнем с пресловутого тока утечки, точнее - токов, поскольку их существует два вида. Первый - утечка тока затвора, вызываемый самопроизвольным перемещением электронов с отрицательно заряженного кремниевого субстрата канала в положительно заряженный поликремний затвора. Второй - самопроизвольное перемещение электронов с отрицательно заряженного истока к положительно заряженному стоку через кремниевый субстрат, находящийся под каналом транзистора, и им уже не контроллируемый. Этот эффект известен как подканальная утечка (очевидно), или утечка в выключенном состоянии (не менее очевидно, поскольку транзистор, находясь во включенном состоянии, продолжает "слегка работать"). Оба эффекта приводят к тому, что приходится поднимать как напряжение на затворе, так и, как следствие, рабочий ток, дабы компенсировать их, что, в свою очередь, самым негативным образом отражается на энергопотреблении и тепловыделении транзисторов. Здесь пора вспомнить структуру транзистора, а именно - тонкий слой диоксида кремния, изолятора, находящегося между затвором и каналом, и выполняющего вполне понятную функцию - барьера для электронов, предотвращающего утечку тока затвора. Очевидно, что чем толще этот слой, тем лучше он выполняет свои изоляционные функции, но он является составной частью канала, и не менее очевидно, что если мы собираемся уменьшать длину канала (читай - размер транзистора), то нам надо уменьшать его толщину, причем, весьма быстрыми темпами. К слову говоря, за последние несколько десятилетий толщина этого слоя составляет в среднем порядка 1/45 от всей длины канала. Так вот, уменьшать толщину этого слоя необходимо, чем производители процессоров и занимаются, несмотря на растущий при этом утечку тока затвора. Но у этого процесса есть свой конец - как утверждал пять лет назад все тот же Intel, при продолжении использования SiO2, как это было на протяжении последних 30 лет, минимальная толщина слоя будет составлять 2.3 нм, иначе ток утечка тока затвора приобретет просто нереальные величины. Для снижения подканальной утечки до последнего времени ничего не предпринималось, сейчас ситуация начинает меняться, поскольку рабочий ток, наряду со временем срабатывания затвора, является одним из двух основных параметров, характеризующих скорость работы транзистора, а утечка в выключенном состоянии на нем непосредственно сказывается - для сохранения требуемой эффективности транзистора приходится, соответственно, поднимать рабочий ток, со всеми вытекающими условиями. Одним из наиболее известных на сегодняшний день способов решения этой проблемы является SOI (silicon on insulator, кремний на изоляторе). Суть технологии, в общем-то, вполне логична - транзистор отделяется от кремневой подложки еще одним тонким слоем изолятора. Плюсов - масса. Никакого неконтролируемого движения электронов под каналом транзистора, сказывающегося на его электрических характеристиках - раз. После подачи отпирающего тока на затвор, время ионизации канала до рабочего состояния, до момента, пока по нему пойдет рабочий ток, сокращается, то есть, улучшается второй ключевой параметр производительности транзистора, время его включения/выключения - это два. Или же, при той же скорости, можно просто понизить отпирающий ток - три. Или найти какой-то компромисс между увеличением скорости работы и уменьшением напряжения. При сохранении того же отпирающего тока, увеличение производительности транзистора может составить вплоть до 30 процентов, если оставить частоту той же, делая упор на энергосбережение, то там плюс может быть и большим - до 50 процентов. Наконец, характеристики канала становятся более предсказуемыми, а сам транзистор становится более устойчивым к спорадическим ошибкам, вроде тех, что вызывают космические частицы, попадая в субстрат канала, и непредвиденно ионизируя его. Теперь, попадая в подложку, расположенную под слоем изолятора, они никак не не сказываются на работе транзистора. Единственным минусом SOI является то, что приходится уменьшать глубину области эмиттер/коллектор, что прямо и непосредственно сказывается на увеличении ее сопротивления по мере сокращения толщины - курс физики средней школы. Впрочем, минусом можно считать и лишние примерно 10 процентов увеличения себестоимости, в которые обойдется это удовольствие. Планы IntelА вот теперь можно и вернуться к Intel. На сегодняшний день, базовым для компании является техпроцесс с элементами размерностью в 130 нм (ширина затвора транзистора - 60 нм), на основе ультрафиолетовой литографии с комбинацией длин волн в 248 и 193 нм (используется для критических участков чипа). Еще нельзя сказать, чтобы компания перешла на 300 мм пластины - на сегодняшний день подавляющее большинство фабрик компании все еще использует 200 мм, а 300 мм фабрики главным образом будут отданы уже под 90 нм чипы. Когда обладаешь таким количеством фабрик, то их техническое перевооружение отнимает массу времени и денег, и самым совершенным техпроцессом всегда будут обладать всего лишь одна-две фабрики. Даже несмотря на то, что 300 мм пластины обладают явным экономическим преимуществом, увеличивая выход годных чипов с пластины по сравнению с 200 мм, по данным Intel, в 2.25-2.5 раз, выход чипов вообще с фабрики, при производстве одних и тех же чипов - в 1.6-2.2 раза, при одинаковой стоимости фабрик. Итого, конечная себестоимость чипа, в среднем, уменьшается на 30 процентов. Впрочем, основные вещи от диаметра пластин все же не зависят - шесть слоев металлизированных проводников везде остаются неизменными, везде остаются медными: с алюминием, бывшим безальтернативным выбором в начале 90-х, уже давно распрощались все крупные производители чипов. Точно так же, как стандартом для любого последнего процессора Intel остается упаковка FCPGA. Впрочем, некоторые изменения здесь произойдут уже в этом году, с переходом на 90 нм техпроцесс. Впрочем об особых изменениях здесь речи не идет, достаточно сказать, что Intel намерен сохранить при переходе от 130 до 90 нм порядка трех четвертей всего используемого оборудования (речь идет о том 130 нм техпроцессе, который используется с 300 мм пластинами, разумеется). Еще бы - учитывая количество фабрик, которые с течением времени придется на него переводить.   90 нм транзистор и вирус гриппа Структура транзистора изменится несколько больше. Не в количественном выражении - ширина канала уменьшится всего лишь с 60 до 50 нм, поскольку токи утечки уже при 130 нм техпроцессе начали становиться настоящим бичом новых процессоров, а они, при прочих равных, прямо зависят от ширины канала, которая, в свою очередь, связана со скоростью и размером транзисторов. Пытаясь, при сохранении положительных эффектов изменений, нивелировать их отрицательные стороны, Intel в своем 90 нм техпроцессе начал использовать такие вещи, как "растянутый кремний", очень тонкий слой оксида в затворе, и новый Low-k диэлектрик для изоляции медных соединений - обогащенный углеродом оксид. Очень тонкий слой оксида действительно очень тонкий - 1.2 нм, что полностью соответствует уже известному нам правилу, что его толщина должна составлять 1/45 от глубины канала, которая у 90 нм транзистора примерно равна ширине. Но ведь выше уже шла речь об ограничении в 2.3 нм. Ну что же, очевидно, что если поверить Intel, утверждающему, что он продолжает использовать SiO2, то компании пришлось предпринять какие-то действия, позволившие повысить его изолирующие способности, возможно, сжав кристаллическую решетку. В будущем, впрочем, компания перейдет к более радикальным мерам, но об этом чуть позже. Растянутый кремний. Его задача целиком и полностью противоположна предыдущей. Если слой оксида предназначен для предотвращения прохода по нему электронов, то прямо под ним находится тот самый переход по которому электроды, при открытом затворе, перемещаются с эмиттера на коллектор. И вот тут то требуется, чтобы ток был максимально большим, чтобы электроны совершали этот путь максимально легко и быстро. Обычно материалом канала служит кремний, но в данном случае его еще и "растянули", сделав так, что атомы изначальной кристаллической решетки разошлись на большее расстояние друг от друга. Очевидно, что чем больше пространство между атомами материала, тем меньшее сопротивление испытывают проходящие сквозь него электроны. По утверждению Intel, результат применения растянутого кремния выражается в увеличении рабочего тока на 10-20 процентов, причем за счет возрастания себестоимости всего на 2 процента. Еще одним дополнительным моментом в 90 нм техпроцессе стал седьмой слой металлических (медных) проводников, обеспечивающий большую гибкость при создании комплексных процессоров, состоящих из более чем ста миллионов транзисторов, вроде того же Prescott. Но тут все совсем понятно и очевидно, и не нуждается ни в каких дополнениях. Разве что только то, что здесь Intel традиционно на шаг отстает от наиболее передовых техпроцессов. В то время, когда ведущие производители предлагали техпроцессы с семью слоями металлизации, компания в своем 130 нм использовала шесть. Сейчас Intel будет использовать семь - а компании вроде IBM уже объявили техпроцессы с восемью.  Это, правда, шесть слоев, но, зато - красиво. ;) Надо лишь добавить, что по мере уменьшения транзисторов и, соответственно, увеличения их количества в процессоре, ситуация с металлическими проводниками между ними, начинает играть все более важную роль, в частности, уже с их емкостью, влияющей на скорость передачи информации. В своем 90 нм техпроцессе Intel начал применять новый диэлектрик между соединениями - на смену SiOF пришел обогащенный углеродом оксид, по утверждению Intel, увеличивающий эффективность их работы на 18 процентов. Prescott еще только предстоит пойти в массовое производство, пока же Intel демонстрирует свои новые возможности на SRAM, являющейся, впрочем, основой одного из ключевых элементов сегодняшних процессоров - кэш-памяти. С помощью 90 нм техпроцесса компании удалось поставить новый рекорд, разместив 6-транзисторную ячейку SRAM на площади всего лишь в один квадратный микрон, что дает 52 Мбит для чипа с размерами 10х11 мм, состоящего из 330 миллионов транзисторов, почти в 8 раз больше, чем число транзисторов в Pentium 4. Таким образом, 8 Мбит кэша второго уровня у Prescott будут располагаться на площади всего лишь около 4х4 мм!  Тот самый СРАМ :) Таким для Intel является настоящее, а что же ждет нас в будущем? В первую очередь, конечно же, движение по привычному пути развития, выжимая остатки возможного из кремниевых транзисторов - то, что в Intel называется TeraHertz Transistor. Несмотря на то, что даже сегодняшние технологии позволяют в единичном экземпляре произвести транзистор с размерностью всего лишь в 15 нм, очевидно, что при том количестве транзисторов, которое подразумевают такие размеры, энергопотребление и тепловыделение чипа в целом, а также суммарный ток утечки, сделают невозможным его практическое использование без кардинальных новшеств в техпроцессе. TeraHertz Transistor - это, как легко можно понять, в первую очередь замена материалов, поскольку именно они определяют базовые характеристики транзистора. Окончательно производится отказ от использования диоксида кремния в роли разделительного слоя между затвором и каналом - ему на смену приходит некий материал, называемый Intel "high k gate dielectric", по утверждениям компании уменьшающий утечку электронов с канала в затвор в 10 тысяч раз по сравнению с SiO2. Сказанного ранее достаточно для того, чтобы понять всю важность этой, давно назревшей замены: она позволяет в будущем снизить толщину изолирующего слоя до десятых долей нанометра, при сохранении вполне приемлемых значений утечка тока затвора. Вторая ключевая деталь - это то, что в Intel называют "транзистор с обедненным субстратом", технология, фактически, являющаяся разновидностью SOI. Но с улучшениями - Intel всегда очень настороженно относился к SOI, и просто так он бы его использовать не начал. В свое время у компании были очень серьезные возражения против SOI в любом из его вариантов: с каналом, где лишь часть его является обедненной, или же вся длина канала. В первом случае, по мнению Intel, особых выгод не появляется, а во втором - потребуется делать канал очень малой длины, порядка 10 нм, что очень сложно в производстве и приведет к тому, что очень сильно возрастет внешние сопротивление транзистора по причине уменьшения глубины эмиттера и коллектора. Поэтому транзистор с обедненным субстратом (depleted substrate transistor, DST) представляет из себя первый подход, с полностью обедненным каналом, но с небольшой модификацией, устраняющей его основной минус: канал сделан действительно очень коротким, полностью обедненным, так что сохраняется полный контроль над ним, рабочий ток, проходя непосредственно под затвором, не ионизирует находящуюся под проводящим слоем часть канала транзистора, вызывая эффект его виртуального удлинения, в результате чего характеристики транзистора начинают "плыть". Но все это пока в равной мере относится и к обычному SOI транзистору с полностью обедненным каналом - вопрос по прежнему остается в серьезном росте внешнего сопротивления. Так вот, у DST Intel не позволил влиять глубине канала на глубину стока и коллектора, нарастив необходимую разницу в глубине не вниз, как обычно, а вверх. Все зайцы убиты одним выстрелом: по прикидкам Intel, более чем существенное сокращение тока в нерабочем состоянии даст возможность и дальше продолжать неуклонное понижение питания, ниже 1.0 В, и где-то до 0.6 В к 2010 году.  Вот, собственно говоря, сочетание этих двух вещей, high k диэлектрик затвора и транзистор с обедненным субстратом, Intel и называет TeraHertz Transistor, имея на это, кстати, полное право - в комплексе, они делают возможным создание 32 нм (раза в три меньше, чем вирус гриппа) транзисторов с длиной канала до 15 нм и напряжением порядка 0.75 В, действительно работающих на частоте в 1 TГц. Впрочем, на этом новведения Intel в области транзисторов не заканчиваются. В той же половине нынешней декады, когда начнется использование технологий, составляющих TeraHertz Transistor, Intel намерен совместить их с новой архитектурой самого транзистора - Tri-gate Transistor. Последние три с половиной десятка лет в микроэлектронике используется одна и та же структура транзистора: управляющий электрод, два под ним, и идущий от одного из них к другому поток электронов. Практически двумерная схема - плоскость. В последнее время лидеры микропроцессорной отрасли начали серьезные исследования в области уже "трехмерных" процессоров, с несколькими затворами и каналами. Как понятно по названию, Intel в своей экспериментальной архитектуре предлагает использование трех каналов в одном транзисторе. Об ограничениях традиционной архитектуры выше было сказано - фактически, борьба с утечками поглощает сегодня большинство усилий инженеров. Требуется либо выжимать по капле возможности из обычных транзисторов, либо перейти на что-то новое. Что же из себя вообще представляет транзистор с тремя каналами. Во-первых, он действительно трехмерный даже на первый взгляд - из привычной плоскости кремниевой пластины выступает затвор и эмиттер с коллектором, представляющие из себя крестообразное пересечение: брусок эмиттера/коллектора, пересеченный бруском затвора, изолированного в местах пересечения привычным оксидом. Как бы перевернутый транзистор, не врастающий в пластину, а вырастающий из нее.  Таким образом, транзистор работает сразу в трех измерениях: место среза затворного бруска представляет из себя прямоугольник, верхней и боковыми сторонами которого являются электроды - затворы. Сравнить с проекцией обычного транзистора, где у того же прямоугольника управляющий электрод находится лишь сверху, со всеми вытекающими отсюда обстоятельствами: канал приходится заряжать/разряжать для включения/выключения транзистора гораздо дольше, а напряжение для этого прикладывать - гораздо больше.  Но на этом все отнюдь не заканчивается, напротив - все только начинается. Кто сказал, что затворный брусок можно пересечь лишь одним бруском эмиттера/коллектора? Никто не мешает нам пересечь его сразу несколькими такими брусками, и в результате получится следующая картина: мы включаем транзистор, подавая отпирающий ток на затвор по всей его длине. В результате ток начинает течь во всех брусках, пересекающих затворный, правильно? А рабочий ток транзистора в целом, который, стоит напомнить, является одним из основных параметров его производительности, будет равен сумме значений рабочего тока каждого из таких пересечений! Таким образом, к примеру, с шестью выводами (три - эмиттер, три - коллектор), грубо говоря, не беря в рассмотрение куда большую эффективность (до 20 процентов), мы получаем либо тот же рабочий ток, что и у обычного транзистора при втрое меньшем исходном напряжении, либо, при том же - втрое больший рабочий ток. Дело можно было бы затевать уже только ради этого.   На первый взгляд трехзатворные транзисторы имеют все преимущества по производительности перед своими классическими собратьями, в то же время, будучи способными производиться с использованием того же оборудования и технологий (включая те, что лежат в основе TeraHertz Transistor), а в некоторых отношениях они даже более легки в производстве, облегчая, скажем, требования по длине канала в 2-3 раза, что очевидно, учитывая куда большую его эффективность с тремя затворами. По сути, здесь можно поставить знак равенства между длиной затвора классического транзистора, и произведением высоты на ширину затвора - у трехзатворного. Очевидно, что величины получатся несравнимые. Тем не менее, пока что эта разработка числится в сугубо экспериментальных, с прицелом на возможное использование во второй половине нынешней декады. Естественно, что для того, чтобы обеспечить производство процессоров с транзисторами такой размерности, соответствующим образом должна развиваться литография - процесс, с помощью которого и появляются транзисторы на поверхности кремниевой пластины. Сейчас у Intel, как уже упоминалось, переходный этап - для создания ряда элементов 90 нм чипа удалось приспособить старое доброе 248 нм оборудование, для особо критичных участков - используются новые 193 нм установки, впрочем, таких участков, по данным Intel, набирается менее 20 процентов. Теперь же компания может позволить себе несколько расслабиться, потихоньку увеличивая долю 193 нм оборудования, поскольку его потенциала хватит и для производства чипов с 65 нм транзисторами. Хотя и там придется использовать аналогичную смесь из 193 нм систем с уже созданными сегодня 157 нм устройствами, работающими в D1C в Орегоне. Дальше уже наступит черед Extreme Ultraviolet (EUV) Lithography, использующей свет с длиной волны 13.4 нм (сравним с сегодняшними 193 нм!), которой последние годы занимается консорциум EUV LLC, состоящий из всех ведущих производителей литографического оборудования и производителей чипов. Дела идут достаточно гладко, первые маски были созданы еще в начале 2001 года - с размерностью элементов в 200 нм, однако, пока свет через систему зеркал дойдет до поверхности кремниевой пластины, изображение будет сжато в четыре раза, так что с помощью таких масок вполне можно печатать элементы с размерностью в 50 нм. Как раз то, что и требуется. Впрочем, на достигнутом никто не останавливается - дальше на очереди маски со 120 нм разрешением, которое понадобится уже к концу этого десятилетия для создания 30 нм транзисторов. Intel ожидает начала использования EUV при производстве процессоров где-то с 2005 года, когда компания займется производством чипов по 45 нм техпроцессу.  Опытный образец EUV установки С преодолением всех преград, препятствующих увеличению транзисторов на чипе (а следовательно - и росту количества контактов у процессора) во весь рост станет другой сопутствующий вопрос - использование адекватной таким масштабам упаковки чипа, поскольку без соответствующей защиты, подвода энергии и отвода тепла, обеспечению надежного использования всего этого множества сигнальных линий, потенциал чипа попросту невозможно будет использовать. Впрочем, ответ на этот вопрос у Intel уже имеется - это Bumpless Build-Up Layer (BBUL). Очень логичная, если не сказать - красивая, технология. Что представляет из себя сегодняшняя FCPGA? Чип крепится сверху основного корпуса, соединяясь с ним посредством предназначенных специально для этой цели контактных площадок из органического материала - solder bumps. От контактных площадок сигнал идет к слоям металлических соединений, расположенных в верхней части корпуса, а дальше, через каналы в нем, в нужном порядке добирается до нижних слоев проводников, подсоединенных уже к выводам процессора. По сравнению с теми методами, что были раньше - прогресс очевидный: толщина процессора составляет всего порядка 2 мм (1 мм на корпус, 1 мм - на чип с контактными площадками), открытость верхней поверхности чипа позволяет организовать достаточно эффективное охлаждение через металлическую крышку, прикрывающую чип от повреждений. Но: всегда есть место для улучшений. BBUL в этом плане делает достаточно много. В основе этого метода упаковки лежит размещение чипа непосредственно в корпусе, в специально предназначенной для этого нише. В результате, как минимум становится вдвое меньше высота, и легче сам корпус, что очень важно для тех же ноутбуков, но затевалось все отнюдь не только ради этого. Все слои металлических соединений теперь находятся внизу, между чипом и ножками процессора, так что органики больше нет - на всем пути следования сигнала находится медь, что соответствующим образом отражается на его надежности. Вдобавок, отсутствие контактных площадок позволяет легче развести большее количество соединений.  Конденсаторы, питающие чип, расположены теперь гораздо ближе к нему, не будучи отделены от него всей толщей корпуса. Так что можно и требования по питанию слегка ослабить, и проще подавать его непосредственно туда, где оно необходимо. Кстати, особенно удобен такой корпус для встраивания в него нескольких чипов, вплоть даже до процессора, памяти, графического чипа и чипсета. В общем, плюсов для комплексных продуктов вполне хватает, и уже с 2005-2006 года Intel должен будет начать использовать BBUL в своих коммерческих продуктах. Говоря о совсем уж отдаленной перспективе: естественно, как и конкуренты, Intel активно изучает "жизнь после кремния", в частности, совместно с учеными Гарварда изучая кремниевые нановолокна и углеродные нанотрубки. Сегодня они выглядят предпочтительными кандидатами на роль технологий "пост'2010", какая же именно из них выйдет победителем - говорить пока что рано. Планы AMDВ отличие от Intel, их ближайший конкурент, AMD, отнюдь не так силен как по части производственного потенциала, так и по части разработки новых технологий, что естественно, учитывая, что ежегодные объемы капвложений компаний отличаются почти на порядок. AMD обладает всего лишь парой фабрик, на которых она способна производить свои процессоры, да и то Fab25 частично занимается производством флэш-памяти. Все новые процессоры компании производятся на одной единственной фабрике Fab30, расположенной в окрестностях Дрездена и обладающей самым совершенным техпроцессом, находящимся в распоряжении AMD.  AMD'шный Clean Room Если во времена 0.25 мкм AMD еще могла на равных конкурировать с Intel в плане технологий, то ко временам 0.18 мкм отставание уже начало проявляться. В виду нехватки собственных сил, компании пришлось искать стратегического партнера, в качестве которого была выбрана Motorola, действительно обладающая на тот момент одним из самых совершенных техпроцессов, используемым, например, при производстве чипов PowerPC для Apple - HiPerMOS 7 (HiP7). AMD получила лицензию на него, получив вместе с ней в свое распоряжение набор технологий, более эффективных, чем 130 нм техпроцесс Intel. Во-первых, он полностью основывался на использовании 248 нм оборудования, что сделало его внедрение более дешевым (что для AMD критично в особенности), а также позволило быстрее начать массовое производство. Хотя AMD и упоминала о возможности использования 193 нм сканнеров для особо критичных участков, как это делает Intel. Во-вторых, в отличие от 130 нм техпроцесса Intel (P860), HiP7 выдвигает слегка более мягкие требования: длина канала составляет 80 нм против 70, а толщина слоя оксида под затвором 1.8/2.5 нм (для быстрых и основных транзисторов) против 1.5 и 2.4 нм у Intel. Наконец, HiP7 обеспечивает возможность использования до 9 слоев медных соединений против 6 в P860. И, наконец, в отличие от P860, предполагающего использование в качестве диэлектрика, изолирующего межтранзисторные соединения, стандартного флюоросиликатного стекла, SiOF, с k=3.6, HiP7 дал AMD возможность выбора между флюоросиликатным стеклом с 3.7, и low-k диэлектриком от Applied Materials - Black Diamond, с k<3.0. Эффект примерно тот же, что и от замены алюминия на медь. Здесь, благодаря Motorola, AMD вырвалась вперед, став третьим после IBM и Motorola производителем центральных процессоров, использующим low-k диэлектрики. Intel от SiOF, как мы уже знаем, отказался только в 90 нм техпроцессе. Сейчас AMD готовится к вводу в коммерческую эксплуатацию уже HiP8, следующего поколения техпроцесса, который станет ответом на 90 нм P1262 от Intel. Пробные чипы на его основе уже произведены, полный же перевод Fab30 на HiP8 ожидается к концу 2004 года. В принципе, с ним AMD вновь окажется на полшага впереди своего конкурента. Хотя бы потому, что здесь будет применен SOI, который у Intel только еще намечается в в программе TeraHertz Transistor. Это при том, что теоретически компании ничего не мешало начать использовать SOI уже в 130 нм техпроцессе, благо, что HiP7 это вполне позволял. Возможно, что связанный с этим рост внешнего сопротивления транзисторов оказался неприемлемым на данный момент - по слухам, опоздание Opteron/Athlon 64 во многом связано как раз с безуспешными попытками использовать таки при их производстве SOI. Сейчас AMD должна все же его применить, что должно отразиться на скорости переключения транзисторов соответствующим образом - опыт использования этой технологии говорит об улучшении вплоть до 20 процентов. Вдобавок, незначительно уменьшается ток утечки и ширина затвора. Что касается будущего с точки зрения технологий, то здесь AMD, как и остальные, на данный момент экспериментирует со всеми вещами, которые считаются перспективными на данный момент. Тут и замена в изолирующем слое диоксида кремния на метал-силикат High-k диэлектрик, хотя AMD называет куда меньшую цифру эффективности, чем Intel - сокращение тока утечки затвора не в 10000, а всего в 100 раз. Тут и смешанный SiGe субстрат вместо чистого кремния в той части канала, через которую идет рабочий ток. Это тот самый растянутый кремний, который начал использовать Intel в своем 90 нм техпроцессе: используется физическое явление, когда кристаллическая решетка кремния подстраивается под кристаллическую решетку находящегося ниже материала, в данном случае - германия, растягиваясь под ее структуру. В результате, по данным IBM, сопротивление потенциально падает до 70 процентов по сравнению с обычным кремнием, что приводит к ускорению работы транзистора до 35 процентов.  Возвращаясь к растянутому силикону Тут и возможность использования многозатворных транзисторов, хотя AMD более внимательно приглядывается к двухзатворным вариантам, отличающимся от трехзатворного транзистора, ставшего фаворитом Intel, отсутствием верхнего управляющего электрода. За счет этого, Fin Field Effect транзистор (FINFET) AMD, как и любой другой подобный транзистор, получается более высоким, но с более узким бруском коллектор/эмиттер. Настолько узким, что ширина его получается где-то на треть уже, чем ширина затвора. Что создает понятные затруднения при литографии. Это тот случай для транзистора, когда "мало" - не значит "хорошо". Тем не менее, как и у любого другого трехмерного транзистора, преимущества FINFET перед традиционной схемой, особенно при малой длине канала - неоспоримы. В общем - все те же самые вещи, что и у Intel: аналог TeraHertz Transistor + 3D транзисторы. Набор карт на руках у AMD ничем не уступает тому, что имеется на данный момент на рыках у ее конкурента. Впрочем, учитывая, что AMD в последнее время резко изменила свою ориентацию с Motorola на IBM (с промежуточной остановкой на UMC), и HiP8 станет последним техпроцессом Motorola, который будет использовать в своих процессорах компания, в этом подходе могут наметиться определенные изменения. Хотя вряд ли они будут слишком кардинальными - IBM во многом исповедует те же самые подходы, что и AMD с Motorola. Планы IBMКомпания традиционно считается технологическим лидером среди производителей процессоров, первой начав использовать в своих коммерческих продуктах такие технологии, как медные соединения, low-k диэлектрики, или SOI, неудивительно, что именно ее AMD выбрала в качестве своего партнера для 65 и 45 нм техпроцессов. Сейчас базовым для IBM является 130 нм техпроцесс 8SF из фирменной линейки Blue Logic, на котором делаются как PowerPC, так и Power4 чипы для серверов и суперкомпьютеров. Он сочетает в себе практически все наработанные на сегодняшний день IBM технологии производства, упомянутые только что. Самым же совершенным на сегодняшний день является Blue Logic Cu-08, позволяющий компании производить процессоры, состоящие из 72 миллионов транзисторов с шириной затвора 70 нм, питанием от 0.7 В, и тепловыделением 0.006 мкВт/транзистор/МГц. Цифра 8 в названии процесса означает количество слоев металлических соединений в чипе. IBM получила первый заказ на чип, созданный с применением Cu-08, FPGA матрицу от Xilinix с 90 нм транзисторами, еще в декабре прошлого года, массовое же производство таких чипов на новейшей фабрике компании в East Fishkill, начнется со второй половины этого года. Ее новая фабрика площадью в 140 тысяч квадратных футов обошлась компании в 2.5 миллиарда долларов, но она предлагает лучшее, что доступно на сегодняшний день - 300 мм пластины в сочетании с 90 нм техпроцессом и технологиями типа SOI и low-k диэлектриков. Впрочем, IBM продолжает задавать тон и в обозримом будущем, сохраняя за собой титул технологического лидера. Тут и транзисторы, которые компания предлагает выращивать один над другим, создавая многоэтажные структуры, экономя площадь чипа, и уменьшая количество требуемых металлических соединений, хотя IBM пока испытывает сомнения по поводу тепловыделения подобных конструкций. Тут и SiGe транзисторы, когда на кремниевую подложку наносится слой кремния, обогащенного небольшой примесью германия. Несколько более дорогой техпроцесс, которым IBM занимается с начала 80-х, предлагая сегодня под названием RF CMOS, тем не менее, находит свое применение в производстве коммерческих чипов, в первую очередь - для коммуникационного оборудования, где ценятся его высокие частоты и низкое энергопотребление по сравнению с традиционными кремниевыми транзисторами. Сегодня IBM заявляет о возможности того, что в течение ближайших двух лет, в своем техпроцессе BiCMOS 9HP (линейка техпроцессов BiCMOS позволяет сочетать в одном устройстве блоки на биполярных SiGе транзисторах и на обычных кремниевых CMOS) она предложит клиентам возможность использования SiGe транзисторов с частотой до 350 ГГц, что даст возможность создания чипов с частотой до 150 ГГц. Те, кому не требуется такая частота, смогут использовать эти же транзисторы с пониженным питанием, что выразится в сниженной скорости, но и в просто мизерном энергопотреблении. Тут и, естественно, уже упоминавшиеся нанотехнологии, которые очевидно придут на смену сегодняшней литографии после 2010 года. Еще бы: EUV позволит продлить жизнь сегодняшним транзисторам, пусть они даже будут к тому времени трехмерными и многоэтажными, до ширины затвора порядка 30 нм, но дальше резервы этого подхода выглядят уже окончательно исчерпанными. Причем, не только в инженерном плане! В коммерческом смысле литография тоже зашла в тупик: фабрику стоимостью в миллиарды долларов, на переоборудование которой в последующем надо ежегодно выделять сотни миллионов, трудно назвать нормальным явлением. Тут то и появляются на горизонте нанотехнологии, предлагающие совсем другой подход, когда транзисторы не "печатаются" на кремниевой пластине, а буквально собираются сами из самоорганизующихся молекул. Примерно таким же образом, как мельчайшие капельки воды кристаллизуются на морозе в геометрически правильные снежинки. Как уже упоминалось, неясно, какая из двух технологий станет победителем, хотя создается впечатление, что IBM больше внимания уделяет карбоновым нанотрубкам. Они были открыты в 1991 году ученым из NEC, Sumio Iijima, во время изучения под электронным микроскопом материала, осадившегося на графитовый катод во время синтеза фуллеренов методом осаждения. Iijima обнаружил, что в осадке находится ряд неописанных до того времени закрытых графитовых структур, в том числе и в виде пресловутых трубок. Занявшись этим вопросом, NEC достаточно быстро обнаружил, что меняя условия процесса осаждения, можно добиться массового производства нанотрубок. Правда, в оригинальном состоянии наблюдались лишь многослойные экземпляры, но через пару лет, когда этим направлением занялись уже всерьез, и не только в NEC, удалось открыть, что при добавлении к графитовому электроду некоторых металлов, вроде кобальта, можно получать и трубки прекрасного качества с однослойными стенками. В 1996 году метод был модифицирован Richard E. Smalley, в результате чего все те же трубки приобрели тенденцию выстраиваться в своеобразные скопления, получившие название канатов. Правда, в результате всех этих модификаций в этой смеси встречались как карбоновые, так и металлические трубки, но не так давно IBM был найден метод избирательного уничтожения последних, что стало очередным этапом на пути к промышленному применению нанотрубок в микроэлектронике.  Тот самый канат Меняя их материальную структуру, и получая, в зависимости от этого, трубки либо с проводящими, либо с изолирующими свойствами, и собирая из них под атомным микроскопом транзисторы, ученые уже экспериментируют с простейшими электронными структурами, признавая, в то же время, что здесь еще должны пройти несколько лет и несколько прорывов, прежде чем станет возможным коммерческое применение этих технологий. Возможно, что раньше, чем появятся чипы, сделанные исключительно из нанотрубок, мы увидим гибриды, где нанотрубки будут отвечать, к примеру, за гомогенные структуры высокой плотности, вроде кэш-памяти. Схожей альтернативой являются нановолокна - действительно микроскопические волокна, составленные из уже привычных кремния и кремния, обогащенного германием (SiGe), расположенных слоями по всей длине волокна. Очевидно, что меняя свойства этих участков есть возможность получать любые полупроводниковые устройства, а компактность волокон, вдобавок, могущих пересекаться как угодно, позволяет разместить на площади, где сегодня размещаются миллионы транзисторов - миллиарды. Процесс получения нановолокон по сути своей очень схож с тем, в результате которого получаются нанотрубки: химическое осаждение в комбинации с пульсирующим испарением лазером. Кремниевая пластина покрывается тончайшим слоем золота, камера нагревается. Под воздействием нагрева, золотая пленка плавится, превращаясь на капли нанометровых размеров. Затем на эти капли осаживаются пары кремния и германия: когда лазер выключен - только кремния, когда включен - и кремния, и германия, так контролируется процесс. По словам самих ученых, процесс выращивания заданной нановолокон заданной структуры с помощью запрограммированного на ту или иную последовательность лазера, чем-то напоминает процесс полимеризации.  Волокна. Это которые две большие! Темные полоски - SiGe, светлые - просто силикон. За час удается вырастить миллионы таких слоеных волокон по весьма низкой цене.В этом то вся и суть: нанотрубки, или нановолокна, кто бы из них не оказался победителем в конце концов, возможно новая технология позволит при заметном увеличении плотности транзисторов если не удешевить процесс, то хотя бы оставить его на уровне, близком к сегодняшнему. Планы UMC и TSMCКстати, пора бы действительно вернуться к сегодняшнему дню, и переместиться несколько юго-восточнее - на Тайвань, где находятся фабрики двух крупнейших местных полупроводниковых гигантов, UMC и TSMC. В отличие от всех вышеперечисленных компаний, эти не производят продуктов под собственной торговой маркой, занимаясь исключительно контрактным производством. Как правило, обе фирмы воспринимаются как игроки одного уровня, тем не менее, TSMC, по крайней мере, в последние годы, явно находится на полшага впереди своего конкурента. Основанная в 1987 году, на данный момент компания обладает семью 200 мм фабриками и двумя 300 мм, наиболее тонким используемым техпроцессом является 130 нм - 8 слоев медных соединений с low-k диэлектриком, транзисторы с шириной затвора до 80 нм. В принципе, не так уж плохо по сравнению с остальными. В том числе, и по темпам внедрения - производство началось еще в конце 2000 года, из успешных общеизвестных продуктов можно назвать VIA C3. К сожалению, нельзя сказать, чтобы техпроцесс использовался столь же успешно на всех фронтах, широкоизвестная история с провалом первоначального выпуска чипов для NVIDIA тому лучшее подтверждение. На десятках миллионов транзисторов в чипе 130 нм техпроцесс TSMC не смог обеспечить требуемого выхода годных чипов, что вынудило NVIDIA впервые за все время их сотрудничества прибегнуть к поиску второго партнера для производства. IBM предпочитает именно таких клиентов - со сложными заказами, и у нее есть лучшие на данный момент технологии. Неудивительно, что выбор NVIDIA пал именно на нее. Тем не менее, не стоит судить обо всем по данной неудаче, частично вызванной торопливостью NVIDIA, на которую та имела свои причины. Прогресс TSMC продолжается, и сегодня компания уже практически имеет в своем распоряжении свой 90 нм техпроцесс, впервые получивший персональное название - Nexsys. Подобно последним техпроцессам ранее названных компаний, он позволяет сочетать в рамках одного чипа транзисторы со слоями оксида разной толщины (три варианта, если быть точным), что позволяет комбинировать более экономичные транзисторы, работающие с нормальной скоростью, с более быстрыми, но и более прожорливыми и горячими. Длина канала транзистора также примерно соответствует показателям американских компаний - 50 нм, а вот по слоям металлических соединений с TSMC может поспорить лишь IBM - 9 слоев медных проводников с изоляцией из low-k диэлектриков с k<2.9. Одновременно с IBM намеревается TSMC начать и массовое производство чипов на базе Nexsys - со второй половины этого года. Естественно, что, поскольку компания является контрактным производителем чипов, как и IBM, она должна иметь в своем распоряжении максимальное количество техпроцессов, пригодных для нужд всех своих текущих и потенциальных клиентов. В отношении TSMC это справедливо на все сто процентов: в ее ассортимент входят в том числе и такие вещи, как уже упоминавшиеся SiGe BiCMOS устройства. Компания не объявляет широко о своей R&D деятельности, но годовой бюджет в этой области около 300 миллионов долларов и теснейшие связи с большинством разработчиков на этом рынке (вроде Applied Materials), не говоря уже о том, что, ряд из них, как, например, Philips Electronics имеют прямой материальный интерес в TSMC, поскольку являются одними из ее совладельцев, то, очевидно, что компания находится в струе, и намерена и дальше оставаться в числе технологических лидеров. По крайней мере, это уж точно относится к разрабатываемому совместно Philips/ST Microelectronics/TSMC 65 нм техпроцессу. Точно так же, как самостоятельно, так и через партнеров подобного уровня, компания занимается и разработками, нацеленными в более отдаленное будущее, внимательно изучая все возможные альтернативы. Хотя, конечно, и не в такой степени, как ее американские, японские, или европейские конкуренты, традиционно уделяющие более значительное внимание фундаментальным исследованиям. Примерно то же самое будет справедливым и относительно UMC, делая поправку на более мелкие масштабы деятельности той. И R&D бюджет около 250 миллионов долларов в год (сравним с 4 миллиардами долларов у Intel в этом году), и не столь успешный опыт сотрудничества с другими компаниями (а здесь будет уместно вспомнить неудавшееся партнерство с AMD). Тем не менее, недооценивать UMC было бы совершенно неуместно. Пусть с опозданием, но компания только что начала коммерческое производство чипов по своему 130 нм техпроцессу (первой, как обычно, отметилась Xilinix с одной из своих FPGA матриц) - 8 слоев медных соединений с low-k диэлектриками (k=2.7), два варианта транзисторов, длина канала транзистора - до 70 нм. Вполне нормально для 130 нм техпроцесса, хотя, конечно, и заметно позже, чем у всех остальных. Может быть поэтому AMD и предпочла для партнерства более сильного игрока. Но, с другой стороны, одновременно UMC начала и поставку своим клиентам образцов чипов, сделанных уже по 90 нм техпроцессу, доказывая, что на этом этапе компания вновь готова занять свое место в строю. При этом, L90 является абсолютно конкурентоспособным продуктом, со своими 9 слоями металлизации и тремя вариантами оксида в транзисторах. Впрочем, сумеет ли UMC в этом году сделать L90 достаточно дешевым для коммерческого использования - это еще очень большой вопрос. К сожалению, компания отличается тем, что она первой, или одной из первых, демонстрирует новые технологии (ей принадлежит наибольшее количество патентов в области полупроводниковых технологий на Тайване), но в массовое использование вводит их одной из последних.  Как и TSMC, ей приходится иметь в своем распоряжении весь спектр техпроцессов, от чистой CMOS логики или BiCMOS SiGe, до RF CMOS или CIS фотоматриц. Так, 0.18 мкм BiCMOS SiGe техпроцесс должен будет стать доступным для клиентов уже во второй половине этого года, придя на смену использующемуся сегодня его 0.35 мкм предшественнику. Новое поколение же чистых CMOS процессов, L65, как явствует из названия, с 65 нм транзисторами, UMC планирует ввести в строй где-то в первой половине 2005 года, примерно в тех же временных рамках, когда это сделают ее конкуренты. Вероятно, там может появиться и SOI, работы над которым UMC ведет. Естественно, несмотря на удачу с AMD, у UMC хватает связей в своей области. В первую очередь, безусловно, ключевым партнером компании является Infineon, с которым, как и с IBM, UMC заключила в 2000 году соглашение о совместных разработках в области техпроцессов. Однако о дальнейшем сотрудничестве с IBM почти никакой публичной информации нет, тогда как с Infineon UMC построила совместную фабрику в Сингапуре - UMCi, а также, уже в прошлом году, сформировала совместную исследовательскую команду по разработке 65 и 45 нм техпроцессов для 300 мм пластин. Разумеется, этим дело не ограничивается, и у UMC имеется совместная команда разработчиков и со все той же ST Microelectronic, и история успешной тесной работы с Intel, TI, AMD, и Motorola, в том числе и в области фундаментальных исследований. Вот и был продемонстрирован срез лучших компаний, работающих сегодня с CMOS логикой, в частности, можно сказать, что и с x86 процессорами (IBM - совместимый с x86 Crusoe, UMC - потенциально, Athlon XP). Состояние дел у этой пятерки на данный момент очень хорошо характеризует положение дел в индустрии в целом, то же самое относится и к их планам. В особенности, конечно, это касается таких монстров, как Intel и IBM, хотя к ближней и средней перспективе это применимо и к UMC с TSMC.

|