Так же как и в случае с архитектурами Sandy Bridge, Ivy Bridge и Haswell, на базе которых Intel выпускала процессоры для установки в разъем LGA2011, архитектура Broadwell пришла в нишу двухсокетных серверов и рабочих станций позже, чем на рынке появились родственные CPU для мобильного сегмента и десктопные чипы Broadwell, на этот раз немногочисленные и оставшиеся в тени развернутой вскоре линейки Skylake.

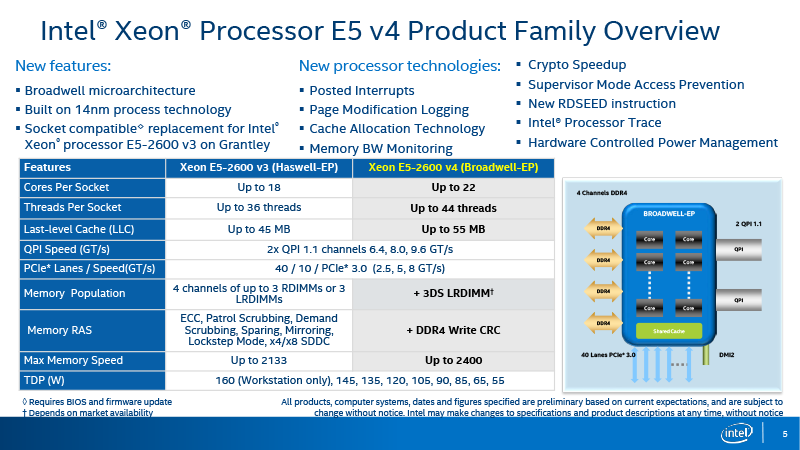

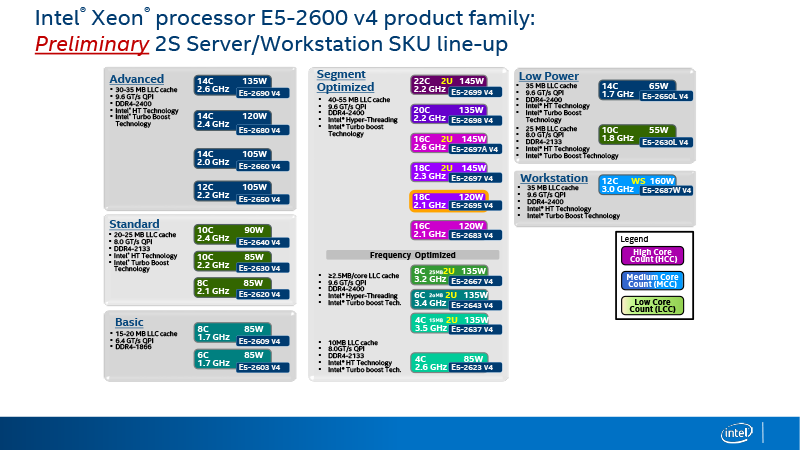

Сегодня на повестке дня – CPU Broadwell из линейки Xeon E5-2600 v4, предназначенные для рабочих станций и двухпроцессорных серверов. Новая линейка продуктов совместима с существующей платформой Intel C610, обслуживающей процессоры Haswell-EP, и на момент запуска включает 27 позиций с различным числом ядер и классом TDP: от 55 до 145 Вт для серверов плюс единственный CPU со спецификацией 160 Вт, предназначенный исключительно для рабочих станций – 12-ядерный E5-2687W v4.

Кремниевая пластина чипов Broadwell-EP

Поскольку архитектура Broadwell относится к фазе «тик» знаменитого маятника Intel, основная масса изменений в ядре Broadwell-EP связана с переходом техпроцесса с 22-нм к 14-нм нормам. Как следствие, Intel смогла увеличить количество ядер и объем LLC (кеш-памяти последнего уровня), оставаясь в рамках практически неизменной сетки TDP. Данные преимущества будут востребованы сборщиками серверов и рабочих станций широкого назначения, а также в HPC-индустрии (High Performance Computing), где замена процессоров Haswell-EP на Broadwell-EP принесет мгновенный рост соотношения быстродействия и мощности. Разочаровывающим моментом является то, что наряду с TDP не изменилась и максимальная частота, доступная Broadwell-EP, которая, как и у Haswell-EP, не превышает 3,6 ГГц в режиме Turbo.

⇡#Архитектура чипов Broadwell-EP

В целом аппаратные характеристики линейки Xeon E5-2600 изменились следующим образом. Количество доступных ядер в одном разъеме возросло с 18 до 22, объем LLC – с 45 до 55 Мбайт. Максимальная частота модулей памяти DDR4 SDRAM, с которыми официально совместимы процессоры, – с 2133 до 2400 МГц. Контроллер памяти Broadwell-EP также готов принять модули стандарта 3DS LRDIMM, несущие многослойные микросхемы DRAM (технология пока не вышла на рынок). Сборщики систем, требующих чрезвычайной надежности, могут воспользоваться поддержкой ECC на запись данных в модули DDR4 (весьма ресурсозатратной технологии, дополняющей стандартную для серверного сегмента коррекцию ошибок чтения из системной памяти).

Более подробный обзор мы начнем с логической структуры ядра Broadwell-EP, а затем коснемся оптимизаций конвейера в Broadwell по сравнению с предыдущей итерацией микроархитектуры Core и новых функциональных возможностей микропрограммы CPU.

Ядро Broadwell-EP производится в трех разновидностях, содержащих 10, 15 и 24 физических ядра x86 соответственно. Так как в линейке Xeon E5 v4 доступно только 22 ядра на разъем, то, как следствие, 24-ядерные конфигурации зарезервированы за линейкой Xeon E7 v4. Поскольку Xeon E7 и десктопные Core i7 для платформы LGA2011v3 будут основаны на тех же кристаллах, эти семейства CPU также получат обновление на Broadwell-E/Broadwell-EP в определенное производителем время.

Судя по данным о физических параметрах кристалла, за счет перехода от техпроцесса 22 нм к 14 нм Intel увеличила транзисторные бюджеты трех кристаллов Xeon на 22-30%, сократив их площади на 30,5-38%.

| Haswell-EP | Broadwell-EP | Изменение, % | |

|---|---|---|---|

| HLC (High Core Count) | |||

| Число транзисторов, млрд | 5,56 | 7,2 | 29,50 |

| Площадь кристалла, мм2 | 662 | 456 | -31,11782477 |

| Число физических ядер | 18 | 22 | 22,22 |

| MLC (Medium Core Count) | |||

| Число транзисторов, млрд | 3,84 | 4,7 | 22,40 |

| Площадь кристалла, мм2 | 492 | 306 | -37,80 |

| Число физических ядер | 12 | 15 | 25,00 |

| LLC (Low Core Count) | |||

| Число транзисторов, млрд | 2,6 | 3,2 | 23,08 |

| Площадь кристалла, мм2 | 354 | 246 | -30,51 |

| Число физических ядер | 8 | 10 | 25,00 |

|

Физические характеристики ядер Broadwell-EP |

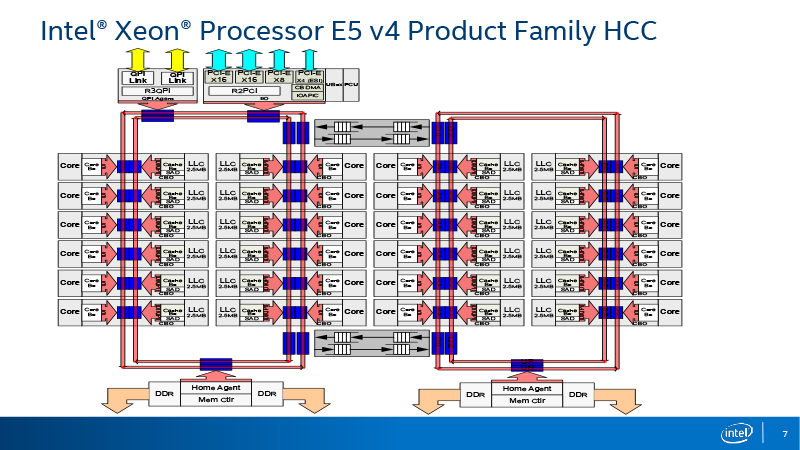

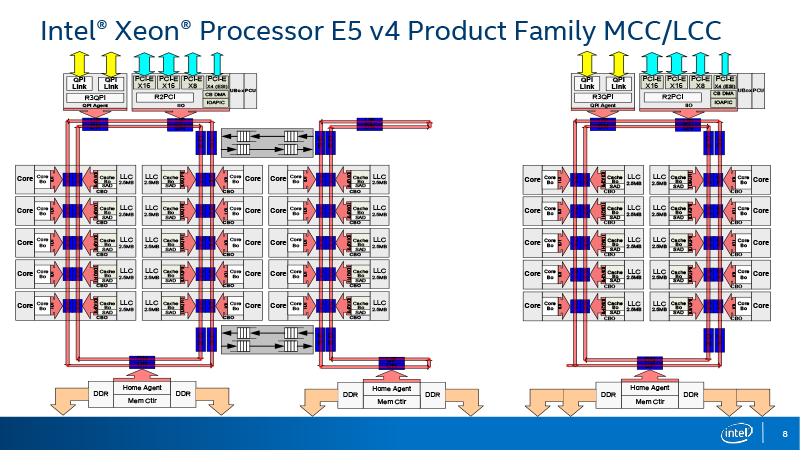

В общем виде структура процессора повторяет то, что мы видели ранее в ядре Haswell-EP. Начиная с архитектуры Sandy Bridge, Intel использует кольцевую шину для коммуникации между отдельными ядрами, оснащенными собственными сегментами кеша третьего уровня. В кристаллах MCC (Medium Core Count) и HCC (High Core Count) используются две кольцевые шины, разбивающие ядра на два COD (Cluster on Die). Конфигурация COD передается операционной системе с тем, чтобы транзакции происходили преимущественно между ядрами внутри кластера, не вызывая передачи через соединение колец, вызывающей дополнительную латентность.

На блок-схемах можно заметить, что каждый контроллер DRAM на чипах HCC и MCC обслуживает отдельный канал памяти, но в конфигурации LCC (Low Core Count) контроллеры несут двойную нагрузку. Как прокомментировал инженер Intel, значимого ущерба для производительности это не приносит.

⇡#Оптимизации конвейера, новые функциональные возможности

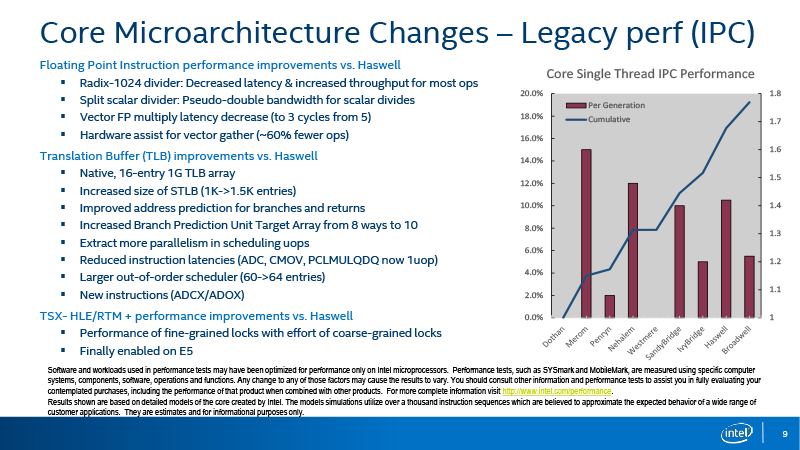

Несмотря на то, что Broadwell относится к фазе «тик», Intel не ограничилась экстенсивным развитием конфигурации ядра по сравнению с Haswell. Broadwell содержит список оптимизаций конвейера x86. Front-end чипа существенно усилен в плане внеочередного исполнения команд. Увеличена емкость вторичного буфера трансляции адресов (STLB), внеочередного планировщика, введена поддержка гигабайтных страниц, появился второй обработчик промахов, позволяющий просматривать страницы памяти параллельно, и т.д.

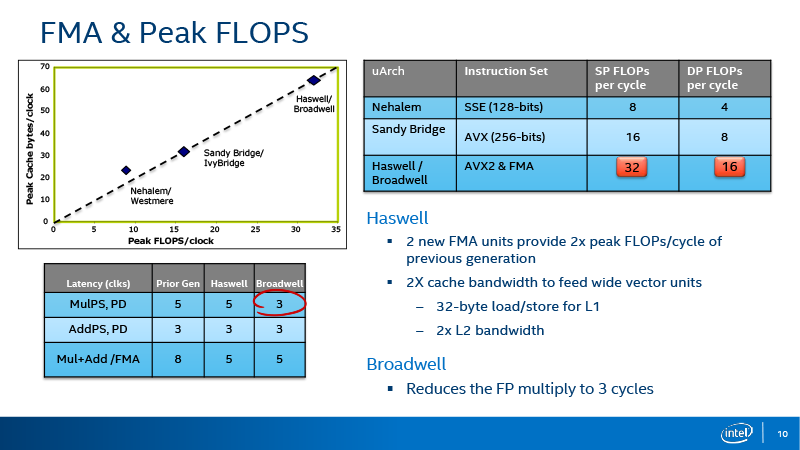

Изменения заметны и в исполнительных блоках чипа. Так, значительно снижена латентность умножения чисел с плавающей запятой (с 5 до 3 циклов), добавлен 10-битный делитель Radix-1024, снижающий латентность и увеличивающий пропускную способность в большинстве операций.

В сумме эти изменения обеспечивают прирост IPC (числа инструкций, исполняемых за такт) около 5% по сравнению с Haswell. При этом, как нам было известно ранее, в работе над Broadwell Intel установила отношение роста IPC к росту мощности 2:1. Теоретически мощность чипа при дополнительных 5% IPC должна увеличиться лишь на 2,5%.

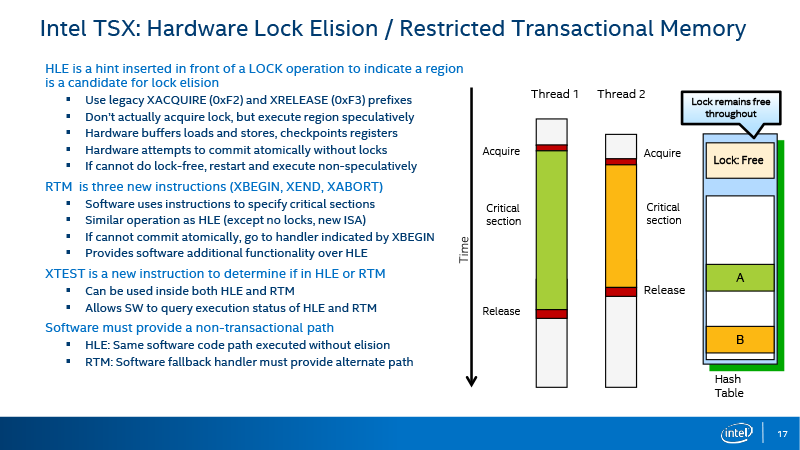

От оптимизаций широкого назначения мы перейдем к специфическим нововведениям, которое принесло ядро Broadwell-EP. Здесь наконец активирована поддержка набора инструкций Intel TSX, деактивированных в Haswell по причине обнаруженных в ядре аппаратных ошибок. TSX (Transactional Synchronization Extensions) вводит три новые инструкции, обеспечивающие работу т.н. транзакционной памяти. Не вдаваясь в подробности этого понятия, скажем только, что данная технология несет большой потенциал для исполнения многопоточных нагрузок, обращающихся с общими данными, обеспечивая повышенную производительность и энергоэффективность.

В области безопасности Broadwell Intel снизила латентность исполнения ряда инструкций, применяемых в криптографии, и ввела две новые инструкции ADCX/ADOX, а также расширила возможности встроенного генератора случайных чисел специальной инструкцией RDSEED, выдающей число для инициализации внешнего программного генератора ключей. Дополнительный механизм Supervisor Mode Access Prevention (SMAP) предотвращает исполнение кода из пользовательских страниц в режиме супервизора.

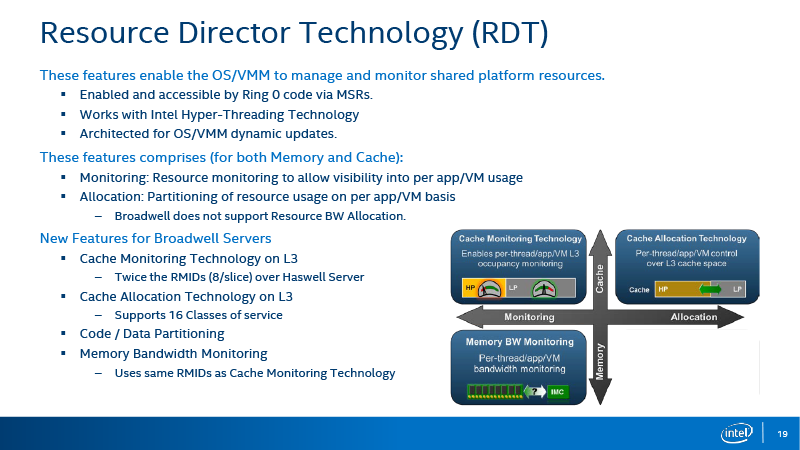

Огромный раздел документации на Broadwell-EP, предоставленной Intel, относится к оптимизации использования CPU в инфраструктуре с общими ресурсами: виртуальные машины, QoS (Quality of Service).

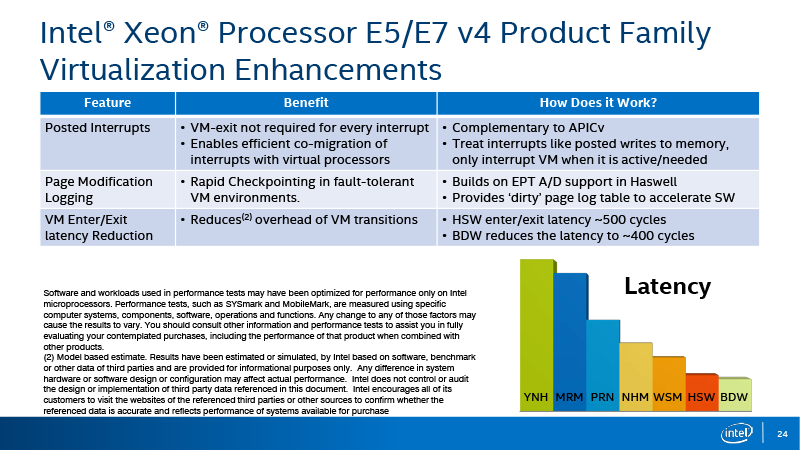

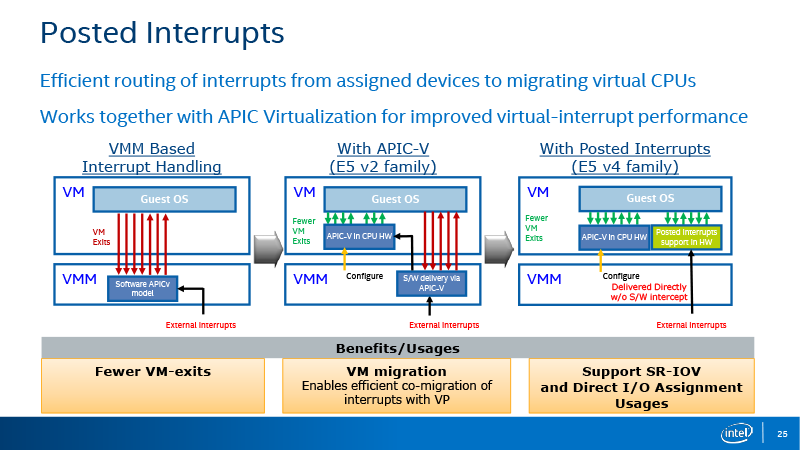

Представлен API под названием Resource Director Technology (RDT), обеспечивающий для отдельных потоков мониторинг и управление задействованными ресурсами кеша L3 и системной памяти. Среди прочего введена аппаратная поддержка отложенных прерываний (Posted Interrupts) для виртуальных машин, благодаря которой прерывания внешних устройств, назначенных отдельным ВМ, рассматриваются как отложенные вызовы на запись в память и не требуют вмешательства гипервизора.

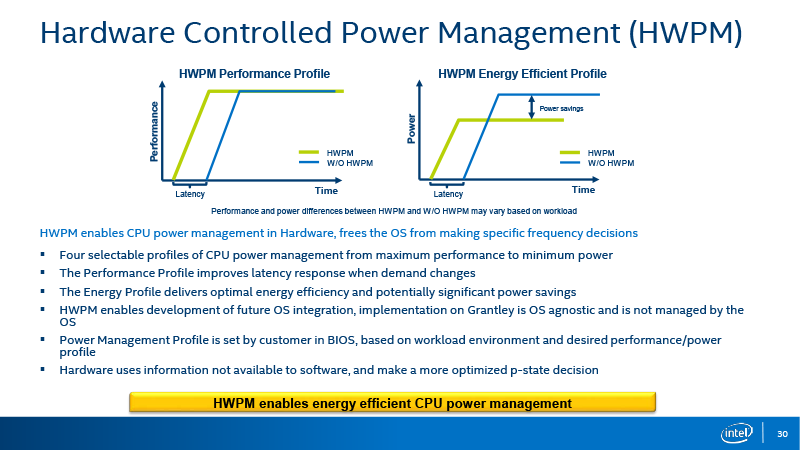

Intel продолжает развивать механизмы, направленные на повышение производительности на ватт путем более изощрённого управления частотой и напряжением питания ядер.

Говоря о мобильных применениях Broadwell, Intel отмечала, что процессор имеет возможность более самостоятельно переключать состояния мощности (P-states), основываясь на своих внутренних данных, недоступных работающим на нем программам, без необходимости ждать команды от ОС. Этот подход нашел применение и в серверной реализации Broadwell. Про Broadwell также известно, что он позволяет более эффективно отключать части ядра, не выполняющие полезную работу (Power Gating).

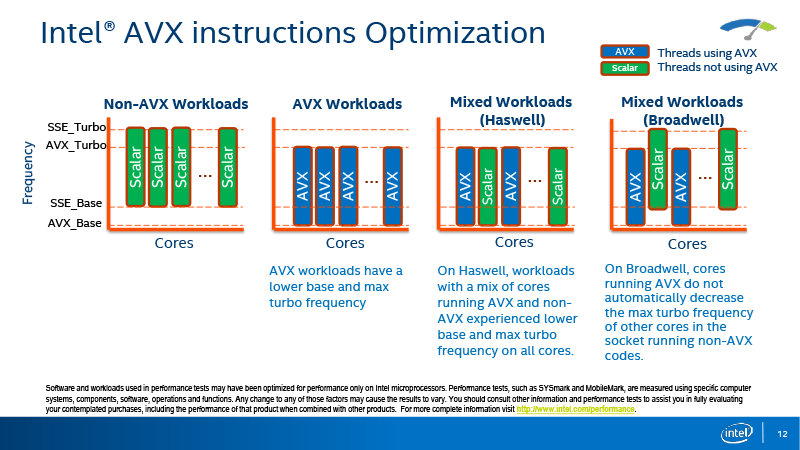

В дополнение к этому процессор теперь по-другому управляет частотой ядер в смешанной нагрузке, состоящей из скалярных вычислений и инструкций AVX. В то время как в Haswell требовалось снижать частоту всех ядер, если некоторые из них заняты AVX, то в случае с Broadwell присутствие AVX не влияет на рабочую частоту других ядер.

В данный момент мы не имеем возможности измерить быстродействие новых Xeon в целевых серверных приложениях, поэтому будем опираться на данные, предоставленные самими разработчиками и партнерами Intel, использующими ее продукты. В зависимости от того, насколько конкретная задача полагается на перечисленные оптимизации и дополнительные физические ядра, старший представитель линейки Xeon E5 v4 показывает прирост производительности от 8 до 44% по сравнению с топовым Xeon E5 v3 на ядре Haswell-EP.

В завершение обзора скажем, что хотя в данной итерации микроархитектуры Core серверный сегмент не получил такого же щедрого прироста количества ядер, каким он наслаждался в прошлые годы начиная с Xeon на базе архитектуры Nehalem, да и потолок тактовой частоты не сдвинулся по сравнению с таковым у ядра Haswell-EP, замедление темпов прогресса в данном случае вполне ожидаемо и оправдано колоссальной сложностью освоения все более тонких технологических норм. Кроме того, Intel провела большую работу по оптимизации работы CPU в таких ключевых задачах, как виртуализация, и ввела дополнительные функции, обеспечивающее более эффективное использование того количества ядер, которыми располагает процессор на данный момент. В итоге это не только обосновывает апгрейд существующей инфраструктуры для предприятий, использующих CPU класса Sandy Bridge-EP и более старые, но и делает Broadwell-EP оправданной заменой Haswell-EP в задачах, которые могут извлечь пользу из представленных в нем нововедений.

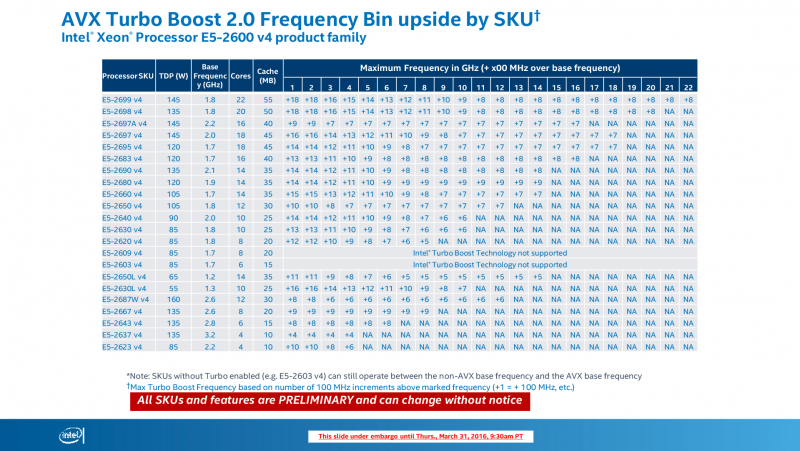

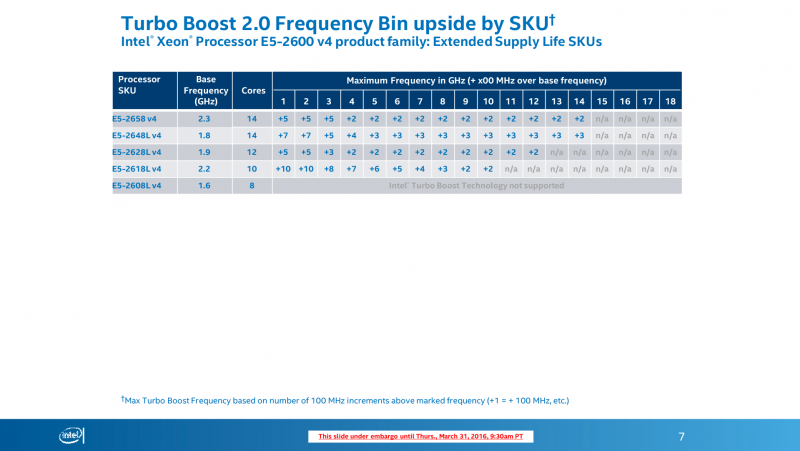

Тактовые частоты процессоров семейства Xeon E5-2600 v4

В заключение приводим таблицу частотных спецификаций представителей линейки Xeon E5-2600 v4.