TSMC выпустила первый чип по улучшенному 3-нм техпроцессу N3E, но до массового производства ещё далеко

Разработчик полупроводниковых микросхем Alphawave сообщил, что выпустил первый в индустрии опытный образец чипа с использованием улучшенного 3-нм технологического процесса N3E от компании TSMC. Отмечается, что тестовый образец успешно прошёл все необходимые тесты.

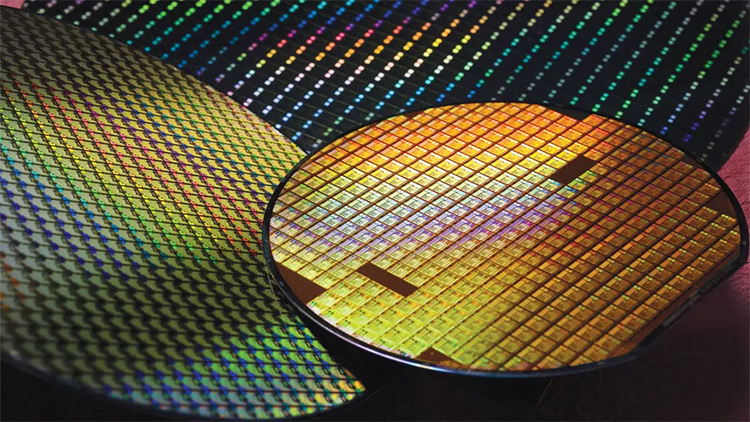

Источник изображения: TSMC

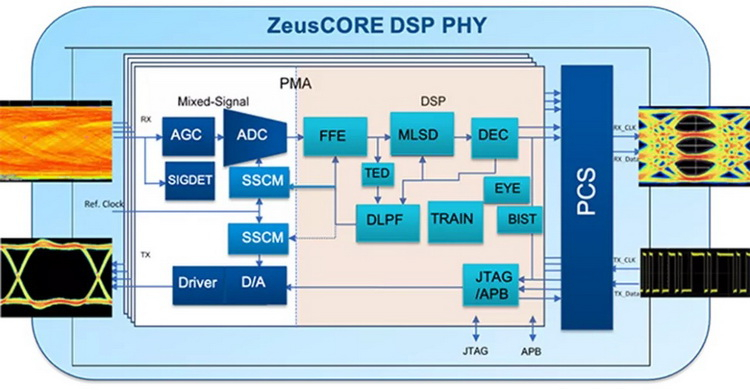

Для Alphawave выпустили образец чипа ZeusCORE100 1-112Gbps NRZ/PAM4 Serialiser-Deserialiser (SerDes), представляющий собой пару функциональных блоков, обычно используемых в высокоскоростной связи, для преобразования данных между последовательным и параллельным интерфейсами в обоих направлениях. Отмечается, что он поддерживает различные новые стандарты интерфейсов, включая 800G Ethernet, OIF 112G-CEI, PCIe 6.0 и CXL3.0. Подобные чипы в основном применяются для коммуникаций в серверных системах.

Источник изображения: Alphawave IP

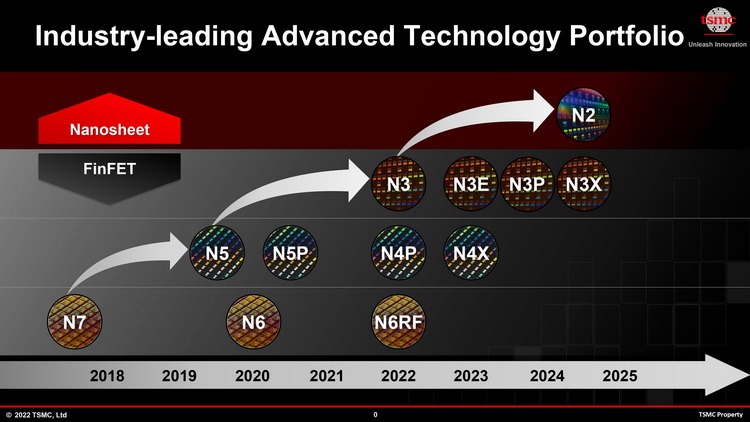

TSMC планирует представить пять вариаций 3-нм техпроцесса в течение двух–трёх лет. Обычная версия техпроцесса N3 будет использоваться ведущими клиентами контрактного производителя чипов, например, той же Apple. С вводом второго поколения 3-нм техпроцесса (N3E) планируется ускорить, а также увеличить объёмы выпуска микросхем, повысить уровень их производительности и энергоэффективности.

Источник изображения: TSMC

Ожидается, что чипы на базе усовершенствованного 3-нм техпроцесса N3E получат более широкое использование по сравнению с микросхемами на базе стандартного техпроцесса N3, однако старт массового выпуска чипов на основе техпроцесса N3E ожидается не ранее середины 2023 года, то есть примерно спустя год после начала массового производства чипов согласно нормам N3.

После перехода к массовому производству чипов по нормам N3E компания TSMC планирует перейти к выпуску микросхем на техпроцессах N3P и N3S, которые будут представлять собой варианты оптимизации N3E под различные классы применений. N3P ориентируется на высокопроизводительные чипы, а N3S — на энергоэффективные чипы с повышенной плотностью транзисторов. Оба техпроцесса запланированы на 2024 год. К 2025 году, когда компания начнёт осваивать следующую ступень полупроводниковых норм, появится ещё один техпроцесс 3-нм класса — N3X. На его базе будут выпускаться высокопроизводительные процессоры, для которых важно использование высоких рабочих токов и длительная работа на повышенных тактовых частотах.