Intel собрала гигантский ИИ-чип из 16 вычислительных кристаллов и 24 стеков HBM5

Intel первой разработала явно дезагрегированную чиплетную архитектуру — серверные GPU Ponte Vecchio для приложений ИИ и высокопроизводительных вычислений состояли из 47 чиплетов. Этот продукт до сих пор удерживает рекорд по количеству элементов в многослойной архитектуре, но Intel Foundry планирует нечто гораздо более экстремальное: многочиплетный корпус, объединяющий не менее 16 вычислительных элементов на восьми базовых кристаллах и 24 стека памяти HBM5.

Источник изображений: Intel

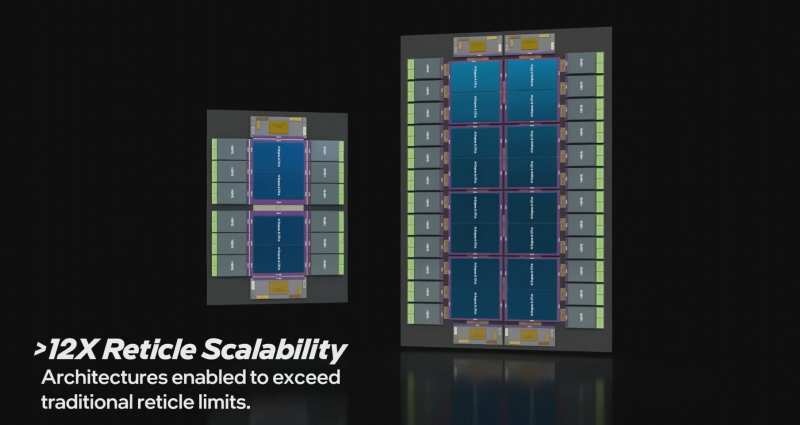

Предполагается, что такая конструкция будет иметь возможность 12-кратного масштабирования до самых больших чипов для ИИ на рынке (12-кратный размер фотошаблона, превосходящий 9,5-кратный размер фотошаблона TSMC).

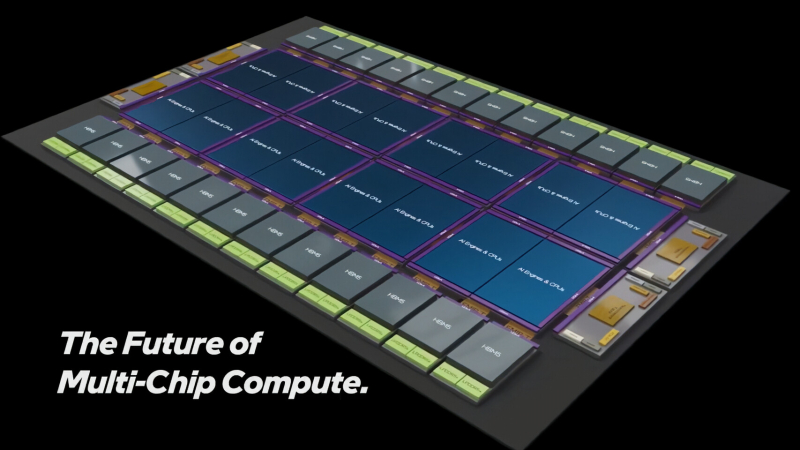

Концептуальный многочиплетный корпус Intel 2.5D/3D демонстрирует 16 больших вычислительных элементов (движков искусственного интеллекта или процессоров), изготовленных по технологическому процессу Intel 14A или даже более сложному 14A-E (1,4 нм, расширенные возможности, транзисторы RibbonFET 2 второго поколения с круговым затвором, улучшенная система питания PowerVia Direct с обратной стороны). Вычислительные элементы расположены поверх восьми (предположительно, размером с фотошаблон) базовых вычислительных кристаллов, изготовленных по техпроцессу 18A-PT (1,8 нм, повышенная производительность за счёт сквозных кремниевых соединений TSV и системы питания с обратной стороны), которые могут либо выполнять дополнительную вычислительную работу, либо содержать большой объём кэш-памяти SRAM для «основных» вычислительных кристаллов, как показано в примере Intel.

Базовые кристаллы в такой конструкции соединены с вычислительными блоками с помощью передовой технологии упаковки Foveros Direct 3D, использующей сверхплотное гибридное соединение медных контактов толщиной менее 10 мкм для обеспечения максимальной пропускной способности и энергоэффективности верхних кристаллов.

Базовые кристаллы используют EMIB-T (улучшенная версия Embedded Multi-Die Interconnect Bridge с TSV), а сверху — UCIe-A для боковых (2.5D) межсоединений между собой и с кристаллами ввода-вывода, изготовленными по технологии 18A-P (1,8 нм, с улучшенной производительностью), а также с изготовленными по заказу того или иного клиента базовыми кристаллами, что позволяет разместить до 24 стеков памяти HBM5.

Примечательно, что Intel предлагает использовать EMIB-T с интерфейсом UCIe-A для подключения специализированных модулей HBM5, а не стеки HBM5 стандарта JEDEC с традиционным отраслевым интерфейсом, что, возможно, призвано повысить производительность и ёмкость. Учитывая концептуальный характер разработки, использование специализированных стеков HBM5 не является обязательным требованием проектирования. Это лишь способ показать, что Intel также может интегрировать такие чипы.

Весь пакет также может поддерживать PCIe 7.0, интерфейс 224G SerDes, некогерентные коммутационные сети, содержать оптические модули и собственные ускорители для таких задач, как безопасность, а также память LPDDR5X для увеличения ёмкости DRAM.

Intel Foundry продемонстрировала два концепта: «среднего масштаба» с четырьмя вычислительными блоками и 12 модулями HBM и «экстремальный» — с 16 блоками и 24 стеками HBM5, о котором говорится в данной заметке. Даже конструкция среднего масштаба достаточно продвинута по сегодняшним стандартам, и Intel может производить её уже сегодня.

Что касается экстремального варианта, он может появиться к концу десятилетия, когда Intel усовершенствует не только технологию 3D-упаковки Foveros Direct, но и свои производственные узлы 18A и 14A. Возможность производить такие корпуса чипов экстремального размера к концу десятилетия поставит Intel на один уровень с TSMC, которая планирует нечто подобное и даже ожидает, что по крайней мере некоторые клиенты будут использовать её решения для интеграции компонентов размером с целую кремниевую пластину примерно в 2027–2028 годах.