ИИ-ускорители упёрлись в предел скорости HBM, и эта проблема пострашнее дефицита памяти

По оценкам представителей отрасли, современные ИИ-ускорители в своём развитии достигли того этапа, когда пропускная способность интерфейса памяти становится узким местом на пути дальнейшего масштабирования быстродействия. Дефицит памяти или её объём в этом отношении уходят на второй план, и устранение этого барьера главным образом зависит от разработчиков GPU и больших языковых моделей.

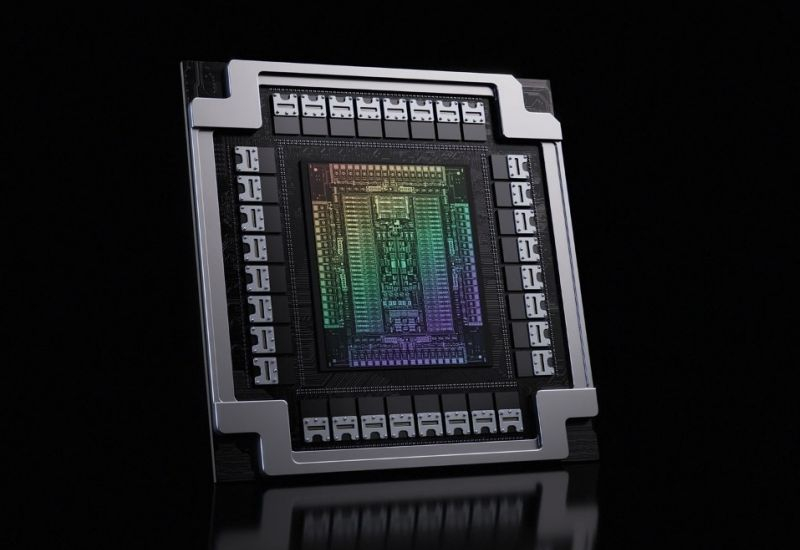

Источник изображения: Nvidia

По словам сооснователя Majestic Labs Ша Рабии (Sha Rabii), на которого ссылается CNBC, если непосредственно ускорители вычислений в последние годы продвинулись в своём быстродействии весьма значительно, сопутствующая им память стала не особо быстрее. По сути, именно производительность памяти ограничивает сейчас дальнейший рост быстродействия больших языковых моделей. При этом переход к инференсу увеличит потребности в объёме памяти, так что спрос на неё будет расти очень быстро. В любом случае, чем больше в инфраструктуре ИИ памяти, тем большее количество клиентов она способна обслуживать в единицу времени. О необходимости наращивать объёмы выпуска памяти на CES 2026 говорил и основатель Nvidia Дженсен Хуанг (Jensen Huang). Он даже отметил, что покупатели игровых решений компании типа видеокарт и консолей «обижены» на отрасль ИИ, поскольку дефицит памяти толкает цены вверх даже в указанных смежных сегментах рынка.

Даже запланированный AMD и Nvidia переход на использование памяти типа HBM4 не позволит полностью решить проблему пропускной способности. Память этого семейства всё равно ограничена в количестве задействованных каналов и высоте стека микросхем, не говоря уже о ширине интерфейса. Пропускная способность вычислительных систем могла бы масштабироваться гораздо эффективнее, если бы не свойственные HBM ограничения. Наращивать количество вычислительных блоков в составе GPU в таких условиях не имеет особого смысла, ибо память не будет успевать передавать все данные при вычислительных нагрузках, имеющих отношение как к обучению больших языковых моделей, так и инференсу.

Доступные разработчикам компонентов методы упаковки чипов также выступают в роли специфического ограничивающего фактора, в условиях высокого спроса профильные мощности сильно загружены, усиливая дефицит скоростной памяти и повышая расходы производителей.

На архитектурном уровне разработчики пытаются изучать альтернативы типа осуществления вычислений прямо внутри микросхем памяти (PIM), увеличения плотности компоновки микросхем в составе стека памяти, а также применения в многокристальных решениях прогрессивных интерфейсов типа UCIe, которые позволяют не только увеличить эффективную полосу пропускания, но и снизить задержки при работе с данными. Темпы дальнейшего масштабирования инфраструктуры ИИ будут зависеть от прогресса в сфере внедрения более скоростной памяти.

HBM4 предложит прирост быстродействия в полтора раза относительно HBM3E, позволяя через свою более широкую 2048-разрядную шину передавать до 2 терабайт данных в секунду. К 2027 году на арену выйдет память типа HBM4E, которая потенциально увеличить скорость передачи информации ещё в полтора раза. Внедрение интерфейса CXL также должно способствовать повышению эффективности обмена данными между компонентами вычислительных систем. В части памяти переход к CXL обеспечит увеличение степени загрузки на 50 %, а также снижение энергопотребления на величину до 20–30 %. Появление новых методов трёхмерной компоновки памяти тоже должно способствовать повышению производительности и снижению энергопотребления.