Intel заменит AVX-512 на AVX10 — набор инструкций, который сможет работать везде

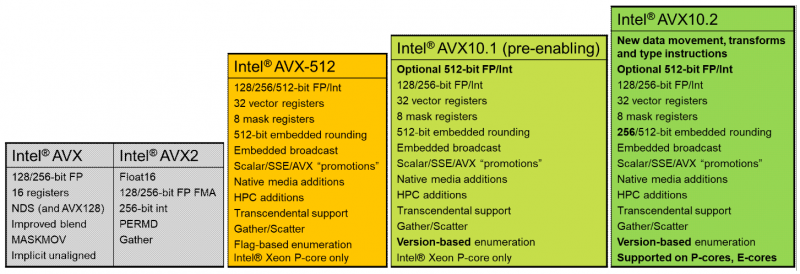

Вместе с расширениями архитектуры APX, компания Intel представила сегодня новый набор команд AVX10 (Advanced Vector Extensions 10). Он является дальнейшим развитием AVX-512 и будет поддерживаться в перспективных гибридных процессорах не только производительными, но и энергоэффективными ядрами.

Основная цель внедрения AVX10 — подведение векторных инструкций, которые могут выполняться разными типами ядер Intel, под единый стандарт. Актуальный набор векторных инструкций AVX-512 позволяет работать с 512-битными операндами, однако поддерживается исключительно большими P-ядрами. Маленькие E-ядра имеют лишь 256-битные регистры, поэтому AVX-512 в них не работает. Это приводит к тому, что в гибридных процессорах вроде Alder Lake или Raptor Lake поддержку AVX-512 приходится отключать.

Набор AVX10 должен решить эту проблему, однако несколько своеобразным способом. Регистры шириной 512 бит в E-ядрах не появятся, но он позволит выполнять одни и те же векторные инструкции набора AVX-512 как P-, так и E-ядрами, но применительно к регистрам разной размерности: в первом случае – 512, а во втором — 256 бит. Вопрос совместимости результатов операций Intel собирается решить добавлением в AVX10 флага размерности AVX512VL и специальных 256-битных инструкций со встроенным округлением.

По утверждению Intel, все имеющиеся программы с поддержкой AVX-512 сохранят работоспособность и тот же уровень производительности при исполнении на ядрах с поддержкой 512-битных регистров и инструкций AVX10. Однако перекомпиляция под AVX10 программ, использующих набор AVX2, позволит получить прирост производительности за счёт задействования более эффективных команд и дополнительных 16 регистров. Кроме того, общая производительность программ, использующих AVX10, при их исполнении на гибридных процессорах, будет выше за счёт того, что часть нагрузки сможет перенаправляться на E-ядра.

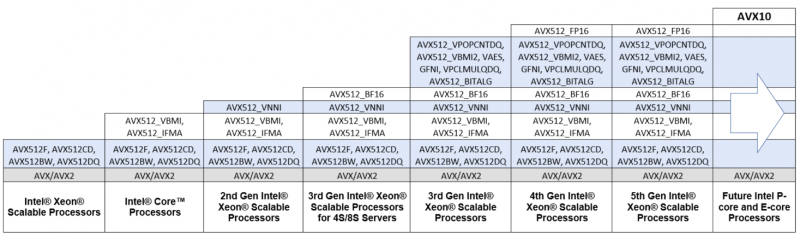

Первая версия AVX10, обозначенная в документации Intel как AVX10.1, появится в серверных процессорах Granite Rapids, которые должны выйти в 2024 году. Однако в них работа с 256-битными регистрами реализована пока не будет, а совместимость с AVX10 будет обеспечиваться лишь на уровне P-ядер. Иными словами, речь идёт лишь о первом переходном этапе к внедрению нового набора. Полноценная же реализация AVX10 в виде версии AVX10.2, работающей как с 512-, так и с 256-битными регистрами, намечена на более поздний срок.

С переходом на AVX10 дальнейшее развитие AVX-512 замораживается, а все вызовы 512-инструкций в перспективных процессорах будут происходить через AVX10. Что же касается ещё одного продвигаемого Intel набора команд, AMX (Advanced Matrix Extensions), то он сохранит свою актуальность и после перехода к AVX10.