TSMC будет выпускать основания для стеков HBM4 по 12- и 5-нм техпроцессам

Компания TSMC на конференции European Technology Symposium 2024 поделилась свежими деталями о ходе разработки чипов-оснований для высокопроизводительной памяти HBM4. Одной из ключевых особенностей новой технологии памяти станет переход с 1024-битного на 2048-битный интерфейс. Однако реализация этого потребует применения более передовых технологий упаковки, по сравнению с теми, что используются сейчас для производства и интеграции памяти HBM.

Источник изображения: TSMC

В рамках своей презентации TSMC поделилась свежими деталями о чипах, которые лягут в основание стеков памяти HBM4. Компания собирается использовать для выпуска базовых чипов сразу два своих техпроцесса — N12FFC+ (12 нм) и N5 (5 нм). Каждый обладает своими достоинствами, но оба будут служить одной цели — интеграции высокоскоростной памяти HBM четвёртого поколения в состав будущих ИИ- и HPC-процессоров.

«Мы сотрудничаем с ключевыми партнёрами в разработке HBM-памяти (Micron, Samsung, SK Hynix) над передовыми узлами для полной интеграции стека HBM4. Базовый кристалл на основе экономичного техпроцесса N12FFC+ обеспечит прирост производительности HBM4, а базовый кристалл на основе N5 позволит размещать больше логических компонентов на чипе и снизить энергопотребление памяти», — отмечает компания.

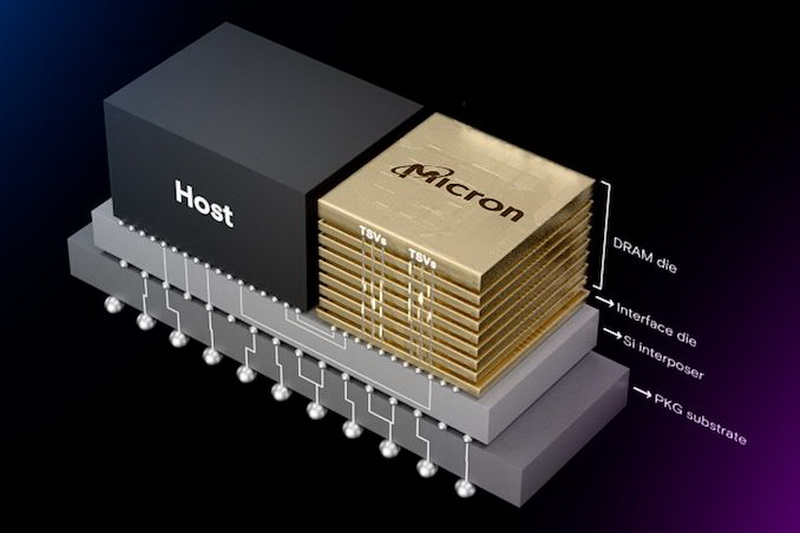

Базовый кристалл памяти HBM4, изготовленный по технологии TSMC N12FFC+ (12-нм FinFet Compact Plus), будет использоваться для установки стеков памяти HBM4 на кремниевый переходник рядом с SoC. В TSMC отмечают, что N12FFC+ позволяет создавать стеки памяти в конфигурациях 12-Hi (двенадцать ярусов, 48 Гбайт) и 16-Hi (шестнадцать ярусов, 64 Гбайт) с пропускной способностью каждого стека более 2 Тбайт/с.

Базовые кристаллы HBM4 на техпроцессе N12FFC+ будут применяться для производства «систем в корпусе» (system-in-package, SiP) с использованием передовых технологий упаковки TSMC CoWoS-L или CoWoS-R. По данным TSMC, в настоящее время HBM4 может достигать скорости передачи данных до 6 ГТ/с при токе 14 мА.

«Мы также оптимизируем свои технологии упаковки CoWoS-L и CoWoS-R для HBM4. Они подразумевают использование более восьми уровней интерконнекта, чтобы обеспечить маршрутизацию более чем 2000 соединений в составе HBM4 с должной целостностью сигнала», — сообщила TSMC

Компания TSMC сотрудничает с EDA-партнёрами Cadence, Synopsys и Ansys над вопросами обеспечения целостности передачи сигналов, тепловой точности и снижения электромагнитных помех (EMI) в новых базовых кристаллах HBM4.

В качестве более продвинутой альтернативы TSMC сможет предложить для своих клиентов техпроцесс N5 для производства оснований для стеков памяти HBM4. Этот узел позволит размещать в составе стека HBM4 ещё больше логических компонентов, снизить энергопотребление памяти и ещё сильнее повысить её производительность. Но, возможно, самым важным преимуществом N5 является то, что он позволяет добиться очень малого шага межсоединений в составе HBM4, порядка 6–9 микрон. В свою очередь это позволит интегрировать кристаллы памяти HBM4 прямо поверх логических микросхем. Это должно увеличить производительность и пропускную способность памяти, что окажется полезным при производстве ИИ-чипов.