JEDEC разрешит памяти HBM4E подрасти — ради упрощения производства и снижения цены

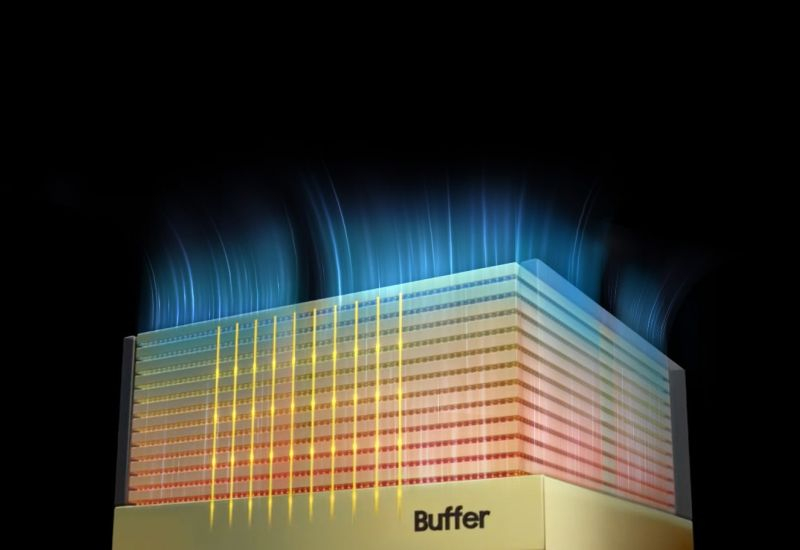

Формируемая несколькими слоями память типа HBM считается одной из самых быстрых на рынке, но она остаётся дорогой и сложной в производстве. По некоторым данным, стандартизирующий орган JEDEC готовит послабления в части требований к высоте стека HBM4E, чтобы облегчить жизнь и работу производителям памяти не только одноимённого поколения, но и последующих.

Источник изображения: Samsung Electronics

Об этом сообщает издание Business Korea, которое заодно напоминает, что действующим стандартом JEDEC определена максимальная высота стека HBM3E в размере 720 мкм, а для HBM4 задан предел в размере 775 мкм. Как ожидается, для HBM4E шаг увеличения размера окажется заметно больше, поскольку максимальная высота стека ограничится 900 мкм. Предполагается, что за счёт этого в стеке можно будет разместить больше ярусов и тем самым увеличить ёмкость одного стека памяти. Современные микросхемы HBM3E имеют до 12 ярусов, но производители памяти уже располагают образцами 16-ярусных чипов HBM3E и HBM4.

Кроме того, подобные послабления влекут целый ряд преимуществ. Во-первых, при производстве HBM следующих поколений можно будет сохранить технологию упаковки чипов в стеке — сейчас для этого применяется метод термокомпрессионного формирования связей, а перспективная технология гибридных связей пока не может применяться в массовом производстве из-за нестабильности качества продукции. Сохранив прежнее оборудование для производства новых типов памяти, можно будет не только сэкономить, но и не ограничивать объёмы выпуска продукции из-за нехватки новых типов оборудования.

Во-вторых, поскольку требования к сложности выпускаемых чипов HBM будут снижены, снизится уровень брака и объёмы годной продукции удастся увеличить, а затраты снизятся. Правда, у возможных послаблений находятся и свои противники. Южнокорейские производители типа Samsung и SK hynix уже сейчас выпускают продукцию, которая превосходит требования стандартов JEDEC. Если эти требования станут мягче, это позволит конкурентам проще проникать на рынок, особенно китайским.