⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Fall Processor Forum 2004: процессоры завтрашнего дня

Среди крупнейших всемирных индустриальных форумов, проводящихся ежегодно китами компьютерной индустрии, по пальцам одной руки можно пересчитать серьезные научно-технические конференции, действительно привносящие свежую струю информации о полупроводниках будущего. Все основные мероприятия, какими бы они ни были крупными и зрелищными, как правило, рассчитаны на зевак, журналистов и торговых партнеров, с которыми "за кулисами стендов" заключаются договора о поставке новинок. Серьезные технологические симпозиумы, как правило, проходят при закрытых дверях и рассчитаны больше на специалистов, чем на широкую публику. Между тем, внимательно разобравшись даже с усеченной информацией, попадающей в Сеть, можно с достаточной долей вероятности прогнозировать стратегические пути дальнейшего развития той или иной отрасли, что, как правило, подтверждается в ближайший год анонсами о появлении новинок в рознице.  Не исключение из этого списка - одна из наиболее серьезнейших мировых конференций, Fall Processor Forum (FPF, ранее - Microprocessor Forum), посвященная архитектурам процессоров и проводимая под эгидой аналитической компании In-Stat/MDR с участием и при активном содействии и спонсорстве большинства производителей, так или иначе связанных с процессорами. Можно отметить, что с некоторых пор разве что Intel не столь активно, как раньше, принимает участие в MPF. Оно и понятно - для популяризации свих разработок Intel уже приличное время проводит два раза в год свой собственный научно технический Форум для разработчиков - IDF, на котором, главным образом, и преподносятся ее процессорные новинки. Впрочем, Intel все равно будет присутствовать в этой статье - незримо, по аналогии с 3-спальной кроватью "Ленин всегда с нами" из старинного советского анекдота. Ибо как не крути, а сравнивать и даже противопоставлять варианты архитектур придется, не без этого. Остальные игроки процессорного рынка, как правило, если и не приурочивают к FPF анонс своих новых архитектур, тем не менее, не упускают возможности рассказать что-нибудь действительно новое. Передавая дух и настроения докладчиков на FPF 04 в виде отдельных зарисовок о докладах различных компаний, мне бы хотелось не только рассказать о наиболее свежих частных случаях архитектурных решений, но также передать общие тенденции индустрии. Как известно, с 4 по 6 октября "под одной крышей" были объединены сразу три конференции, считавшиеся ранее самостоятельными - Microprocessor Forum, Embedded Processor Forum и MEMS Executive Forum, главное внимание по праву занимали доклады на тему современных и перспективных архитектур производительных процессоров для настольных, мобильных и серверных систем. Сейчас ключевой тенденцией в этом секторе по праву называют переход от практики одноядерных универсальных архитектур к широкому внедрению специализированных, интегрированных на одном кристалле "систем в чипе" (System-on-Chip, SoC), а также к многоядерным дизайнам и поддержке многопоточных сценариев обработки данных. Второй особенностью активно разрабатываемых в настоящее время процессорных структур называют реализации поддержки дополнительных инструкций для ускорения производительности при выполнении специфических алгоритмов. То есть, говоря привычным языком, для выполнения Закона Мура индустрия вынуждена не только продолжать своеобразную "гонку по вертикали" в виде смены техпроцессов, но также увеличивать производительность за счет роста "горизонтальной" сложности архитектур и распараллеливания потоков данных. Таким образом, наряду с традиционными инвестициями в разработку новых архитектур и усовершенствование прежних многие компании в настоящее время вкладывают значительные деньги в "распихивание" нескольких процессорных ядер на один кристалл. Хорошо это или плохо - покажет лишь время, ибо даже если добиться наилучшего арбитража нескольких ядер и оптимального программное распараллеливания задач, нет никакой гарантии, что овчинка будет стоить выделки, и реальный прирост производительности станет просто смехотворен на фоне, простите, тупого увеличения тактовой частоты. В настоящее время эти вопросы интересуют любых разработчиков процессоров, будь то архитектуры ARM, IA-64/EPIC, MIPS, Power, SPARC, x86 или что-то нетрадиционное. Впрочем, пора закруглятся со вступлением и переходить к "изюминкам" нынешнего форума, благо, интересных вещей было представлено немало. Наиболее интересными презентациями FPF 04, на мой взгляд, стали следующие:

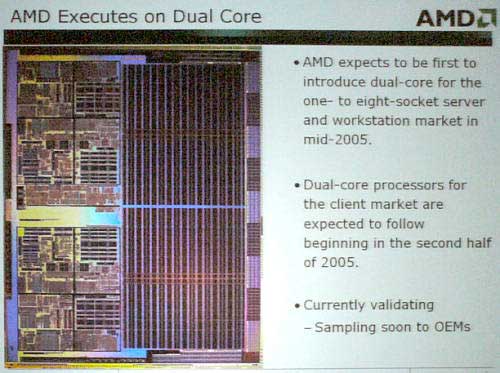

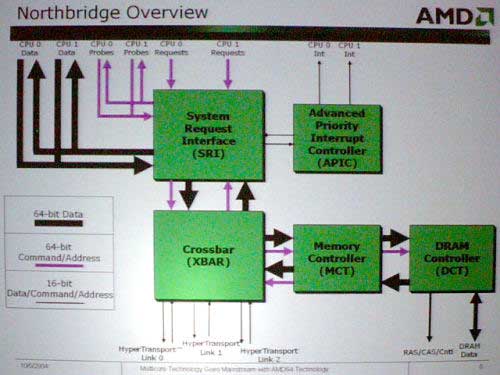

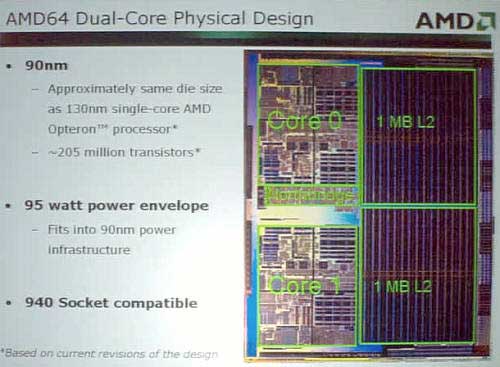

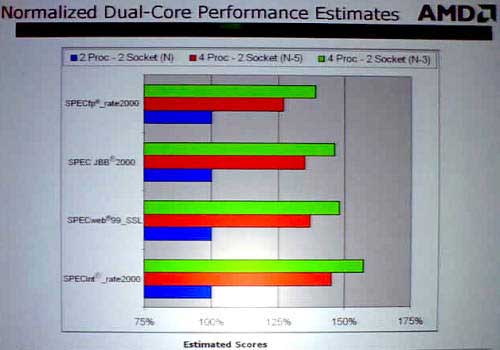

В этом материале отражены доклады, имеющие непосредственное отношение к архитектуре x86, хотя, на самом деле, в рамках форума FPF 04 было заслушано множество других, не менее интересных для специалистов материалов. Перечислю их через запятую (возможно, к рассказу о них мы еще вернемся - если не в отдельных материалах, то уж точно в рамках новостей): I/O процессоры PowerPC 440XX, новое поколение многоядерных SoC-процессоров SiByte от Broadcom, новые мультимедийные расширения процессорной архитектуры ARM, сигнальная обработка в архитектуре MIPS, интеграция процессоров SH-4 с AV/графическими ядрами, инструкции Virtex-4 FX в архитектуре PowerPC, а также многие другие темы. Теперь - подробно о самом интересном - версиях x86, которые в скором времени попадут в ноутбуки и настольные ПК. 2-процессорные AMD64: 205 млн. транзисторов на 95 ВтОтдадим должное AMD: чего бы там не показали и не рассказали о других архитектурах, идеи о выпуске 2-ядерных чипов Athlon 64/Opteron уже в следующем году будоражат сознание широкой публики почище заездов Формулы-1. В кои веки компания #2 по "десктопным" процессорам не следует послушно в кильватере лидера, но даже умудряется срезать острые углы, не вляпываться в некоторые тупички Intel, а в последнее время даже умудряется местами диктовать моду. Чем же таким будет интересен новый 2-ядерный чип AMD?  Как известно, впервые идею о выпуске двуядерного процессора специалисты AMD выдвинули еще пять лет назад. Проводивший презентацию AMD Кевин МакГрат с удовольствием показал собравшимся слайды с Microprocessor Forum 1999, где была изложена идея интегрированной многопроцессорности. Правда это или нет, но теперь утверждается, что еще на стадии начальной разработки архитектуры AMD K8 учитывалась возможность ее оптимизации под многоядерный дизайн с симметричной моделью многопроцессорного программирования (SMP, Symmetric Multiprocessing Programming). В качестве плюсов этой архитектуры для оптимизации под 2- и более ядерный дизайн представитель AMD подчеркнул достаточно короткий конвейер K8 - всего 12 стадий для целочисленной арифметики, а также интегрированные в чип функционалов северного моста, что якобы также упрощает переход к многоядерности.  Впрочем, наиболее интересным оказалось заявление представителей о прогнозируемой производительности 2-ядерных чипов Opteron. А она будет превышать возможности нынешних одноядерных чипов на 25 - 50% при меньшей тактовой частоте! Увы, снижение тактовых частот является обязательным условием для баланса производительности и температурного режима чипа. По крайней мере, на первых порах высоких тактовых частот ждать не стоит. М-р МакГрат заявил о том, что первые 2-ядерные чипы Opteron будут иметь тактовые частоты, примерно на 600 - 1000 МГц меньшие, нежели их одноядерные варианты.  Увеличение производительности двуядерных процессоров AMD завязано на реализацию новой архитектуры - AMD Direct Connect Architecture, где ядра, грубо говоря, почти "напрямую" подключаются к периферии и системной обвязке, что уменьшает количество узких мест и всевозможные задержки. Процессорные ядра работают в сочетании с комбинированным интерфейсом системных запросов (SRI, system request interface) и коммутатором, подключающим общий модуль северного моста, состоящий в свою очередь, из трех шин HyperTransport и двухканального 128-битного интерфейса памяти DDR.  Как известно, нынешний 0,13 мкм Opteron имеет площадь кристалла 194 мм кв. По уточненным данным, AMD намерена разместить два ядра поколения K8 примерно на той же площади кристалла, правда, уже с нормами производства 90 нм и применением технологии SOI (Silicon-on-Insulator). Взамен 106 млн. транзисторов у нынешнего чипа Opteron, 2-ядерный дизайн будет составлен из 205 млн. транзисторов. Каждое ядро нового процессора будет обладать 1 Мб собственной скоростной кэш-памяти. При этом, по словам представителей компании, два ядра будут выделять столько же тепла, сколько один нынешний, то есть, TDP (Thermal Design Power) 2-ядерного чипа Opteron останется в рамках 95 Вт, а это значит, что новые процессоры впишутся в уже существующие серверные форм-факторы без каких-либо изменений последних. Что бы там не случилось с цоколевкой новых процессоров для настольных ПК, AMD намерена выпустить 2-ядерные Opteron под тот же разъем Socket 940. Можно без сомнений говорить о том, что первые 2-ядерные чипы Opteron будут поддерживать память DDR первого поколения, это уточнение прозвучало от Кевина МакГрата во время кулуарных дискуссий в рамках FPF. В рамках конференции AMD также подтвердила свой предварительный план по выпуску новых 2-ядерных процессоров. Как известно, в настоящее время компания уже имеет "на руках" образцы 2-ядерных чипов, в самое ближайшее время ожидается начало поставок опытных образцов OEM-партнерам, а массовый переход на серийные серверные процессоры Opteron ожидается на протяжении 2005 года. Что касается 2-ядерного варианта для настольных ПК - обновленного Athlon 64 FX (ядро Toledo, в отличие от нового одноядерного Athlon 64 FX с ядром San Diego), появление первых чипов запланировано на вторую половину 2005 года.  Очень интересные цифры были продемонстрированы представителями AMD во время презентации. Точными данными или результатами тестов это назвать нельзя, сам график так и подписан - "ожидаемая производительность". Как видно на иллюстрации по бенчмаркам SPECfp/SPECint/SPEC JBB/SPECweb, если в том же синтетическом тесте SPECfp_rate2000 (арифметика с плавающей запятой) производительность системы на двух одноядерных процессорах принята за 100%, то система на двух 2-ядерных процессорах с рейтингом N-5 имеет производительность более 125%, а показатели такой же системы с рейтингом N-3 составляют порядка 140%. В целочисленной арифметике (SPECint_rate2000) показатели еще выше - более 140% и более 150% соответственно. Представители AMD так и не растолковали систему своих новых рейтинговых оценок реальной тактовой частоты 2-ядерных чипов, однако, если мы решим принять тактовую частоту одноядерного чипа за 2,4 ГГц, двуядерного N-3 за 2,1 ГГц, а такого же N-5 за 1,9 ГГц, то в принципе, такой расклад становится более-менее понятен. Впрочем, наивно полагать, что все закончится механическим "склеиванием" двух ядер Opteron. На деле, новые чипы будут обладать целым рядом новых достоинств, среди которых уже точно названы следующие:

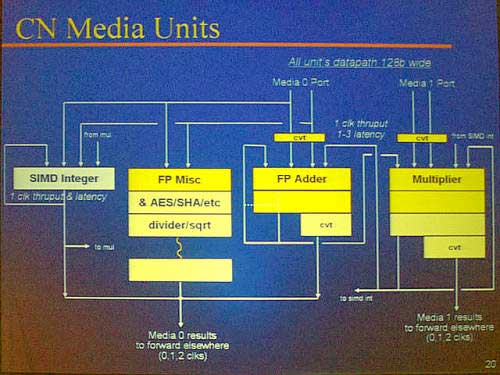

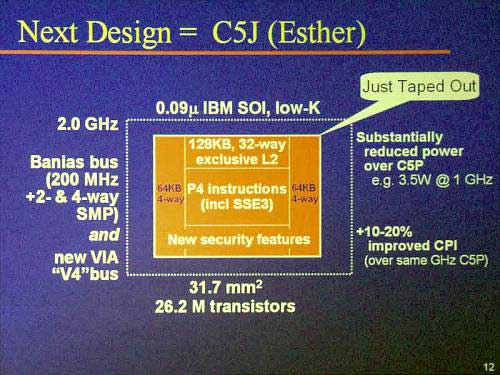

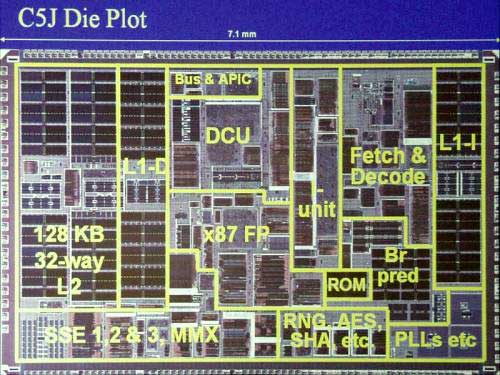

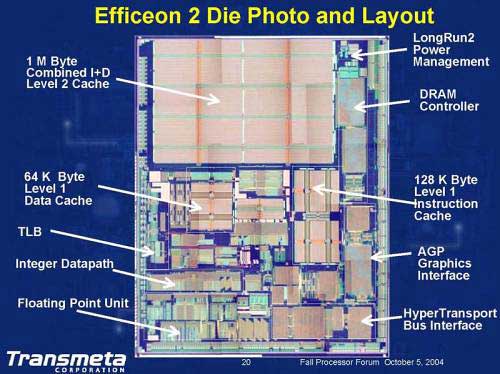

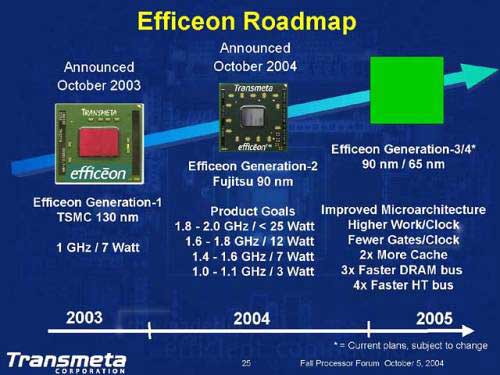

В заключение краткого обзора выступления AMD на форуме FPF 04 нельзя не упомянуть о планах компании. Вот какие задачи в плане усовершенствования архитектуры K8 ставят перед собой инженеры AMD на ближайшее будущее: 1. Более одного чипа на кристалл Такие дела. На этом, пожалуй, рассказ про выступление AMD можно закончить. В качестве основной "морали" 2-ядерной стратегии AMD, пожалуй, можно выдать следующий тезис: IBM была первой со своими 2-ядерными чипами Power4 в 2001 году, HP и Sun представили свои варианты 2-ядерных решений в году нынешнем, но AMD хотела бы стать первым производителем, который запустит такие процессоры на рынок x86 серверов. Что ж, время покажет... Isaiah: новый процессорный пророк от VIA в 64-битных одеждахКомпания VIA Technologies в лице Гленна Генри (Glenn Henry), президента процессорного подразделения Centaur Technology приняла участие с докладами о своих новых разработках сразу в двух форматах - для настольных и встраиваемых систем. Поскольку обе новинки выполнены на базе архитектуры x86, каждая из них заслуживает упоминания в этом материале.  Наиболее интересным был рассказ о новой 64-битной архитектуре ядра Isaiah, получившего кодовое инженерное название CN. Как видите, череда пророков в виде ядер Ezra, Samuel и Nehemiah (Эзра, Самуил, Неемия) продолжается в еще одном - Isaiah (Исайя). Появление нового ядра в кремнии ожидается не ранее первой половины 2006 года, поэтому рассказ о его возможностях был весьма сжат, подробности последуют значительно позже. Новый чип Isaiah сочетает в себе реально производительную out-of-order суперскалярную 64-битную архитектуру с экономичным дизайном и встроенными аппаратными средствами безопасности. Чип позиционируется не только в качестве процессора для ПК, но как центральный элемент самых разнообразных электронных устройств для работы с цифровым медиа-контентом и поддержкой вывода изображения с разрешением HDTV. Помимо 64-битной архитектуры, суперскалярное ядро Isaiah интересно поддержкой системной шины с высокой тактовой частотой, наличием оптимизированного и наконец-то доведенного до ума 128-битного FPU, поддержкой дополнительных инструкций SSE, увеличенным размером кэша L2. Известная система аппаратной защиты VIA PadLock Hardware Security Suite будет доработана и реализована в ядре Isaiah с улучшенными алгоритмами работы. 64-битная суть нового ядра CN выражена в поддержке расширенного набора инструкций x86 - AMD64 (или, если хотите, EM64T). Взамен шины Pentium 3, унаследованной от "совместимого" дизайна своих предшественников, Isaiah будет поддерживать так называемую "шину Via". Уже точно известно, что ядро CN будет обладать интегрированным контроллером памяти, однако, представители компании наотрез отказались комментировать, какая же память будет поддерживаться. В кратком рассказе о ядре Isaiah не были упомянуты ни ожидаемые тактовые частоты новых чипов, ни техпроцесс, ни какие-либо более-менее существенные подробности об архитектуре. Ничего пока не известно о длине конвейера нового чипа, хотя, возможно, она останется той же, что у современного чипа Nehamiah с его 17 стадиями. Интересно упомянуть, что VIA также интересуется многоядерными архитектурами чипов, однако, не ставит их во главу угла своей стратегии. Скорее всего, многоядерные процессоры компании будут базироваться на ее стандартных процессорных "производных" в качестве интересного, но необязательного дополнения к одноядерным предложениям.  Что касается другой новинки компании - ядра VIA C5J, здесь гораздо меньше тумана. Правда, представлено оно было в рамках совмещенной с основным форумом конференции Embedded Processor Forum, что ясно указывает на позиционирование нового чипа. Новый процессор ведет свою "родословную" от базовой разработки VIA C3. На прошлом MPF компания VIA представила свое ядро Nehemiah, носящее также рабочее название C5P. В первом квартале нынешнего года появились упоминания о получении первых образцов ядра C5I, ранее фигурировавшего как C5XL и получившего давным-давно название Esther (то бишь, "Эсфирь". Не сумлевайтесь, источник названий тот же - Ветхий Завет). Наконец, в дни FPF 04 ядро Esther благополучно обзавелось названием C5J, под которым и было представлено. Впрочем, незадолго до начала FPF 04 компания VIA также объявила официальную торговую марку, под которой ядро C5J будет представлено на рынке - C7 для стандартных систем и C7-M - для мобильных вариантов. Базовые характеристики ядра Esther весьма схожи с Nehemiah, однако, изменения произошли все же существенные. Например, 64 Кб 16-ходового кэша L2 превратились в 128 Кб 32-ходового кэша L2, появилась полная поддержка наборов инструкций SSE2/SSE3, бита NX (No Execution), новой шины V4 (если кто-то не понял что это, шепотом намекну - AGTL+). Тактовая частота чипа поднята до 1,5 ГГц с прицелом на достижение 2 ГГц при уменьшенном энергопотреблении. Однако, на мой взгляд, самый интересный фокус - это появление архитектуры SMP с поддержкой до 4 процессоров! Ничего не скажешь, хороший прогресс!  Площадь кристалла процессорного ядра C5J составляет 31,7 мм кв., что значительно меньше чем у его предка Nehemiah - 48,1 мм кв., при этом количество транзисторов в новом процессоре выросло с 20,4 млн. до 26,2 млн. Выпускаются эти чипы на производственных мощностях IBM с соблюдением норм 90 нм техпроцесса, применением технологии SOI и Low-K диэлектриков. Интересно в этой связи отметить, что все предыдущие процессоры семейства C3 выпускались на фабриках тайваньской компании TSMC, и опыт сотрудничества VIA и IBM в производстве процессоров пока минимален. Кстати, обзаведение новым производственным партнером совсем не значит, что компания TSMC осталась не у дел. Она по-прежнему продолжит выпуск процессоров с ядром C5P Nehemiah и части его разновидностей: C5Q с нормами 0,13 мкм и C5R с нормами 0,11 мкм. Третья инкарнация ядра Nehemiah - C5W, будет выпускаться также при участии IBM с использованием ее нового техпроцесса 90 нм + SOI. Как известно, первый кремний C7 получен IBM ближе к концу августа. В нынешних планах VIA выпуск первых пробных партий процессоров C5J Esther с нормами 90 нм техпроцесса намечен на четвертый квартал 2004 года, а массовые поставки - на первый квартал 2005 года. Несколько слов об особенностях использования чипов VIA C7. По заявлениям представителей компании, TDP новых процессоров на тактовой частоте 1 ГГц составит порядка 3,5 Вт, что вдвое меньше 7 Вт у ядра C5P на той же тактовой частоте. VIA продолжит использование и поддержку доставшегося ей от Intel разъема Socket 370, однако, предполагается широкое использование миниатюрных форм-факторов VIA C7 для эксплуатации в качестве встроенного процессора в одноплатных системах форм-фактора Nano-ITX. Думаю, что ближе к Новому году мы еще услышим про этот процессор много интересного; не удивлюсь, если впервые с помпой VIA C7 будет представлен на январской выставке CES 2005, а к началу весенней выставки CeBIT 2005 многие компании представят на нем свои интересные разработки. Transmeta: Efficeon 2 и мечты о третьем поколенииТретьим докладчиком, рассказавшей о своем процессорном детище с поддержкой инструкций x86, стала компания Transmeta с ее 90 нм процессорами Efficeon TM8800. Увы и ах, говоря грубо (именно так и хочется говорить после знакомства с деталями презентации), "обломались" все, кто жаждал узнать в дни FPF 04 что-нибудь действительно существенное по новой архитектуре. Помнится, в прошлом году Transmeta разоткровенничалась по полной программе, и тогда рассказ о ее новой концепции Efficeon был свеж и интересен. В этот раз мы получили значительно меньше, в основном, некоторые детали об архитектурных усовершенствованиях и сам факт перехода на 90 нм нормы, о котором до этого не слышал только ленивый. Ладно уж, в сторону досаду, попробуем просуммировать факты.  В отличие от своих "друзей по работе с кодом x86", нынешнее процессорное ядро Efficeon TM8800 второго поколения, которое на каком-то этапе, не замеченном мной, вдруг превратилось в Efficeon 2, совершенно не претендует на поддержку режимов SMP в целом и на многоядерность в любом виде в частности. По-прежнему, речь идет о внутреннем 256-битном VLIW ядре, обрабатывающем за такт до восьми инструкций x86, которые для него перекомпилирует на лету программная часть процессора, так называемое кодоморфное программное обеспечение (CMS, Code Morphing Software), работающее, упрощенно говоря, там, где у обычного x86 процессора находится "стык" аппаратной части и BIOS. Соответственно, само по себе ядро лишено "эмоций" и оперативно "прокручивает" в своей мясорубке все, что ему дадут, а вся суета и "нервная работа" по набивке 256-битных VLIW-молекул x86-атомами ложится на кодоморфное ПО: получилось перекомпилировать восемь команд в одно слово - аллилуйя, не получилось - "пустые" сегменты набиваются холостыми командами. На деле все несколько сложнее, однако, схематически процесс выглядит примерно так. Соответственно, от качества работы CMS напрямую зависит производительность процессора в целом. Минусы процессорного ядра Efficeon очевидны - кэширование истории исполненных последовательностей команд производится в оперативной памяти, плохая организация механизма префетча может свести на нет все преимущества VLIW-ядра, оставив его без эффективной загрузки (говорят, что в нынешних версиях Efficeon в среднем обрабатывается около пяти инструкций x86 за такт). В то же время плюсы также очевидны: доработал кодоморфное программное обеспечение - и "заливай" новую версию прошивки, без малейших аппаратных изменений. Захотел, к примеру, включить поддержку SSE3 или "антивирусного" бита NX- никаких проблем, ядро остается неизменным, лишь требуется новая версия CMS. Собственно говоря, нынешнее поколение процессоров Efficeon 2 как раз и отличается новой прошивкой кодоморфного ПО да портированием архитектуры на нормы 90 нм техпроцесса, которое состоялось на фабрике Akiruno Technology Center компании Fujitsu Electronic Devices Group еще весной, в рамках анонса TM8800. Все остальные плюсы Efficeon TM8800 в виде технологии AntiVirusNX (поддержка бита NX под Microsoft Windows XP Service Pack 2) и поддержки инструкций SSE3 произошли на уровне firmware.  В остальном, конструкция чипа осталась неизменна: интегрированный контроллер памяти с поддержкой DDR400, встроенная шина AGP 4X, "связь с внешним миром" по шине HyperTransport. Efficeon 2 обладает 1 Мб кэша L2, 128 Кб кэша инструкций L1 и 64 Кб кэша данных L1, поддерживает технологию энергосбережения LongRun2. Как раз к плюсам 90 нм Efficeon TM8800 можно отнести меньшее энергопотребление, нормируемое на уровне порядка 3 Вт для тактовой частоты 1 ГГц. Версия Efficeon TM8800 с тактовой частотой 1,6 ГГц выпускается с лета, фигурирует в ограниченных партиях ноутбуков Sharp PC-MP50G и PC-MP70G. В рамках Fall Processor Forum компания Transmeta показала Efficeon TM8800 с тактовой частотой 2 ГГц. Efficeon 22 выпускается нынче в двух видах корпуса: TM8800 (29 x 29 мм) и TM8820 (21 x 21 мм), электрически совместимыми с аналогами Efficeon первого поколения, TM8600 и TM8620. На перспективу Transmeta декларирует для дизайна Efficeon 2 следующие нормы TDP:

Трудно сказать, хорошо это или "уже поздно", ибо на подходе новые Ultra Low Voltage версии процессоров Intel Pentium M с 90 нм ядром Dothan и сравнимыми уровнями энергопотребления. Если бы Transmeta смогла как следует развернуться с массовостью выпуска своих чипов и перестала барахтаться в пределах "ограниченных партий чипов", не исключено, что у нее появилась бы возможность отхватить более-менее значимую долу рынка x86, по крайней мере, в секторе процессоров для ноутбуков, blade-серверов и встраиваемых систем. Пока что доходы компании наполовину складываются от лицензирования технологии энергосбережения LongRun2 и в целом значительно ниже доходов, уже не первый год. Хватит ли у Transmeta силенок на массовые поставки чипов - сказать трудно, пока что относительно массово выпускаются лишь 0,13 мкм чипы Crusoe ТМ5800 на базе предыдущей архитектуры с 128-битным VLIV-ядром.  Впрочем, представители Transmeta не теряют оптимизма и демонстрируют симпатичные концепты крохотных систем на базе Efficeon 2, например, вот эту плату Stratosphere, габариты которой лишь незначительно превыщают размеры обычного PCMCIA устройства.  Что касается третьего поколения процессоров Efficeon, Transmeta пообещала раскрыть подробности о нем только в 2005 году. Этот, пока еще никак не названный Efficeon 3 будет обладать удвоенным размером кэша, улучшенной шиной памяти и обновленной архитектурой, позволяющей обрабатывать большее количество инструкций за такт. Более того, Efficeon 3 будет поддерживать расширенный 64-битный набор инструкций и даже свою собственную технологию виртуализации для одновременной загрузки нескольких операционных систем - именно то, что у Intel называется Silvervale и Vanderpool, а у AMD - Pacifica. Что тут сказать - круто, планов громадье. Однако, сейчас хотелось бы пожелать компании все же наладить массовый выпуск нынешних Efficeon 2, например, 2 ГГц версий, которые в массовых партиях ожидаются к Новому году. В ином случае, у постоянно терпящей убытки компании мечты о третьем поколении Efficeon однажды могут с легкостью материализоваться в печальные строчки дедушки Некрасова: "жаль только жить в эту пору прекрасную уж не придется ни мне, ни тебе".

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|