|

Опрос

|

реклама

Быстрый переход

Японцы создали магнитную память на квантовых эффектах — она в 25 раз быстрее DRAM, почти не греется и не изнашивается

15.05.2026 [21:32],

Геннадий Детинич

Учёные Токийского университета (The University of Tokyo) совместно с коллегами из Центра RIKEN CEMS представили принципиально новый тип энергоэффективного элемента памяти на основе квантово-механических явлений. Переключение состояний элемента опирается на перенос спин-орбитального момента электрона вместо обычного потока электронов (электрического тока), что позволяет памяти работать быстрее, с ничтожным потреблением и почти без износа.

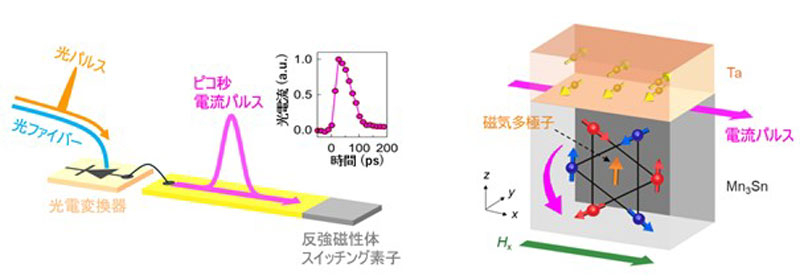

Источник изображения: The University of Tokyo Нечто подобное происходит в случае магниторезистивной памяти MRAM. Более того, давно существуют прототипы памяти STT-MRAM (Spin-transfer Torque MRAM), основанные на том же эффекте переноса спин-орбитального момента электрона. Но японские учёные заявляют, что пошли ещё дальше и подобрали такие материалы, которые работают буквально от квантов энергии. Это почти исключает обычное течение тока и сопутствующие ему случайные столкновения электронов с атомами кристаллической решётки, ведущие к паразитному рассеиванию тепла — глобальной проблеме современной электроники. Этим чудо-материалом оказался антиферромагнетик станнид тримарганца (Mn3Sn, марганец плюс олово). Он является неколлинеарным антиферромагнетиком. Это значит, что атомы марганца в сплаве расположены в особой «кагоме»-решётке (Kagome lattice), а их магнитные моменты направлены под углом 120° друг к другу (как на рисунке). При этом, в отличие от обычных антиферромагнетиков, Mn3Sn демонстрирует гигантский аномальный эффект Холла — то есть ведёт себя как ферромагнетик, создавая сильный направленный отклик на электрический ток, хотя его полная намагниченность почти равна нулю. По этим причинам материал быстро и сильно реагирует на привнесённый электроном спин-орбитальный момент — ему не нужны значительные токи для достижения эффекта переключения ячейки из одного магнитного состояния в другое. Созданный учёными прототип магнитного переключателя способен менять своё логическое состояние всего за 40 пикосекунд, что примерно в 25 раз быстрее лучших современных коммерческих SRAM- и DRAM-элементов, работающих в диапазоне единиц наносекунд. Но главная особенность разработки — сочетание рекордной скорости с крайне низким энергопотреблением, что особенно важно для будущих дата-центров и специализированных ИИ-ускорителей, где проблема тепловыделения становится главным ограничителем роста производительности. Очень короткие управляющие импульсы длительностью 40 пс просто не позволяют элементу разогреться и направить мощность в бесполезное тепло. Также исследователи продемонстрировали высокую стабильность циклов переключения элемента, что критически важно для энергонезависимой памяти следующего поколения. Заявленное число циклов переключения достигает 1012, что недостижимо для современной энергонезависимой памяти. Но и это ещё не все «чудеса». Отдельный прорыв в проекте связан с интеграцией фотонных технологий в элемент. Учёные показали, что переключение возможно не только электрическим сигналом, но и с помощью 60-пикосекундных фототоков, генерируемых лазером обычного телекоммуникационного диапазона (около 1550 нм) и фотоэлектрическим преобразователем. Это фактически демонстрация концепции прямого интерфейса между оптическими каналами передачи данных и магнитной памятью — без промежуточной громоздкой КМОП-логики. Для дата-центров это особенно важно: современные оптоволоконные магистрали уже работают именно в этом диапазоне длин волн, а значит, подобные элементы потенциально могут стать основой для сверхбыстрой опто-спинтронной памяти, напрямую связанной с межсерверными каналами связи. Практическое значение работы выходит далеко за рамки лабораторного эксперимента. Если технология будет масштабирована до интегральных схем, она может лечь в основу нового класса вычислительных архитектур — энергонезависимых процессоров с почти мгновенным переключением состояний и минимальным энергопотреблением. Это особенно актуально для задач искусственного интеллекта, периферийных и экзафлопсных вычислений, где затраты на охлаждение уже сопоставимы с затратами на сами вычисления. По сути, японские исследователи приблизили создание памяти, которая сочетает преимущества DRAM по скорости и флеш-памяти по энергонезависимости, — комбинации, которую индустрия пытается реализовать уже более двух десятилетий. «Роснано» подала миллиардный иск к бывшим руководителям из-за провала проекта выпуска в России чипов MRAM

14.12.2025 [13:05],

Владимир Фетисов

Группа «Роснано» предъявила иск бывшим руководителям компании о взыскании 11,9 млрд рублей убытков по проекту Crocus. В рамках этой программы планировалось организовать на территории России производство магниторезистивной оперативной памяти (MRAM).

Источник изображения: Tingey Injury / unsplash.com «Иск о взыскании убытков, понесенных «Роснано» в связи с реализацией проекта Crocus, направлен на привлечение ответственных лиц, отвечающих за одобрение и реализацию проекта Crocus в период с 2011 по 2020 гг. Предъявленный иск — часть планомерной работы по восстановлению капитала, прав и репутации компании, которая ведётся в тесном взаимодействии с правоохранительными и надзорными органами. Мы продолжим отстаивать и защищать интересы и права «Роснано» как в досудебном порядке, так и в рамках уголовных дел или в гражданском и арбитражном судопроизводстве», — приводит источник заявление директора по особым поручениям АО «Роснано» Евгения Фролова. Он также отметил, что «уже на старте проекта в 2011 году члены правления «Роснано» и кураторы проекта Crocus проигнорировали его технологические риски вопреки своим обязанностям не предусмотрели механизмы защиты прав госкомпании и государства от их наступления». В сообщении сказано, что за девять лет реализации проекта принимавшие решения о его финансировании ответственные лица нарушали нормативные акты АО «Роснано», которые регламентируют инвестиционную деятельность. Финансирование проекта увеличивалось бесконтрольно, несмотря на его убыточность и инвестиционную непривлекательность, а также нарушение контрольных точек реализации. Стартовавший в 2011 году проект по созданию уникального для страны производства памяти MRAM не достиг первоначальных целей, тогда как возможность возврата значительной части вложений была утрачена. Фролов отметил, что с «первого дня антикризисной программы ведётся системная аналитическая работа по выявлению обстоятельств и объёмов очевидно недобросовестных инвестиционных решений и финансовых операций по целому ряду проектов, которые были реализованы с явными нарушениями». TSMC создала улучшенную магниторезистивную память — она потребляет в 100 раз меньше энергии

20.01.2024 [20:57],

Геннадий Детинич

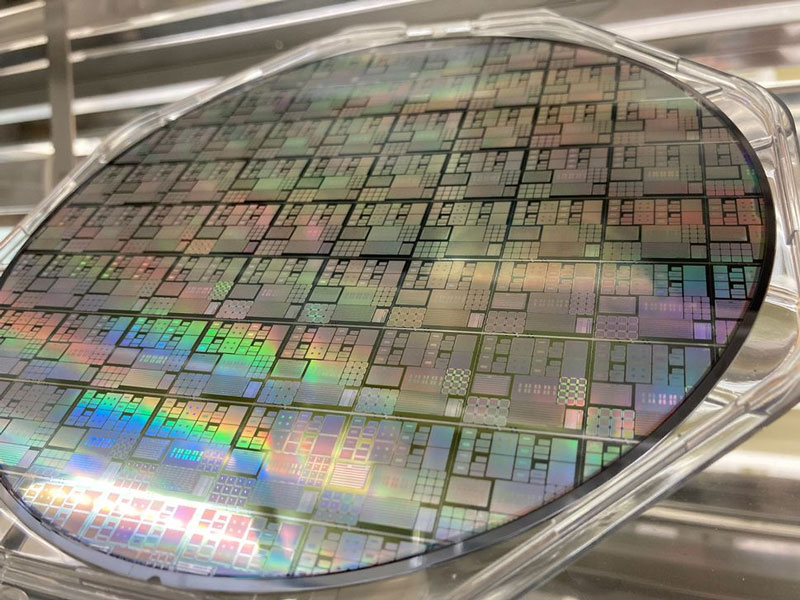

Компания TSMC вместе с учёными Тайваньского НИИ промышленных технологий (ITRI) представила совместно разработанную память SOT-MRAM. Новое запоминающее устройство предназначено для вычислений в памяти и для применения в качестве кеша верхних уровней. Новая память быстрее DRAM и сохраняет данные даже после отключения питания, и она призвана заменить память STT-MRAM, потребляя при работе в 100 раз меньше энергии.

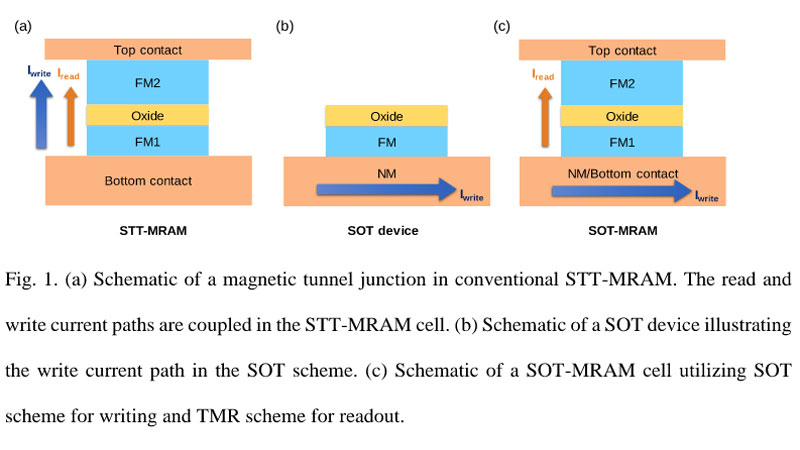

Экспериментальная пластина с чипами SOT-MRAM. Источник изображения: TSMC / ITRI На роль кеш-памяти верхних уровней (от L3 и выше) и для вычислений в памяти, среди прочих перспективных вариантов энергонезависимой памяти, долгое время претендовала магниторезистивная память с записью с помощью переноса спинового момента (STT-MRAM). Этот вариант памяти передавал намагниченность запоминающей ячейке через туннельный переход с помощью спин-поляризованного тока. За счёт этого потребление энергии STT-MRAM оказалось кратно меньше потребления обычной памяти MRAM, в которой запись осуществлялась наведённым электромагнитным полем. Память SOT-MRAM идёт ещё дальше. Запись (намагниченность) ячейки — слоя ферромагнетика — происходит с помощью спин-орбитального вращательного момента. Эффект проявляется в проводнике в основании ячейки в процессе комбинации двух явлений: спинового эффекта Холла и эффекта Рашбы—Эдельштейна. В результате на соседний с проводником ферромагнетик воздействует индуцированное магнитное поле со стороны спинового тока в проводнике. Это приводит к тому, что для работы SOT-MRAM требуется меньше энергии, хотя настоящие прорывы ещё впереди.

Маршруты токов записи и чтения для двух типов ячеек MRAM. Источник изображения: National University of Singapore Другие преимущества памяти SOT-MRAM заключаются в раздельных схемах записи и чтения, что положительно сказывается на производительности, а также увеличенная устойчивость к износу. «Эта элементарная ячейка обеспечивает одновременное низкое энергопотребление и высокоскоростную работу, достигая скорости до 10 нс, — сказал доктор Ши-Чи Чанг, генеральный директор исследовательских лабораторий электронных и оптоэлектронных систем ITRI. — Её общая вычислительная производительность может быть дополнительно повышена при реализации схемотехники вычислений в памяти. Заглядывая в будущее, можно сказать, что эта технология обладает потенциалом для применения в высокопроизводительных вычислениях (HPC), искусственном интеллекте (AI), автомобильных чипах и многом другом». Память SOT-MRAM с задержками на уровне 10 нс оказывается ближе к SRAM (задержки до 2 нс), чем обычная память DRAM с задержками до 100 нс и выше. И конечно, она существенно быстрее популярной сегодня 3D NAND TLC с задержками от 50 до 100 мкс. Но в процессорах и контроллерах память SOT-MRAM появится не завтра и не послезавтра, как не стала востребованной та же память STT-MRAM, которая разрабатывается свыше 20 лет. Всё это будущее и не очень близкое, хотя, в целом, необходимое для эффективных вычислений в памяти и устройств с автономным питанием. |