⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Трудный штурм микроскопических высот: как чиплеты выходят в третье измерение

Упёршись в reticle limit, инженеры-микроэлектронщики нащупали логичный выход — перешли от цельных СБИС к составным. Но размещение чиплетов в единой плоскости затрудняет налаживание между ними высокоскоростных коммуникаций с малыми задержками. И потому следующим очевидным шагом становится переход к 3D. Назвать этот шаг очевидным позволяет сама технология изготовления классических планарно-унитарных чипов, начальное представление о которой было дано в наших предыдущих материалах (раз, два, три). Дело в том, что после литографирования полупроводниковых структур на плоскости кремниевой пластины-заготовки остаются только сами эти структуры — латентные транзисторы, не способные даже функционировать должным образом (пропускать или не пропускать электрический ток на данном участке цепи) по причине банального отсутствия металлических проводников, которые эту общую цепь формировали бы. Именно здесь технологии изготовления сложных полупроводниковых схем делают первый, пусть и крохотный, шаг от плоскости в третье измерение. Над усеянной транзисторами плоскостью кремниевой пластины формируется слой металлических шин (соединённых с этими транзисторами там, где это необходимо, вертикальными проводящими перемычками), а между полем транзисторов и шинной сетью добавляется прослойка изолирующего диэлектрика. Понятно, что единственным уровнем контактов дело не ограничивается. Формируемые из близко расположенных транзисторов базовые логические схемы (например, типовой сумматор) необходимо сводить в более крупные узлы (скажем, арифметико-логическое устройство, способное производить более сложные вычисления), а уже из них формировать структуры верхнего расчётного уровня (блоки CUDA или что-то в таком духе). Разместить столь сложную иерархическую сеть проводников на единой плоскости в общем случае не представляется возможным.

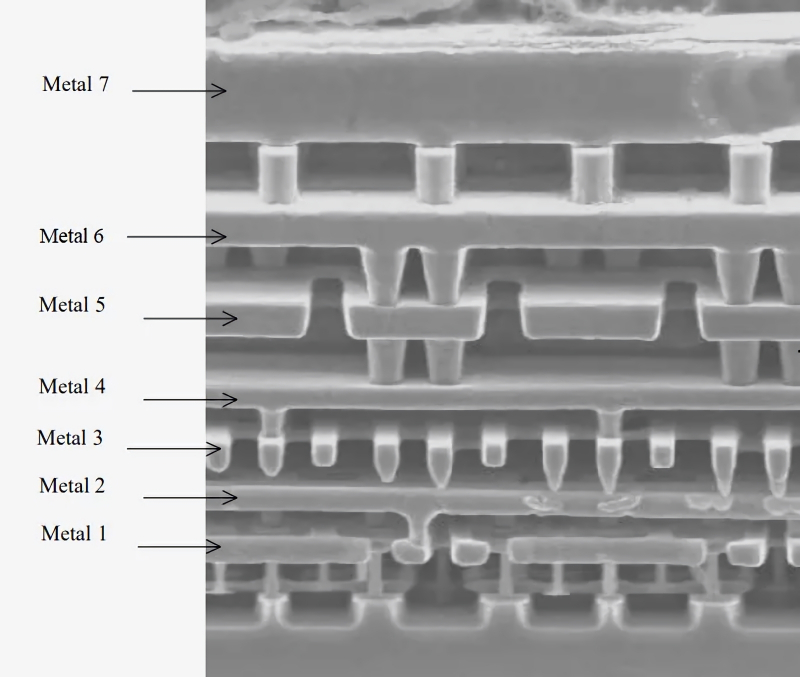

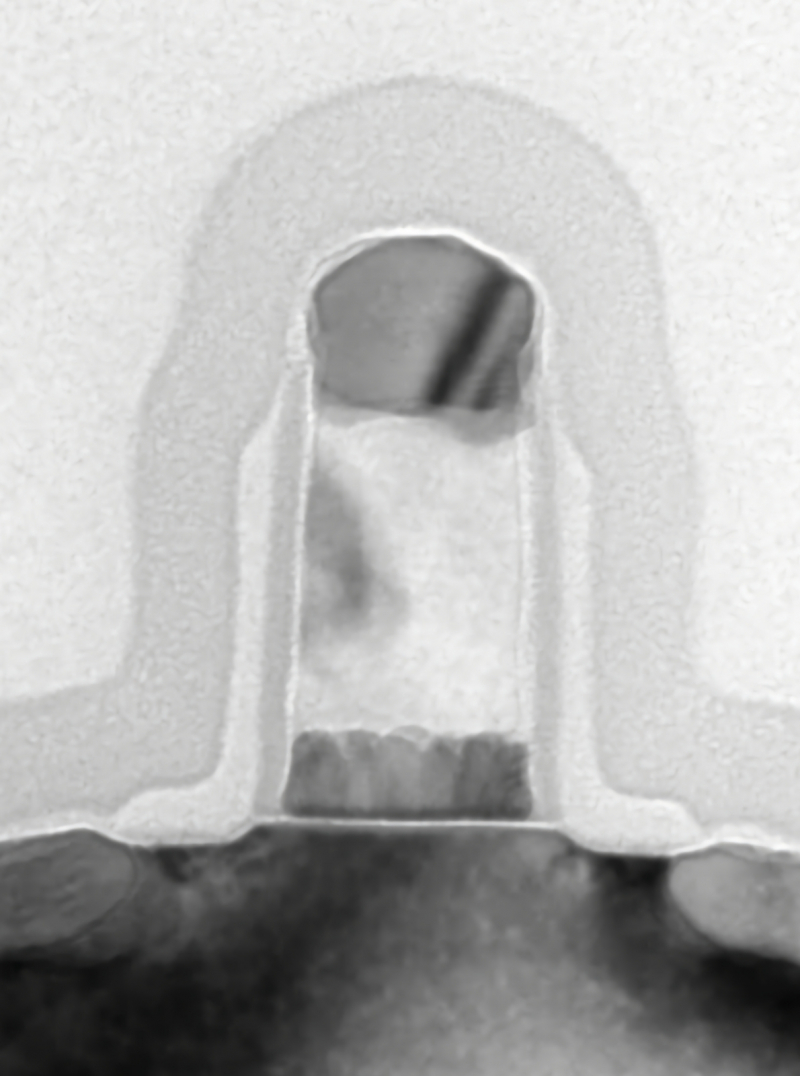

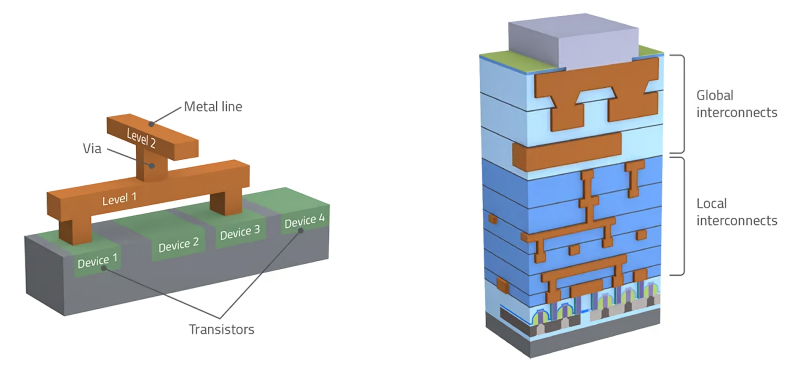

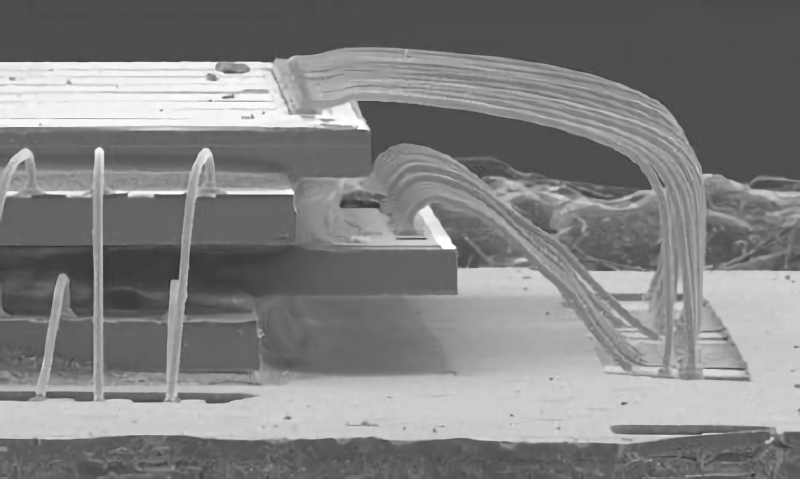

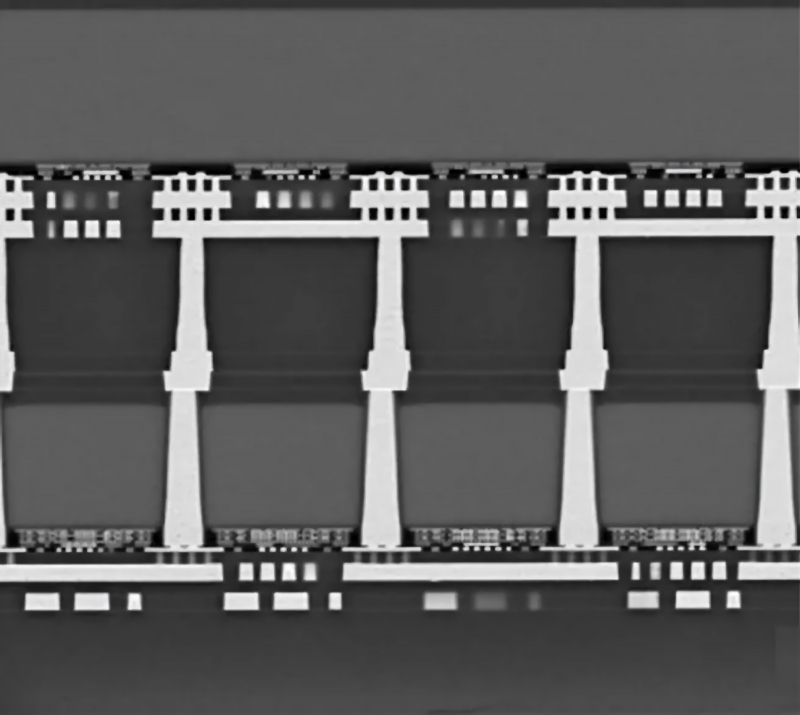

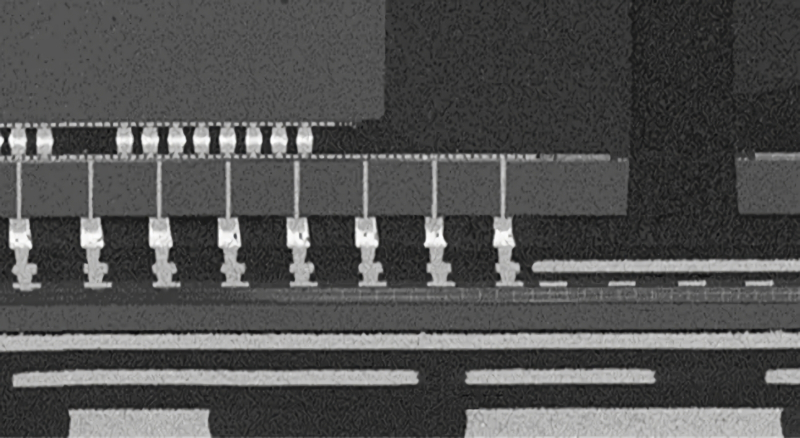

Микросхемы, кажущиеся плоскими, на деле состоят из множества слоёв металлизации, переложенных изолирующим диэлектриком (на данном микроснимке он удалён травлением ради наглядности) и соединенных между собой (и с полупроводниковыми структурами в основании) посредством вертикальных контактов — пилонов (источник: Intel) В результате число слоёв металлических контактов, ответственных за превращение покрытой разрозненными транзисторами поверхности кремниевой заготовки в способный к решению чрезвычайно сложных задач чип, в современных СБИС достигает порой полутора десятков. И хотя путь к этому достижению не был простым, преодоление его помогло инженерам-электронщикам в дальнейшем уверенно взяться за освоение третьего измерения уже в полном масштабе — то есть перейти от одиночных многослойных микросхем к взаимосвязанным уровням, образованным целыми чипами. Для того чтобы понять, как это делается, ненадолго вернемся к процессу создания полупроводниковых чипов. ⇡#Есть контакт? Как устроен процесс металлизации чиповИтак, следующий после литографирования шаг обработки кремниевой пластины называется металлизацией. Поверхность с подготовленными на ней полупроводниковыми структурами покрывают слоем диэлектрика — обычно это диоксид кремния, SiO2, — а уже сверху напыляют металл. Изначально это был алюминий; у меди иные физико-химические свойства, и решение всех сопутствующих инженерных задач потребовало определённого времени.

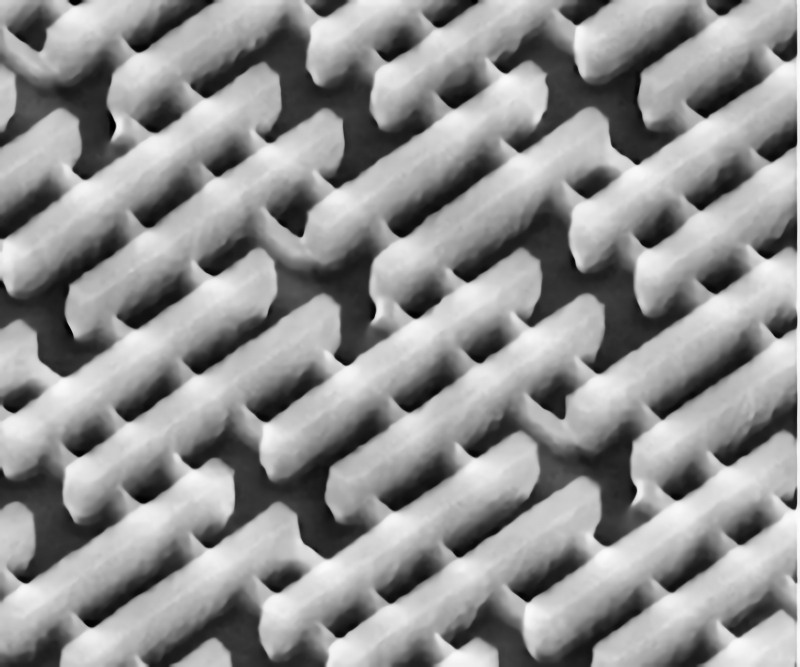

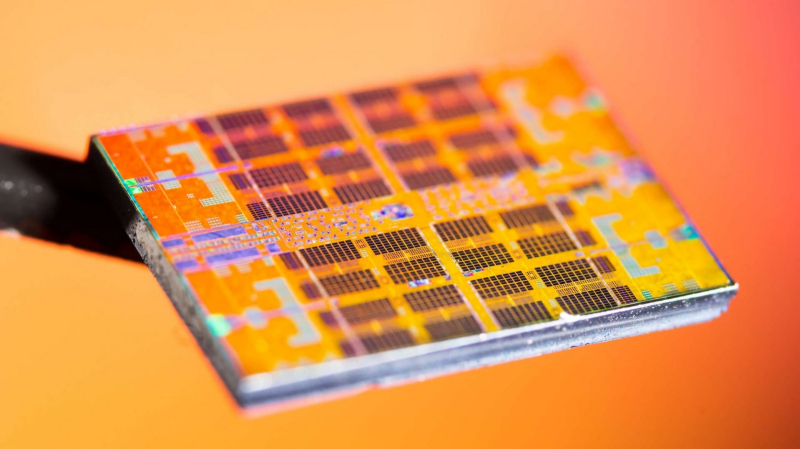

Гребенчатые структуры FinFET-транзисторов на поверхности полупроводникового чипа, выполненного по технологии «22 нм» (источник: Intel) Напыление — точнее, химическое осаждение из парообразного состояния, chemical vapor deposition, — формирует поверх диэлектрика сплошной металлический слой. Не слишком ровный, поскольку заготовка усеяна гребенчатыми полупроводниковыми структурами. Над гребнями высота осаждённого диэлектрика больше, в промежутках меньше — в точности так же неровно ложится снежная пелена на самые обыкновенные огородные грядки. Чтобы оставить на этом слое лишь необходимые алюминиевые дорожки между выведенными с поверхности кремниевой пластины контактами, применяют примерно тот же комплекс процедур, что и в ходе литографирования самой этой пластины: экспонирование по фотомаске (masking), травление (etching) и закрепление (doping) полученной структуры. Чем дальше от кремниевой основы расположен слой металлических контактов, тем более крупномасштабные логические узлы изготавливаемой СБИС он формирует.

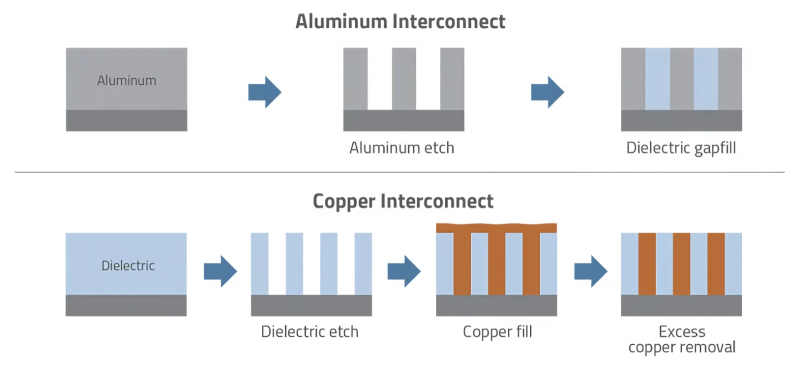

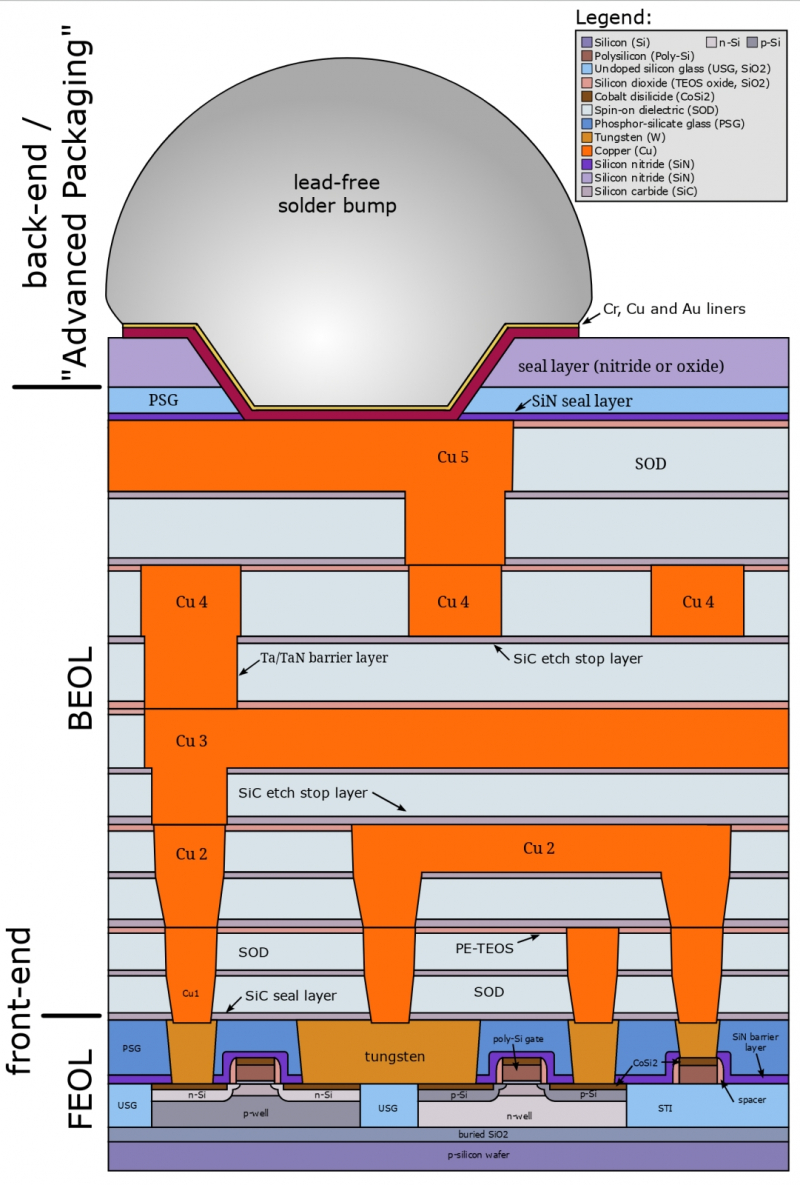

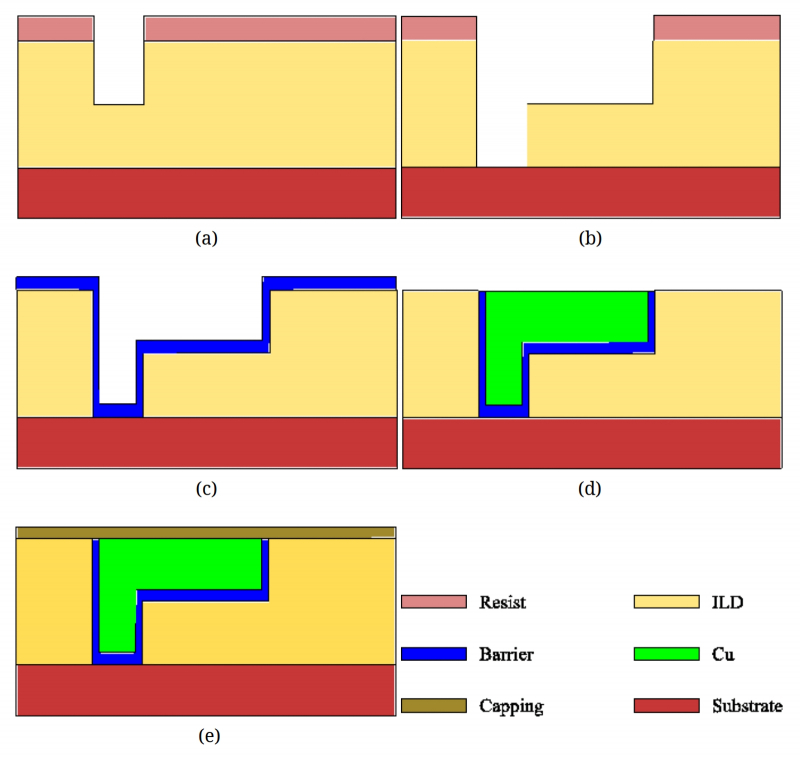

Изготавливать алюминиевые токоведущие микродорожки технологически проще, зато медные обеспечивают повышенные проводимость и надёжность (источник: Lam Research) Для меди процедура чуть сложнее — она подразумевает нанесение промежуточного слоя диэлектрика, его маскирование, экспонирование и протравку, а затем уже заполнение полученных канавок металлом с последующим удалением излишков. У меди выше электропроводность, медный контакт данного сечения в общем случае прочнее и надёжнее алюминиевого, но работа с медью подразумевает и ряд дополнительных нетривиальных процедур, что неизбежно оборачивается для чипмейкера добавочными издержками. Ту часть процесса изготовления СБИС (и заодно те слои металла и диэлектрика), которая относится к формированию отдельных полупроводниковых компонентов на поверхности кремниевой заготовки — транзисторов, сопротивлений, конденсаторов и прочего, называют фронтальным терминалом (front-end-of-line, FEOL). Соответственно, ряды вышележащих слоёв с пронизывающими их металлическими контактными пилонами, которые ответственны за комбинирование этих базовых компонентов в вычислительные логические контуры, носят название тыльных терминалов (back end of line, BEOL).

Фронтальный и тыльный терминалы чиплета, представленные соответствующими слоями металлизации, а также верхний «упаковочный» слой с выведенным на него контактным зерном (bump) (источник: Wikimedia Commons) Если микросхема готовится стать частью многоуровневой составной структуры, на поверхности BEOL формируются небольшие полусферические контакты с характерными промежутками между их центрами (pitch) в пределах 50-300 мкм. По-английски эти контакты называют bump, что можно безыскусно перевести как «пупырышки», а можно и поизящнее, как «зернь» — если вспомнить название известной издревле ювелирной техники. Самым последним на полностью укомплектованную металлическими контактами заготовку наносят изолирующий слой диэлектрика, часто даже не один. И уже после этого пластина передаётся на специализированное предприятие (обычно это совершенно независимая компания по отношению к собственно чипмейкеру), где ее разрезают на отдельные чипы. Их, в свою очередь, упаковывают в защитные корпуса. Лишь по завершении этой процедуры планарно-унитарная микросхема пригодна для дальнейшего использования — установки в подходящее гнездо либо напаивания непосредственно на монтажную плату. Казалось бы, весь этот комплекс операций не так уж и сложен по сравнению с фотолитографическим процессом — особенно если учесть, что разрешение оптической системы для изготовления токоведущих дорожек даже на самом ближнем к транзисторам слое требуется уже не столь высокое, как при формировании самих полупроводниковых структур. Однако в микропроцессорном производстве, как мы не раз уже отмечали, ничто не бывает просто. Вот и в случае металлизации имеется свой, весьма чувствительный камень преткновения. А именно — та самая принципиальная неровность получающейся после осаждения диэлектрика, а затем и металла поверхности.

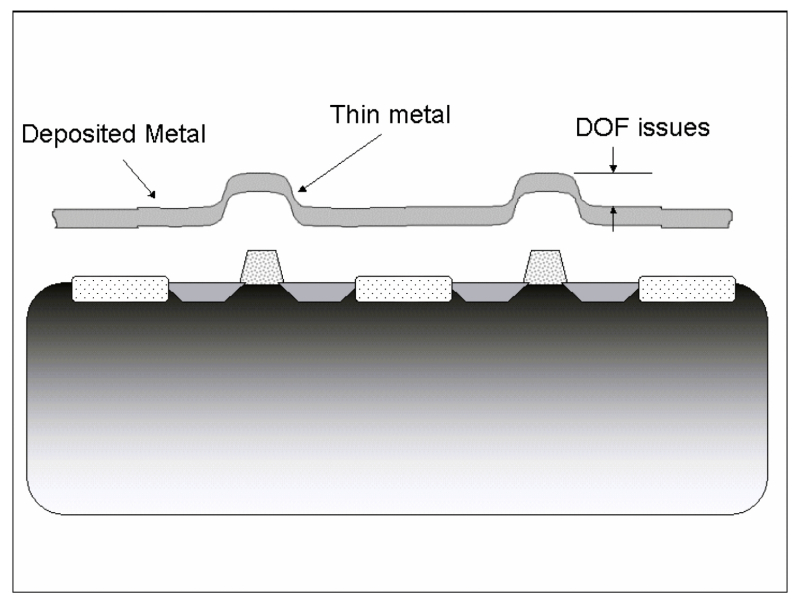

Безыскусное нанесение металла поверх слоя диэлектрика (покрывающего, в свою очередь, полупроводниковые структуры с их гребнями) чревато как чрезмерным истончением этого слоя на склонах, так и затруднениями с фокусировкой литографического оборудования на неровностях (источник: Cornell University) Процесс осаждения представляет собой, по сути, закрепление на поверхности одного молекулярного/атомарного слоя осаждаемого вещества за другим. Таким образом диэлектрик, а за ним и металл воспроизводят — лишь с минимальным сглаживанием, обусловленным итоговой толщиной материала, — все неровности подстилающей поверхности. Для диэлектрика это не проблема, а вот для металла — ещё какая. Дело в том, что контуры, образуемые токопроводящими дорожками металлического слоя, должны формировать электрические цепи строго определённых характеристик — в первую очередь это относится к их сопротивлению, — чтобы итоговые логические схемы с участием транзисторов функционировали должным образом. Сопротивление определяется площадью поперечного сечения проводника. Если часть токоведущей дорожки придётся на склон, сформированный в ходе процессов осаждения над транзисторным гребнем, на этом участке сечение её будет не таким, как на плоскости. Это неизбежно изменит расчётные электропроводные характеристики данного фрагмента цепи — и может кардинальным образом нарушить работоспособность логического узла в целом, вплоть до внезапного пробоя на чересчур тонком участке проводника.

32-нм (в сечении основания) транзистор Panasonic HKMG NMOS, покрытый слоем изолирующего диэлектрика (источник: Chipworks) Допустим, достаточно тонкий техпроцесс позволит осаждать металл слоем толщиной буквально в считаные атомы, так что принципиальной разницы в сечениях между отдельными участками токоведущей дорожки всё же не будет. Но при столь мелких масштабах литографирования уже не удастся сбрасывать со счетов эффекты глубины фокусировки (depth-of-focus, DoF). Ведь на самом нижнем уровне металлические шины соединяют между собой отдельные транзисторы, то есть разрешение фотолитографического процесса при формировании этих шин (токоведущих дорожек) требуется почти столь же высокое, сколь и при изготовлении самих полупроводниковых элементов на кремниевой пластине. ⇡#Шкурочкой пройтись: как поверхность диэлектрического слоя делают плоскойЗагвоздка в том, что современные литографы — и DUV, и EUV — в своей работе полагаются на оптические системы с максимально возможной на данном этапе технологического развития числовой апертурой. Чем выше апертура (NA в известной по прошлым статьям настоящего цикла главной формуле оптической фотолитографии), тем более миниатюрные детали возможно изготовить при помощи данной установки. Но увеличение апертуры неизбежно уменьшает глубину резкости — тот самый параметр DoF. Для актуальных сегодня техпроцессов DoF уже настолько невелик, что ничтожный, исчисляемый микронами перепад высот между гребнями и долинами первого металлического слоя становится критическим препятствием на пути уверенной фокусировки литографа для изготовления токоведущих дорожек.

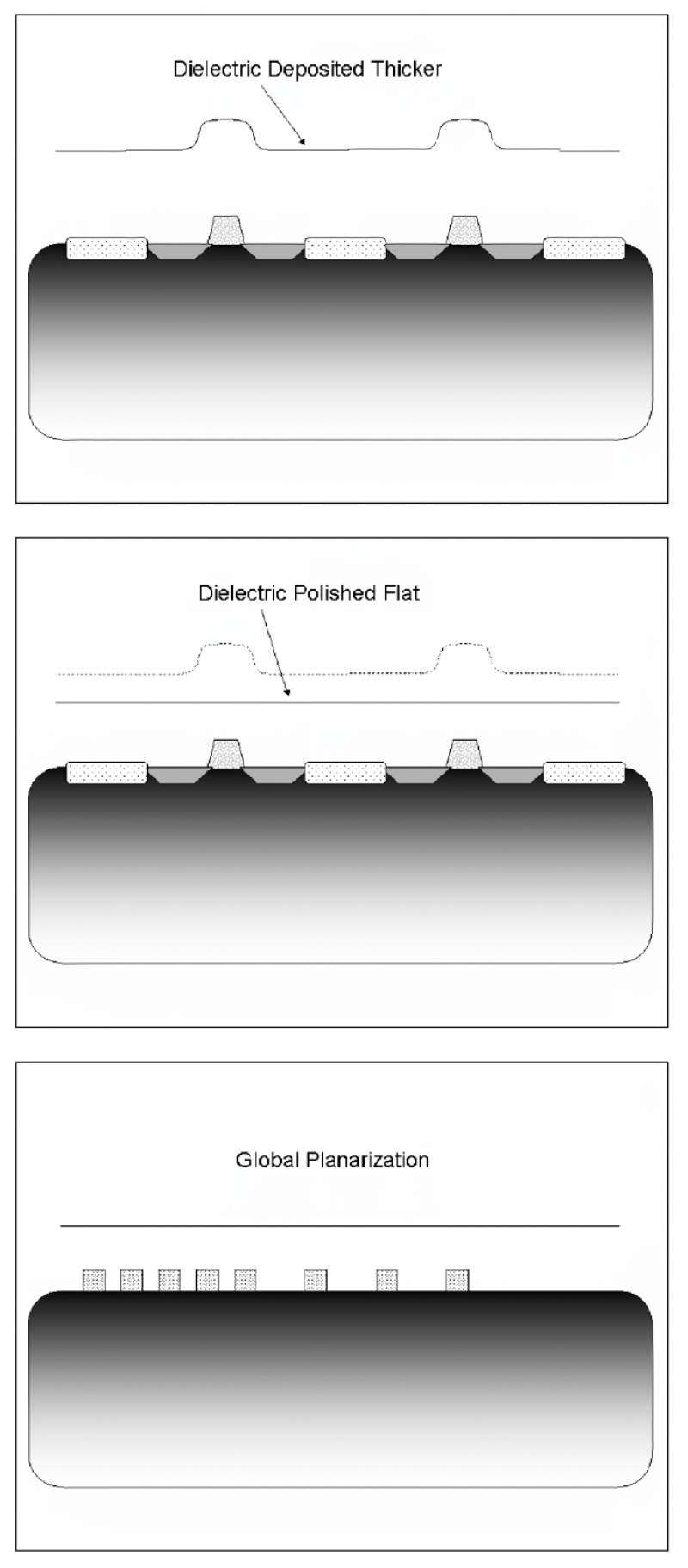

Установка для химико-механической планаризации ChaMP 332, рассчитанная на разравнивание слоя диэлектрика на литографированных пластинах диаметром до 300 мм [источник: ACCRETECH (Europe) GmbH] Здравый смысл подсказывает простое и изящное решение проблемы: поскольку толщина диэлектрика над гребнями транзисторных затворов никак не влияет на изоляцию самих этих затворов (плюс их истоков и стоков заряда) от металлического слоя, логично было бы покрыть поверхности кремния изолирующим слоем заведомо большей, чем это необходимо, толщины. А затем срезать и отполировать его — чтобы слой металла наносился уже на совершенно гладкую поверхность. Ведь сделать ровным зеркало ледяного катка не составляет труда, насколько сложным ни был бы рельеф покрытой льдом почвы. Должно сработать! На самом же деле мысль о том, что литографированную кремниевую пластину, покрытую тонким слоем диэлектрика, можно полировать, далеко не сразу пришла в головы инженерам — разработчикам оборудования для изготовления полупроводников. Долгое время они полагались на ряд технологий, подразумевающих использование либо более легкоплавких, чем SiO2, диэлектриков (с последующим их нагревом для растекания, в ходе которого перепады высот между гребнями и долинами сглаживались), либо и вовсе жидких изоляторов с высоким содержанием органики, которые тоже свободно растекались по поверхности кремния, после чего органическая составляющая — опять-таки в ходе нагревания — выпаривалась.

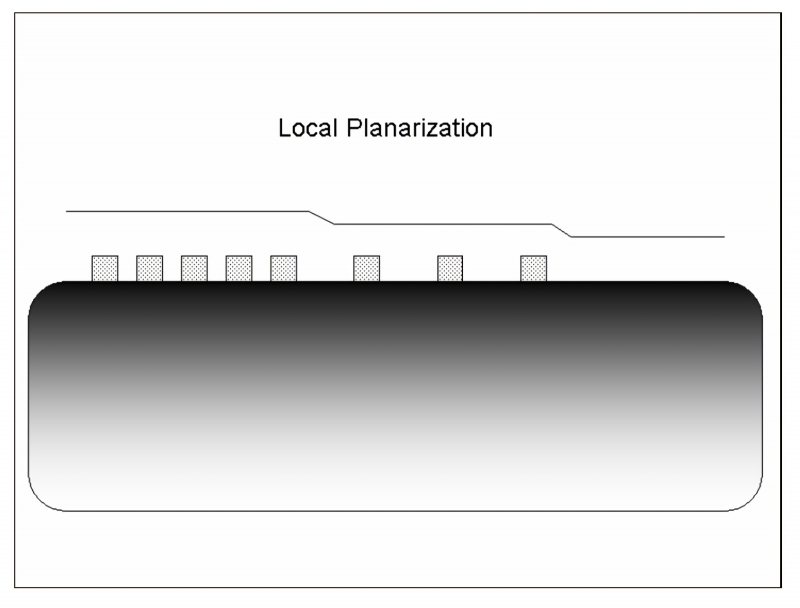

Локальная химическая планаризация решает задачу выравнивания поверхности заготовки на ограниченном участке (источник: Cornell University) Таких чисто химических по своей сути методов было предложено и испробовано много, но все они имели один и тот же главный недостаток — локальность. Капля диэлектрика, нанесённая на пластину, формировала ограниченный по площади ровный участок. Если по соседству гребни транзисторов располагались гуще, жидкий диэлектрик растекался несколько хуже — и в результате этот участок оказывался уже немного приподнят над уровнем предыдущего. Это опять-таки создавало сложности с последующей металлизацией заготовки. Переход от чистой химии к сочетанию её с механикой в деле планаризации (уплощения поверхности диэлектрика на заготовке) совершили в конце 1980-х инженеры IBM. Предложенная ими процедура химико-механической планаризации (chemical mechanical planarization, CMP) подразумевала тот самый логичный путь, что был уже упомянут: нанесение на кремниевый кристалл заведомо более толстого слоя диэлектрика, чем это требуется для уверенной изоляции, с последующим удалением (путём полировки) ненужных холмов над гребнями и доведением толщины слоя до фактически необходимой.

Три простых (в теории) этапа применяемого ко всей пластине-заготовке разом CMP-процесса (источник: Cornell University) Этот метод хорош тем, что позволяет сразу обрабатывать всю пластину-заготовку целиком, да ещё и не подразумевает применения более сложных (и менее стойких), чем SiO2, диэлектриков. Если прежние, чисто химические способы планаризации позволяли (из-за накопления разностей толщин слоёв соседних диэлектрических «клякс» на пластине-заготовке) создавать не более 3-4 уровней металлических шин, то CMP уже на ранних этапах взросления технологии уверенно обеспечивал формирование 7-8 слоёв. Ещё одно преимущество CMP — в возможности без принципиальных затруднений, путём последовательного применения одной и той же процедуры с разными фотомасками, создавать вертикальные токоведущие каналы между слоями — via holes, или попросту vias (здесь via — перешедший в английский язык из латыни предлог со значением «через», «сквозь»). Прежде у инженеров с ними было немало мороки. В ходе формирования методом CMP двойного дамасского рисунка (dual damascene process) последовательно получают травлением как переходные между слоями отверстия — вертикальные шурфы, так и горизонтальные канавки. Затем эти проёмы заполняются металлом и образуют, соответственно, межслоевые контакты и проводящие шины внутри слоёв.

Последовательные этапы реализации двойного дамасского процесса методом CMP: (a) протравливание вертикального шурфа на половинную глубину, (b) протравливание шурфа на полную глубину до субстрата с одновременным формированием горизонтальной канавки, (c) осаждение защитного слоя, блокирующего проникновение атомов меди в диэлектрик, (d) заполнение выемок медью, (e) изоляция сформированных токоведущих структур (источник: Technical University of Vienna) Ложка дёгтя есть, безусловно, и тут — куда же без неё в полупроводниковой отрасли! Механическая процедура полировки тонкой кремниевой пластины, покрытой ещё более эфемерным слоем диэлектрика, требует высочайшей точности выполнения всех операций, особо тщательного подбора абразивов, а также скрупулёзного удаления всех, до последнего, мельчайших фрагментов снятого с заготовки слоя перед началом нового этапа металлизации. Если допустить здесь хотя бы малейшую неаккуратность, микроскопические частицы неизбежно будут оседать на линзы, зеркала и фотомаски оптической системы — с понятными отрицательными последствиями. Но CMP-метод, который начали применять с 220-нм техпроцесса, настолько успешно себя зарекомендовал, что продолжает оставаться главной технологией организации межсоединений внутри планарно-унитарных чипов по сей день. Более того, и на обозримую перспективу заделы по дальнейшему его совершенствованию имеются.

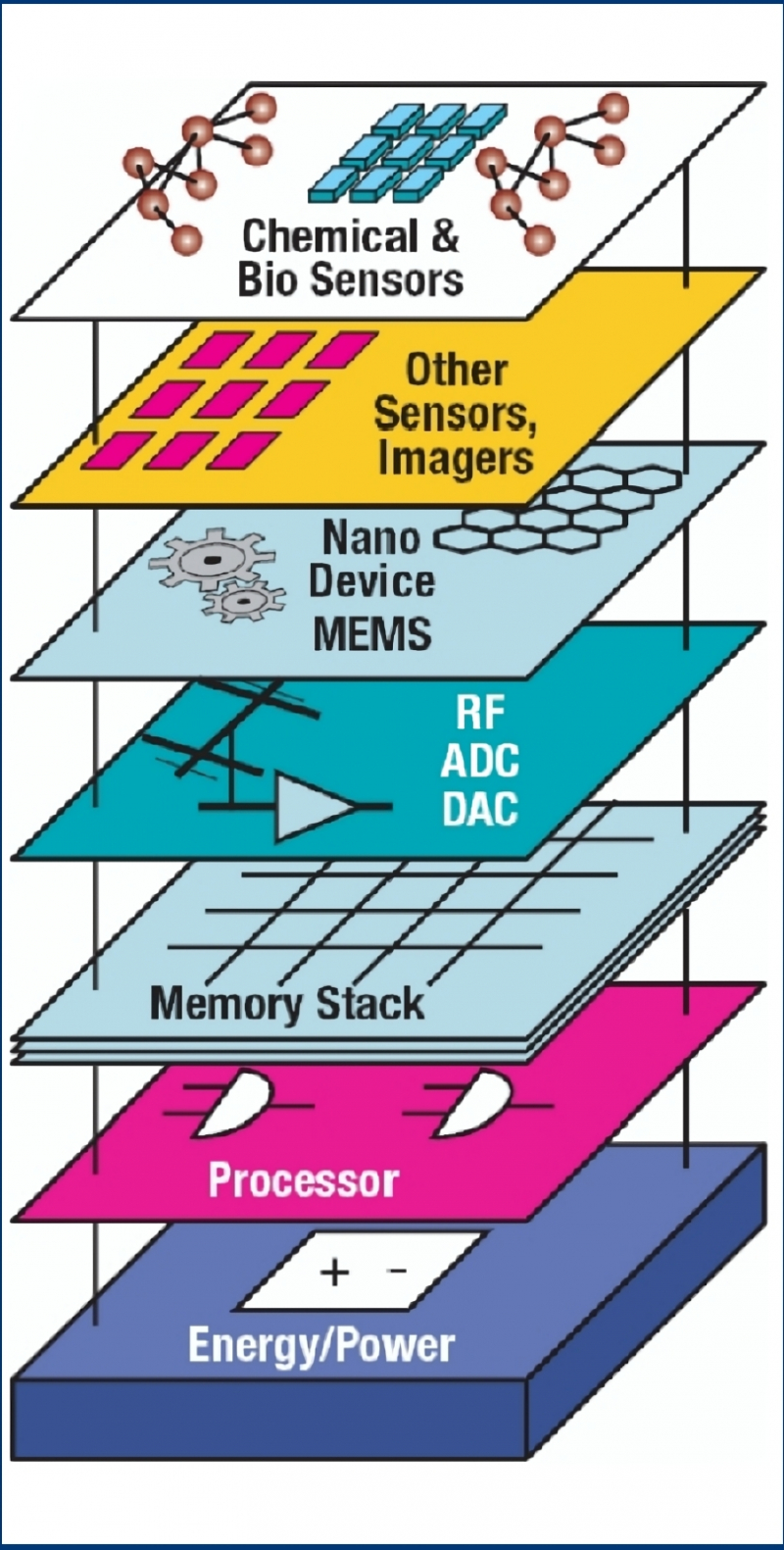

Схематическое изображение медных токоведущих структур, формируемых в теле современной СБИС методом CMP: под локальными межсоединениями (local interconnects) подразумеваются контакты, формирующие и связывающие между собой отдельные логические элементы в структуре чипа; под глобальными — шины, ведущие к внешним контактам (источник: Lam Research) ⇡#Подступаясь к вертикали: способы организации контактов между микросхемамиПринципиальная ограниченность планарно-унитарного пути развития СБИС стала очевидной уже ближе к концу 1990-х, однако успехи коротковолновой фотолитографии — DUV, а затем и EUV — заметно продлили эпоху доминирования монолитных чипов. Тем не менее с середины первого десятилетия 2000-х инженеры стали активно искать способы оптимального выхода в третье измерение — причём поначалу вовсе не для того, чтобы за счёт разделения цельной микросхемы на чиплеты и вертикальной их укладки сэкономить на занимаемой полупроводниковым изделием площади. Перспективной целью в данном случае была (и, кстати, во многом остаётся до сих пор) трёхмерная гиперинтеграция систем инфотеха, нанотеха и биотеха в некие универсальные метаустройства — своего рода элементы грядущего, подлинного Интернета вещей. Вещей, действительно заслуживающих называться умными, — а не нынешних кофеварок со встроенными модулями Wi-Fi или датчиков водопроводных протечек с адаптерами 5G, которые и без интеграции в связную комплексную систему прекрасно справляются со своими основным задачами.

Один из возможных вариантов многоуровневой компоновки 3D-гиперинтегрированного метаустройства (источник: Rensselaer Polytechnic Institute) Перспективные метаустройства будут, как уверены устремлённые в будущее инженеры, содержать в предельно миниатюрном объёме все необходимые для автономной работы компоненты: источник питания, вычислительные мощности, ячейки постоянной и оперативной памяти, антенны и усилительные контуры для радиосвязи, микро- или даже наноэлектромеханические агрегаты (Micro-Electro-Mechanical Systems, MEMS — крохотные актуаторы, манипуляторы и тому подобное), физические датчики (оптические, акустические или другие), а также химические и биологические сенсоры, реагирующие на ничтожные количества определённых веществ, вплоть до отдельных молекул. Для создания подобных микрогаджетов вертикальная упаковка образующих их элементов подходит идеально: именно таким образом удастся минимизировать габариты, не поступаясь функциональностью. Кроме того, предельно плотное размещение составляющих метаустройство частей существенно сократит энергопотери — а ещё упростит и удешевит монтаж (при налаживании массового серийного производства, ясное дело). Если учесть стремительно растущие сегодня возможности машинного обучения и искусственного интеллекта, рои таких агрегатов — не стоит забывать о MEMS, реализующих возможность перемещения в пространстве, — действительно смогут образовывать нечто вроде давно предсказанной фантастами «умной пыли». Правда, пока это более футурологическая, нежели прикладная инженерная тема.

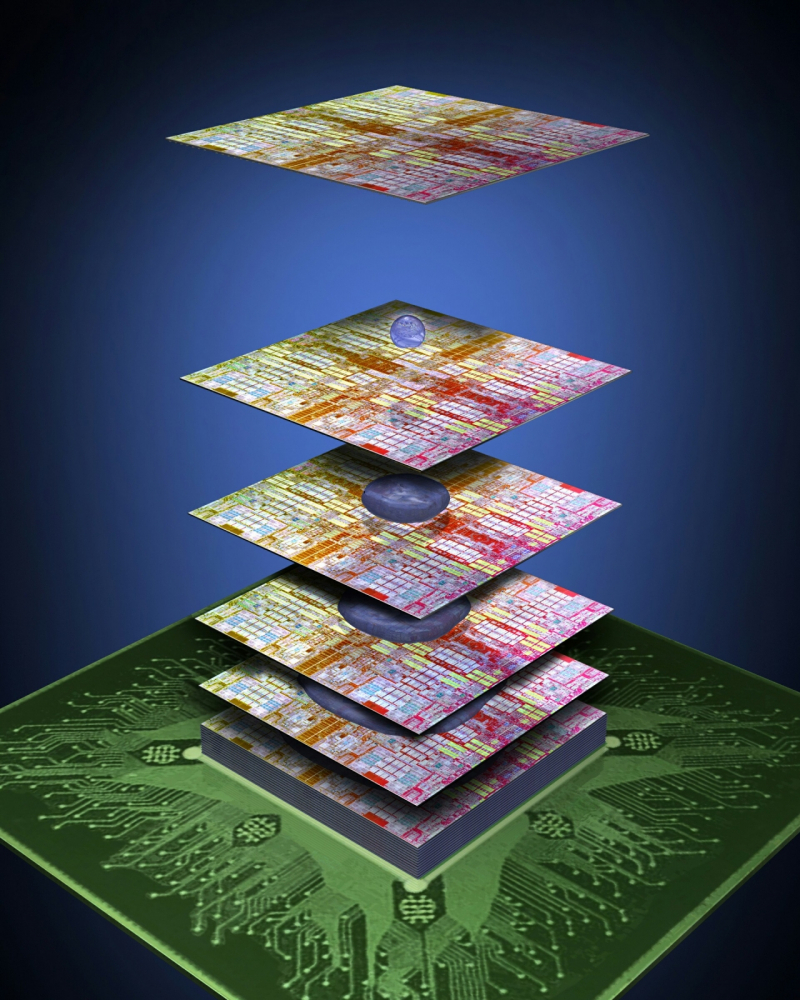

Проект вертикально интегрированного 3D-чипа, представленный Globalfoundries ещё в 2012 г. (источник: ATIC) Главное же в данном случае то, что окрылённые перспективами метаустройств разработчики полупроводниковых систем принялись активно осваивать трёхмерную упаковку чипов. Для начала хотя бы в два этажа: внизу микросхема, производящая логические вычисления, над ней — ячейки памяти. Сделать это оказалось технически не слишком сложно, поскольку в обычных электронных устройствах процессоры и память всё равно разнесены между собой физически и связаны идущими по монтажной плате шинами данных. Достаточно было всего лишь положить один полупроводниковый кристалл на другой и соответствующим образом соединить их. Для начала — даже не напрямую между собой, а с контроллером, так и оставшимся на исходной плате. Правда, такой безыскусный (и самый ранний) способ вертикализации чипов, получивший название упаковки с проводными соединениями (wire-bonded die package), оказался не слишком практичным.

Прямолинейное соединение внешней шиной двух обособленных чиплетов (или даже самостоятельных чипов) через внешний контроллер, die-to-die package (источник: Rensselaer Polytechnic Institute) Тонкие контактные шины оказывались слишком хрупкими — и от малейшего повреждения прижимались друг к дружке, что сразу же вело к коротким замыканиям. Или же они нуждались в дополнительном усилении и изоляции, что удорожало и усложняло конструкцию. К тому же сами микросхемы требовалось отделять одну от другой изолирующими прокладками, а затем каким-то образом этот сэндвич скреплять воедино. Словом, экономия занимаемой площади практически полностью компенсировалась дополнительными затратами на едва ли не ручную упаковку каждой такой СБИС по отдельности. Тем не менее в версиях SiP (system-in-package, когда одна микросхема помещается на другую параллельным переносом) и PoP (package-on-package, когда второй чип, соединённый плоской шиной с первым, словно бы приподнимают и укладывают на тот вверх тормашками, так что соединительные линии лишь загибаются, почти не вытягиваясь в длину) упаковка с проводными соединениями активно применяется до сих пор разработчиками мобильных телефонов, медиаплееров и иных компактных гаджетов.

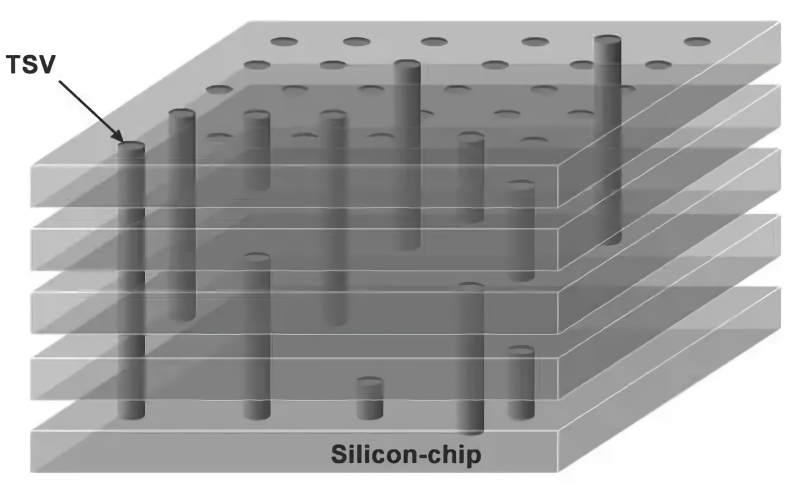

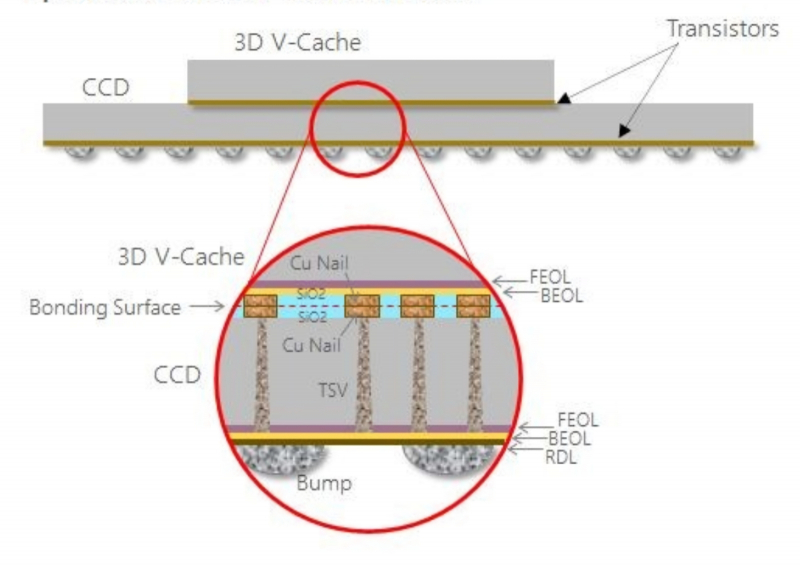

Пилоны TSV прошивают вертикально скомпонованные чиплеты, объединяя разнесённые в пространстве логические контуры в одну схему (источник: Toshiba Memory Corporation) Следующим резонным шагом стал отказ от соединений, выходящих за контуры чипов, и переход к TSV (through-silicon-via) — контактам, проходящим прямо сквозь кремний. На схеме сквозные контакты, проходящие через несколько уложенных стопкой микросхем, выглядят простым и логичным решением. Однако проделать отверстия точно в нужных местах (прожечь лазером либо удалить материал глубоким реактивным ионным травлением — deep reactive ion etching), а затем аккуратно заполнить медью, сформировав микроскопические проводящие структуры строго заданных характеристик, — задача далеко не тривиальная. Так или иначе, решать её к настоящему времени инженеры успешно научились. Представленные в 2021 году на тайбэйской выставке Computex чипы AMD архитектуры Zen 3 снабжены уложенной поверх основного полупроводникового кристалла микросхемой дополнительной кеш-памяти — 3D Vertical Cache. Логически эта микросхема ёмкостью 64 Мбайт выступает частью процессорного кеша третьего уровня (L3), так что суммарный объём L3 для 8-ядерного модуля Zen 3 составляет 96 Мбайт, а для составленного из пары таких модулей 16-ядерного процессора — 192 Мбайт.

Чиплет 3D Vertical Cache соединяется с подлежащим ЦП семейства Zen 3 не микроконтактами-зернью (bumps), а ещё более миниатюрными медными скрепами (bonds), венчающими пилоны TSV, которые идут от слоя транзисторов процессора к самой верхней его границе (источник: AMD) Здесь важно отметить, что с точки зрения BIOS, OS и прикладных программ 3D Vertical Cache не оказывается неким дополнительным участком памяти (условным «кешем четвёртого уровня»), а органично расширяет доступную ёмкость L3. Эта микросхема SRAM размерами 6 × 6 мм выполняется по тому же «7-нм» техпроцессу, что и основной кристалл данного ЦП, и располагают её над тем участком процессора, который отведён под интегрированный 32-Мбайт кеш третьего уровня. В данном случае одной соединительной шиной в десятки или даже сотни линий не обойтись: чтобы обеспечить подлинно бесшовную интеграцию с бортовым L3-кешем процессора, 3D Vertical Cache и базовый чип связывают воедино около 23 тыс. шурфов TSV. ⇡#Гетерогенность — это хорошо: как совмещать разные микросхемыИзбирательное позиционирование дополнительных микросхем над основной — процедура довольно затратная как по времени и прилагаемым усилиям, так и по себестоимости. Если каждый образующий метаустройства слой придётся укладывать поверх предыдущего в рамках особой для каждого такого гаджета процедуры, то вряд ли когда-то удастся приступить к их массовому производству. С прицелом на упрощение и удешевление трёхмерной компоновки полупроводниковых кристаллов в последние годы чипмейкеры направляют немалые инвестиции в развитие прямых гибридных соединений; в частности — между целыми кремниевыми пластинами, wafer-to-wafer direct hybrid bonding (W2W).

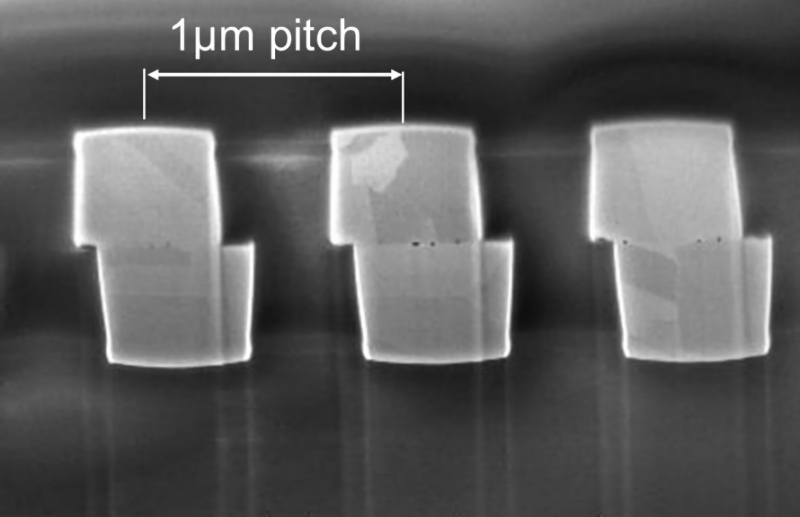

Автоматизированные системы для изготовления 3D-чипов GEMINI FB XT обеспечивают уверенное сопряжение двух 300-мм пластин так, что медные скрепы (bonds) с характерным шагом 1 мкм соединяются с высочайшей точностью (источник: Leti) Ещё в 2017 г. EVG и Leti произвели первое в мире успешное соединение двух 300-мм пластин с литографированными на них чипами. При этом успешно сопрягались — образуя надёжные проводники, которые связывают полупроводниковые структуры на двух пластинах, — группы медных контактов с характерным расстоянием между соседними (pitch) от 1 до 4 мкм. Общая точность выравнивания (доверительный интервал 3σ) достигла 195 нм. Это, напомним, для двух наложенных одна на другую вполне макроскопических — 300-мм в диаметре — пластин! Достижение вполне выдающееся, но во многих случаях именно гибридное вертикальное соединение чиплетов подразумевает, что они могут изготавливаться по существенно различным техпроцессам — и на пластинах разных диаметров. Кроме того, технология W2W позволяет соединять «лицом к лицу» лишь две пластины с соответствующим образом сопрягаемыми выходными контактами BEOL. Третий и последующие уровни вертикализации придётся, если возникнет такая необходимость, сопрягать с этим «сэндвичем» уже каким-то иным способом.

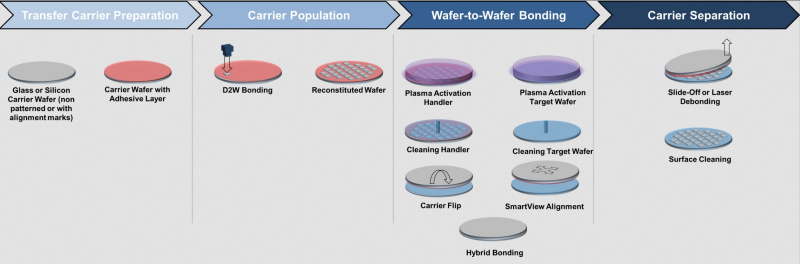

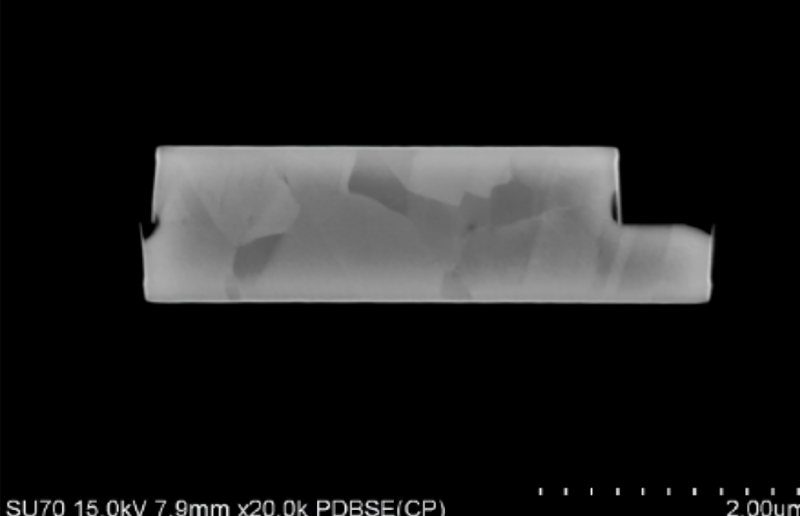

Установка для скрепления пластин по технологии W2W немногим уступает по габаритам DUV-литографам (источник: Leti) Если исходить из этих соображений, прямые гибридные соединения представляются более перспективными в формате не W2W, а D2W — die-to-wafer, когда на подготовленную пластину с первым слоем будущих чиплетов помещаются вторым уровнем уже предварительно нарезанные из другой пластины (не обязательно того же самого диаметра) полупроводниковые кристаллы. Таким образом появляется возможность изготавливать составные чипы гетерогенными, что и требуется для создания метаустройств. Основные направления D2W, разрабатываемые и уже находящие применение сегодня, — это Co-D2W (collective die-to-wafer) и DP-D2W (direct placement die-to-wafer). Групповое соединение чиплетов с пластинами, Co-D2W, предусматривает автоматизированную прецизионную установку подготовленных заранее чиплетов второго уровня на пластину-носитель (handler). После дополнительной обработки и очистки носитель переворачивается, пластина-мишень выравнивается и производится их соединение «лицом к лицу» — примерно с теми же параметрами точности, что в случае прямого W2W-процесса. Затем остаётся лишь отделить пластину-носитель от получившейся гибридной заготовки — и далее обрабатывать и разрезать последнюю на отдельные чипы уже стандартными методами.

Общая схема процедуры D2W: подготовка промежуточной пластины-носителя — размещение на ней предназначенных к вертикальному сопряжению чиплетов — собственно процесс скрепления (bonding) двух пластин-заготовок, основной и носителя — отделение носителя и его очистка для повторного применения (источник: 3DInCites) Технология Co-D2W применяется достаточно давно и хорошо отлажена. Её недостатками считаются достаточно высокий уровень погрешностей (прежде всего вследствие не всегда точного размещения нарезанных чиплетов на нежёстком адгезивном слое пластины-носителя), значительная себестоимость подготовки и очистки этой пластины, которая используется многократно, а самое главное — существенное ограничение по толщине перемещаемых носителем чиплетов. Иными словами, последовательно составлять по-настоящему многослойные метаустройства таким образом не выйдет: предел возможностей Co-D2W — расширение процессорной кеш-памяти в третье измерение или сопряжение оптического датчика с обрабатывающей формируемый им сигнал электроникой.

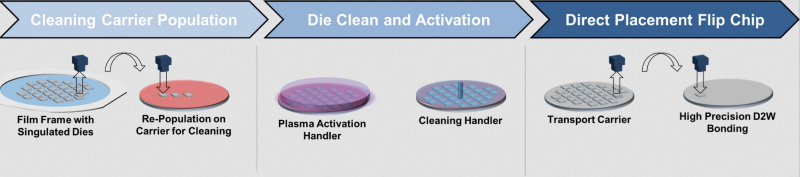

Технология DP-D2W: чиплеты размещаются на носителе — производится общая обработка и подготовка поверхностей к сопряжению — чиплеты переносятся на основную пластину по отдельности (источник: 3DInCites) Гораздо больше надежд инженеры-микроэлектронщики возлагают на технологию прямого размещения чиплетов на пластине-мишени, DP-D2W. Вместо того чтобы аккуратно наклеивать разрезанные полупроводниковые кристаллы на пластину-носитель, а затем переворачивать её целиком для совмещения с мишенью, в данном случае поднимают и переворачивают каждый чиплет (будущего второго уровня составной микросхемы) по отдельности, один за другим помещая их на нужные позиции. По-английски эта процедура описывается как «pick-and-place flip-chip». Принципиальные ограничения на высоту чиплетов при этом по сути отсутствуют — и это огромное преимущество данного метода. Основная же сложность тут заключается как раз в том, что переносящему и переворачивающему чиплеты инструменту необходимо соприкасаться с той стороной полупроводникового кристалла (точнее, верхним слоем его BEOL-структуры), которая сразу после этого будет совмещаться с ответными контактами на пластине-мишени. Малейшие механические повреждения этой поверхности или попадание на неё микроскопических пылинок, увы, практически гарантируют неработоспособность полученного составного чипа.

Микрофотография поперечного среза соединённых процессом DP-D2W скреп верхнего и нижнего чиплетов наглядно подтверждает прочность образовавшейся связи: прямо сквозь контактный стык проросли кристаллические зёрна меди — структура соединения фактически сделалась монолитной (источник: 3DInCites) А избежать захвата прямым контактом технологически невозможно — по крайней мере пока: чиплеты слишком тонки и хрупки, чтобы на нынешнем уровне развития технологий удавалось подцеплять их, не повреждая, захватами роботизированного манипулятора за края. Для плоскопараллельного же бережного переноса множества крохотных СБИС разом отлично подходит метод микротрансферной печати (micro-transfer-printing, µTP) с изготовлением штемпеля из особого эластомера. Поскольку подхват и удержание чиплетов происходит за счёт одних только ван-дер-ваальсовых сил межмолекулярного притяжения, никаких дополнительных химикатов (и их последующего удаления) тут не требуется, что ускоряет процесс и снижает его себестоимость. Но переворачивать таким образом отдельные полупроводниковые кристаллы ещё не научились — для совершенствования технологии DP-D2W придётся искать особые пути. ⇡#Без отрыва от производстваРассмотренные выше технологии изготовления многослойных составных микросхем объединяет их ориентация на комбинирование тем или иным способом уже выполненных по отдельности чиплетов. Однако современные инженерные достижения позволяют всерьёз рассматривать возможность последовательного создания существенно многоуровневых чипов — то есть больше чем с одним уровнем транзисторов — на общей пластине-заготовке. И если такие проекты будут доведены до массовой серийной реализации, это позволит значительно приблизить эру «умной пыли» — будем надеяться, без тех отрицательных её аспектов, которые приходится героически преодолевать персонажам киберпанковских романов.

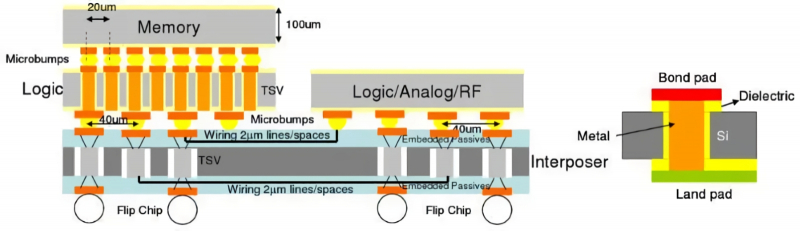

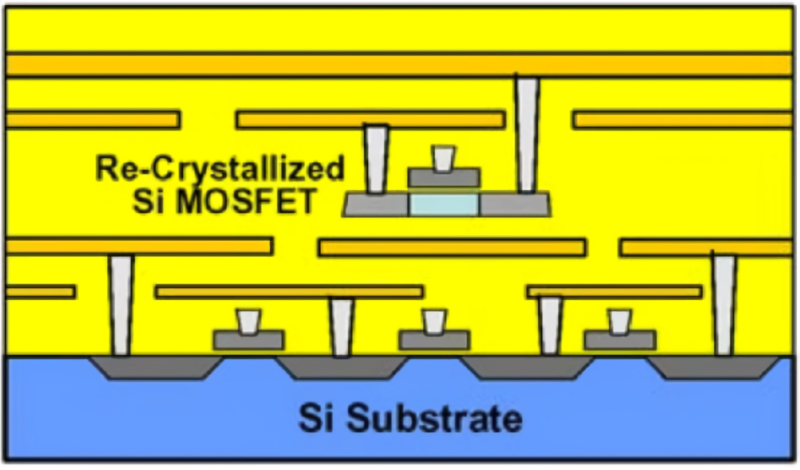

Различные типы соединений в гетерогенных интегрированных чипах: контакт «лицом к лицу» (flip chip) через достаточно крупную зернь внизу, выше промежуточный слой (interposer) с TSV-пилонами и горизонтальными шинами (2 мкм — характерный шаг их токоведущих дорожек), ещё выше логические и аналоговые чиплеты на микрозерни с шагом контактов 40 мкм, третьим слоем — память на 20-мкм микрозерни (источник: Veeco Instruments) По сути, разница между монолитными и вертикально-составными чипами с технической точки зрения уже сегодня не слишком велика. Шурфы TSV-соединений пронзают микросхемы, соединяя разрозненные чиплеты, — но ведь и внутри каждой из этих малых СБИС присутствуют те же самые TSV-каналы, разве что иных протяжённостей и сечений. Постепенно размываются границы между отдельной микросхемой, системной платой для монтажа нескольких таких микросхем (вспомним, как соединены через промежуточный слой — interposer — чиплеты в плоской 2,5D-упаковке) и готовым полупроводниковым прибором в целом (система-на-кристалле уже давно не редкость; теперь же речь идёт о системах на множестве сопряжённых кристаллов). Следующим логичным шагом может стать процесс — точнее, целое семейство разнородных инженерных методик, — называемый wafer-level transistor build-up, создание транзисторов на уровне заготовки. Так, уже почти десятилетие назад было предложено формировать отдельные транзисторы или их группы прямо в слоях металлизации над кремниевой пластиной-заготовкой — точнее, в промежуточных диэлектрических уровнях, отделяющих один слой металла в составе BEOL-структуры от другого.

Технически ничто не мешает формировать транзисторы на промежуточных уровнях современных чипов между слоями металлизации — вопрос лишь в себестоимости значительно усложняющегося чипмейкерского процесса (источник: Rensselaer Polytechnic Institute) Для этого на диэлектрик наносится небольшая порция аморфного кремния вместе с катализатором. Под воздействием высокой температуры (лазерного нагрева, например) образуется микроучасток кристаллического кремния, и далее на нём можно формировать транзисторы стандартным образом: создавать зоны с избытком электронов и дырок, организовывать затворы и так далее. Поскольку процедуры эти будут проводиться в BEOL-структуре, технологический процесс здесь не должен быть сверхминиатюрным, что упрощает и удешевляет изготовление подлинно гетерогенного полупроводникового прибора.

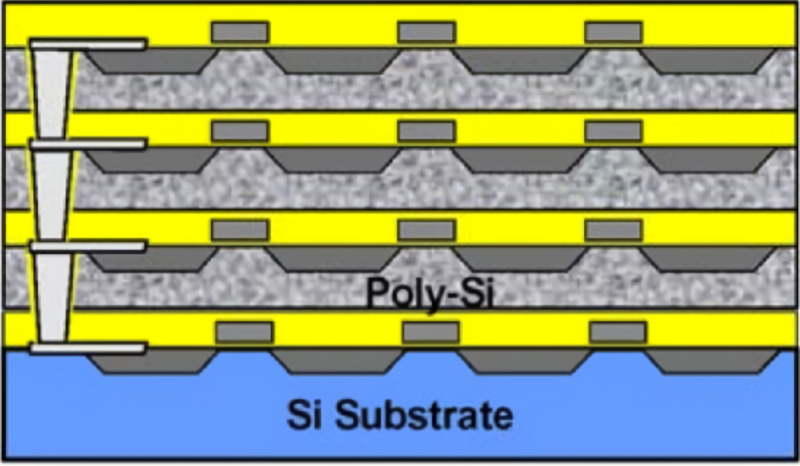

Поликремний и вольфрам — вот всё, что нужно для формирования монолитных многослойных (в смысле множества транзисторных слоёв) гиперинтегрированных чипов (источник: Rensselaer Polytechnic Institute) Если нужно получить по-настоящему много транзисторов в вышележащих слоях, базовые полупроводниковые структуры можно формировать на поликремниевых плёнках, электрически связываемых по вертикали вольфрамовыми пилонами. После стандартной обработки поверхности заготовки и формирования FEOL-слоёв с тем, чтобы получить работоспособные полупроводниковые устройства на самом нижнем уровне, на пластину помещают плёнку из аморфного кремния — и опять-таки путём нагрева кристаллизуют её, получая тем самым привычное основание для нового цикла чипмейкерских процедур. Именно вольфрамовые соединения между слоями требуются здесь потому, что выполненные из этого металла сверхтонкие проводники выдерживают, не теряя своих свойств, нагрев примерно до 600 °С. Как раз такой метод создания многослойных чипов полупостоянной памяти применялся ещё в начале 2000-х для изготовления недорогих и ёмких (512 Мбит), но зато достаточно медленных (1 Мбайт/с чтение, 0,5 Мбайт/с запись) микросхем PROM-памяти. Для получения же более скоростной многослойной памяти разновидностей SRAM и NAND применяют несколько иной подход: в дело идут плёнки из монокристаллического кремния.

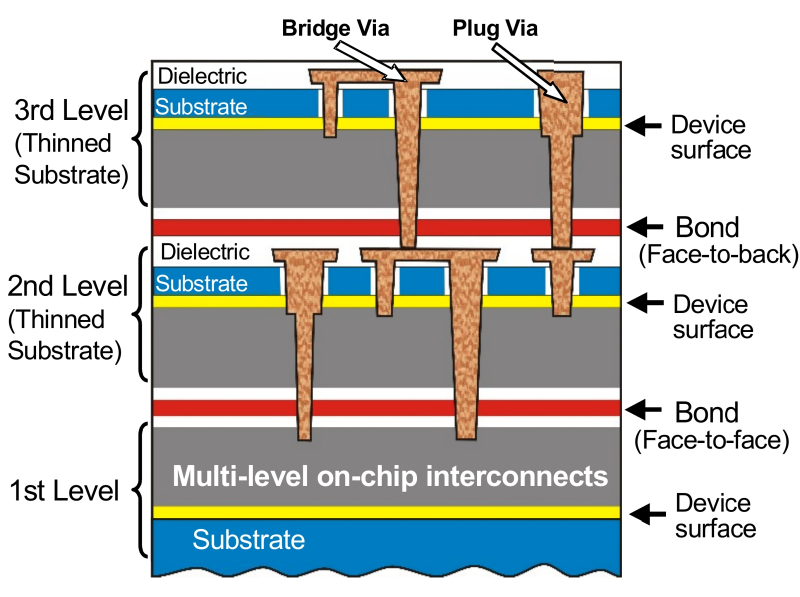

Схема монолитной 3D-гиперинтегрированной СБИС, сочетающей различные типы адгезивной стыковки чиплетов (face-to-face, face-to-back), а также вольфрамовые пилоны и мосты TSV (источник: Rensselaer Polytechnic Institute) Трёхмерная BEOL-совместимая гиперинтеграция на уровне заготовок (wafer-level BEOL-compatible 3-D hyperintegration) подразумевает создание многослойных гетерогенных микросхем буквально за один производственный цикл — правда, с последовательной дозагрузкой в литограф всё новых пластин. BEOL-совместимость означает организацию взаимодействия между логическими контурами в разных слоях, что действительно позволит превратить получаемую в итоге микросхему в органично цельное полупроводниковое метаустройство. Правда, невзирая на то, что активные разработки в этой области ведутся с начала 2000-х, основным путем развития микроэлектроники она покуда не сделалась — за исключением, пожалуй, многослойной памяти, в особенности NAND. К примеру, в середине 2021 г. сингапурский Институт микроэлектроники с триумфом сообщил о таком замечательном достижении в области создания 3D-чипов, как изготовление четырёхслойной микросхемы. По сути, исследователи взяли два двуслойных чипа с расположением транзисторных слоёв «лицом к лицу» (точнее, BEOL к BEOL), сложили их вместе «спина к спине» и проделали TSV-шурфы, сквозь которые проложили медные контакты для взаимной увязки логических контуров всех четырёх СБИС.

Микрофотография поперечного среза TSV, соединяющих логический чип (внизу) с чиплетом кеш-памяти SRAM (источник: Intel) Причина столь скромных успехов микропроцессорных 3D-технологий довольно проста: планарные чиплеты — в крайнем случае размещаемые вторым слоем над логическими микросхемами чипы памяти — проще охлаждать. Поскольку главная цель любых чипмейкерских усовершенствований — повышение производительности СБИС (либо абсолютной, либо в пересчёте на ватт потребляемой мощности), существенно вертикальные конструкции продолжают уступать двумерным и 2,5D-сборкам именно по параметру эффективности теплоотвода под высокими нагрузками. Инженеры усердно трудятся над этой проблемой, но признают, что прорывное решение отыскать пока не удалось. При охлаждении компактных, но всё же макроскопических объектов — таких как лопатки турбин или стенки камер сгорания реактивных двигателей, например, — неплохо зарекомендовали себя микроканалы, по которым циркулирует теплоноситель. Но современные чипы настолько миниатюрны, что прошивать их (помимо шурфов TSV) ещё и каналами для прокачки охлаждающей жидкости — значит дополнительно сокращать площадь, занимаемую в каждом слое транзисторами и металлическими шинами.

Сравнительные размеры микрозерни (короткие толстенькие столбики в верхней левой четверти снимка) и пилонов TSV (тонкие вертикальные линии в центральном поясе) в чипе архитектуры Ponte Vecchio. Горизонтальная светлая полоса правее ряда TSV — кремниевый мост, соединяющий данный базовый чиплет с соседним (источник: Intel) Кроме того, сделать эти каналы совсем уж тонкими тоже не выйдет: жидкий хладагент обладает ненулевым поверхностным натяжением, и сквозь чрезмерно узкие капилляры он попросту не пойдёт. Использовать же, к примеру, сверхтекучий жидкий гелий — значит охлаждать всю систему до таких низких температур, на нормальную работу при которых традиционные полупроводниковые приборы никак не рассчитаны. Нельзя сбрасывать со счетов и другие вызовы, не имеющие отношения к чисто температурным. Скажем, необходимо при серийном массовом производстве рутинно и быстро совмещать крупные пластины-заготовки с точностью менее 1 мкм. Или обеспечить высокую механическую прочность существенно вытянутых TSV — с отношением высоты к диаметру 5:1 и более, что при таких ничтожных габаритах становится непростой задачей даже для вольфрама. Тем не менее одно остаётся непреложным: на пути дальнейшего наращивания производительности полупроводниковых СБИС миниатюризация технологического процесса их изготовления с каждым очередным шагом в сторону единиц ангстремов представляется более затратной (во всех смыслах), чем укорочение соединяющих эти чипы (равно как и чиплеты) проводников и наращивание плотности образуемых ими контактов. Уже простейшее сопряжение двух чиплетов «лицом к лицу» обеспечивает плотность контактов на уровне тысяч единиц на квадратный миллиметр, что значительно снижает задержки при прохождении сигналов по сравнению с показателями самых изощрённых шин 2,5D-соединений.

В 2020 г. TSMC представила фирменную технологию вертикальной упаковки чипов CoWoS-S, при помощи которой рассчитывала в среднесрочной перспективе освоить 12-слойную упаковку чиплетов памяти HBM (каждый слой — не более 50 мкм толщиной) с TSV и пассивным теплоотводом. Реалии последних лет внесли свои коррективы, но — надежда остаётся! (Источник: TSMC) А значит, дорога в третье измерение будет осилена, насколько бы сложным ни оказалось восхождение. На этом пути инженерам придётся, напомним, решить три важнейших вопроса:

Серьёзнейшее внимание, уделяемое сегодня машинному обучению и технологиям искусственного интеллекта, напрямую способствует продвижению микроэлектронной индустрии в сторону трёхмерной упаковки полупроводниковых логических элементов. Ведь в такого рода чипах пути коммуникаций между соседними транзисторами оказываются короче (по сравнению с плоской микросхемой с тех же числом базовых элементов) — и, стало быть, напрямую зависящие от скорости прохождения сигнала внутри схемы нейроморфные вычисления будут производиться быстрее. Вертикализация полупроводниковых технологий существенно важна для искусственного разума — быть может, инженерам стоит обратиться к нему (в лице популярного сегодня ChatGPT, скажем) за светлыми идеями?

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|