⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

От плавников к кольцам и далее к КМОП: перипетии транзисторной эволюции

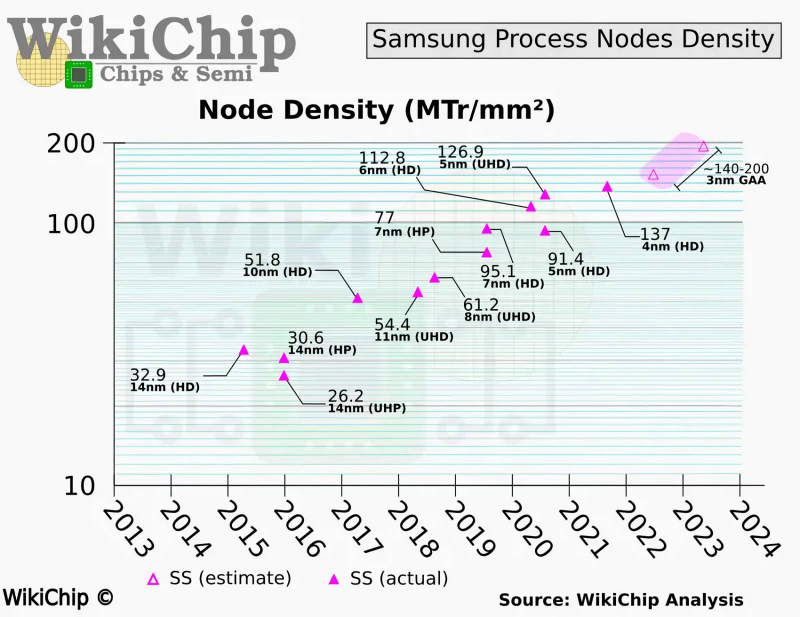

Летом 2022 г. полупроводниковое подразделение Samsung Electronics отчиталось о начале серийного выпуска микросхем по «3-нм» техпроцессу, отличительной чертой которого было названо изготовление передовых GAAFET-транзисторов на кремниевой подложке по собственной технологии нанолистов (nanosheets), которая, как утверждается, превосходит более раннюю концепцию нанопроволочек (nanowires), поскольку обеспечивает бóльшую площадь канала для пропуска электрического заряда в транзисторе. При этом TSMC, на сегодня бесспорный лидер по объёмам изготавливаемых для заказчиков «3-нм» СБИС, продолжает делать ставку на «гребенчатые», или «плавниковые», транзисторы прежнего поколения, FinFET, рассматривая возможность освоения GAAFET не ранее 2025 г. Да и Intel намеревается перейти на фирменную «ленточную» — RibbonFET — реализацию GAA-подхода в транзистростроении не ранее второй половины 2024 г., начиная лишь с техпроцесса «Intel 20A». А в чём, собственно, разница — и почему конечного пользователя в принципе должно беспокоить, что за транзисторы располагаются у очередного процессора под капотом, точнее, под корпусной крышкой?

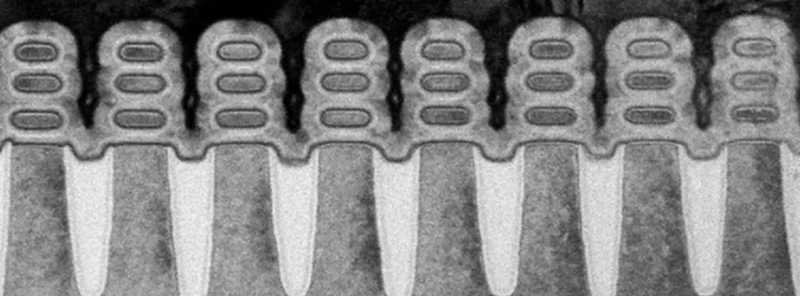

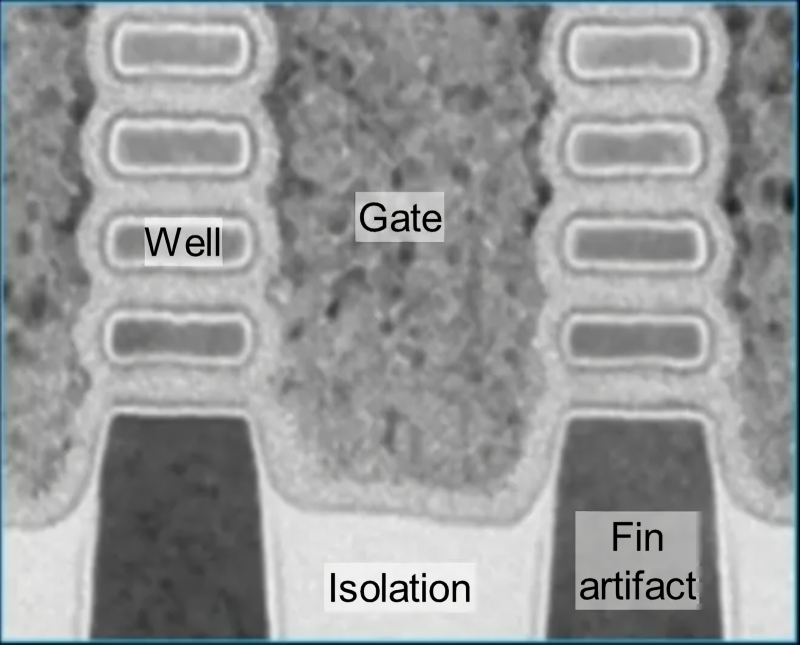

Поперечный (поперёк плавников, вдоль охватывающего их затвора) срез литографированного чипа с транзисторами GAAFET (источник: IBM) ⇡#Поднять плавники!Базовый элемент современной полупроводниковой вычислительной техники, своего рода «атом» любой микропроцессорной структуры, — полевой транзистор с изолированным затвором, он же МОП-транзистор. Название это (MOSFET, metal-oxide-semiconductor field-effect transistor) происходит от прямого указания на химсостав структурных компонентов конструкции самых первых устройств такого рода: затвор их выполнялся из металла, основу (в толще которой формируется канал перетока электрического заряда) составлял полупроводник, а между двумя этими элементами располагался тонкий изолирующий слой диэлектрика — обычно оксида кремния. Мы довольно подробно разбирали ранее принцип действия МОП-транзистора и обусловленные его физическими свойствами сложности с миниатюризацией полупроводниковых систем. Суть в том, что в составе транзистора образуется канал, по которому перемещается электрический заряд от истока к стоку, — а управление тем, открыт этот канал или закрыт, осуществляет затвор. Классическая конструкция МОП-транзистора предусматривает планарное, т. е. с прилеганием к одной и той же условной плоскости (по разные стороны от неё), размещение канала и затвора. И пока физические габариты элементов транзистора были достаточно велики в сравнении с размерами одиночного атома — а именно атомы кремния и иных схожих по структуре материалов с нехваткой или избытком электронов на внешних оболочках, напомним, ответственны за проявление особых свойств полупроводников, на которых построена почти вся современная микроэлектроника, — всё было достаточно просто: безыскусная миниатюризация техпроцесса изготовления этих самых МОП-транзисторов вела к повышению быстродействия всей построенной на них микросхемы. Хотя бы потому, что чем короче канал, тем за меньшее время преодолеют его носители заряда, двигаясь под воздействием имеющейся между истоком и стоком разности потенциалов.

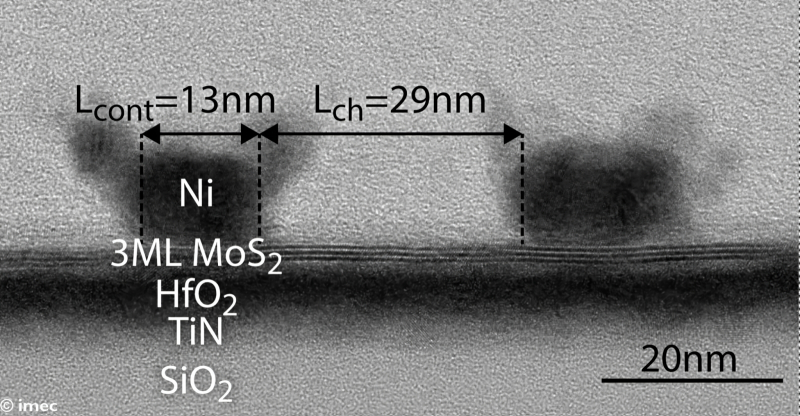

Планарный транзистор на основе трёхслойной плёнки «двумерного» дисульфида молибдена (MoS2; каждый слой — толщиной буквально в одну молекулу) избавлен от многих эффектов короткого канала, свойственных кремниевым транзисторам (источник: IMEC) По достижении же каналом предела примерно в 90 нм из-за особенностей фотолитографической реализации истока и стока на кремниевой подложке начинают заметно давать о себе знать токи утечки, из-за которых даже при формально закрытом затворе через канал всё-таки может проходить электрический заряд, пусть и с меньшей, чем в состоянии «закрыто», интенсивностью. Существует целый набор факторов, известных как эффекты короткого канала (short-channel effects), которые способствуют понижению потенциального барьера (того самого, что препятствует прохождению заряда в канале при закрытом затворе) под воздействием утечек. В частности, при активном затворе вокруг истока и стока заряда — которые при фотолитографическом методе изготовления полупроводниковых структур представляют собой участки с проводимостью n-типа, внедрённые в базу с проводимостью p-типа, — возникают обеднённые отрицательными зарядами области (depletion zones), которые эффективно сокращают рабочую протяжённость контролируемого затвором канала. И как только обеднённые зоны по обоим берегам канала смыкаются, закрытие затвора (снятие с него управляющего напряжения) уже не приводит к приостановке переноса заряда через транзистор: роль альтернативного канала исполняют те самые соединившиеся обеднённые области. Происходит это как раз при длине канала примерно в 25-28 нм. Да, с такими эффектами в принципе можно бороться на электрохимическом, что называется, уровне, применяя вместо легированного различными примесями кремния другие материалы, прокладывая между кремниевой основой и собственно транзистором изолирующий слой, который препятствует образованию обеднённых зон (метод silicon-on-insulator, SOI), и пр. Но и технологические процессы при этом необходимы несколько иные, особенно в случае массового поточного производства, — что грозит удорожанием получаемых таким образом микросхем до решительно неприемлемых значений. Ещё один крайне неприятный момент: при чрезмерном уменьшении длины канала начинает проявлять себя неравномерность распределения легирующих атомов. Легирование полупроводника, напомним, осуществляется крайне небольшими дозами примесей — примерно один-два дополнительных атома на десять миллионов атомов кремния, — так что на участке протяжённостью в 20-30 нм и сопоставимой ширины может попасться 2-3 легирующих атома, а может и 5-6, что приведёт к заметному различию свойств соседних транзисторов в составе чипа. Различия эти придётся компенсировать повышением рабочего напряжения в пределах всей микросхемы, что грозит нивелировать преимущество более миниатюрного техпроцесса по части энергоэффективности.

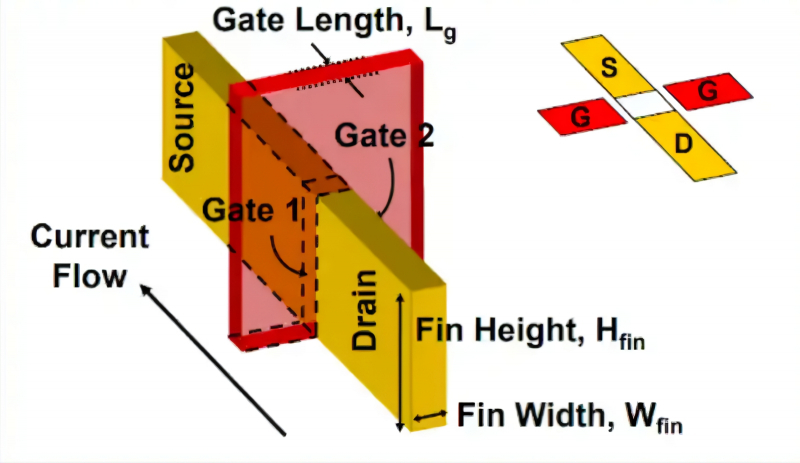

Основные элементы плавникового транзистора: исток и сток (source/drain) и вытянутые благодаря гребню зоны соприкосновения с затвором (gate1, 2) (источник: SiliconVLSI) В 2009 г. на очередной Конференции разработчиков Intel продемонстрировала кремниевую пластину, литографированную по «22-нм» технологическому процессу, причём микросхемы на ней были образованы не классическими планарными, а «плавниковыми», или «гребенчатыми», транзисторами — FinFET. Тогда же было заявлено, что уже через два года на рынок выйдут созданные по тому же принципу серийные процессоры, — и компания сдержала слово: выпущенные в 2011-м ЦП семейства Ivy Bridge действительно первыми в истории компании базировались на «трёхзатворных», или «объёмных», транзисторах FinFET. Эти образные наименования — tri-gate, 3D — подчёркивают главное отличие нового типа транзисторов от планарных: пропускающий заряд канал в случае FinFET — уже не короткий участок полупроводника прямо под затвором, но сразу три участка. Из-за новой геометрии полупроводниковой основы, уже не плоской, а узкой и вытянутой вверх (в виде, собственно, плавника или гребня), и охватывающего её теперь с трёх сторон затвора, к прежнему условно горизонтальному участку канала прибавляются ещё два вертикальных — той же поперечной протяжённости, но значительно более вытянутых. При кажущейся простоте такого решения путь FinFET от ранней идеи до серийного производства оказался долгим. Не случайно сама Intel в 2011-м назвала переход на гребенчатые транзисторы самым радикальным сдвигом в полупроводниковых технологиях за последние полвека. Началось всё ещё в 1997-м, когда группа исследователей под руководством профессоров Чэньминя Ху (Chenming Hu), Джеффа Бокора (Jeff Bokor) и Сюйжэ Кинга Лю (Tsu-Jae King Liu) задалась вопросом о том, как наилучшим образом преодолеть описанный нами чуть выше физически обусловленный предел протяжённости канала классического планарного транзистора в 25 нм. В те времена, напомним, наиболее передовой из серийно применяемых для производства электроники техпроцессов обеспечивал детализацию около 250 нм, — что немало говорит о дальновидности поддержавшего это исследование знаменитого в ИТ-отрасли американского правительственного агентства DARPA. Позднее к работам по данному направлению подключились такие крупные ИТ-компании, как Intel, IBM, Texas Instruments, AMD, Motorola и UMC. Профессор Ху в 1999-м, когда группа обнародовала общую концепцию FinFET — справедливости ради укажем, что ещё в 1989 г. Дай Хисамото (Digh Hisamoto) с коллегами из Группы исследований и разработок Hitachi в Токио предложили схожую с FinFET структуру полупроводникового транзистора с двойным затвором, — так описывал его преимущество перед планарным транзистором: «Можно провести аналогию с кровеносным сосудом: если тот повреждён в результате ранения, самый действенный способ остановить кровь — сжать сосуд с двух сторон. Надавив только с одной стороны, добиться результата тоже возможно, но уже не так эффективно». Длинные узкие участки канала проводимости по обеим сторонам плавника гребенчатого транзистора обеспечивают значительно лучший контроль над токами утечки по всей площади трёхмерного (точнее, по-прежнему плоского, но расположенного теперь перпендикулярно плоскости пластины-заготовки) канала, — просто потому, что электронам становится буквально некуда бежать от электрического поля затвора в толще неширокого плавника. Уже в 2000-м учёные теоретически обосновали работоспособность FinFET-транзисторов вплоть до производственных норм «10 нм» — и, как мы видим сегодня, реальность заметно превзошла даже эти смелые оценки почти четвертьвековой давности. Поскольку участок полупроводника непосредственно под каналом у гребенчатого транзистора приподнят над общим основанием всей структуры, сильно вытянут и утончён, обеднённые отрицательными зарядами области под истоком и стоком уже не оказывают здесь того разрушительного воздействия, как в случае планарного транзистора, да и другие негативные эффекты короткого канала проявляются заметно слабее. Неудивительно, что на десятилетие вперёд полупроводниковые «атомы» именно типа FinFET стали индустриальным стандартом организации полупроводниковых систем: с минимальными вариациями транзисторы с плавниками внедрили на своих производствах все чипмейкеры планеты, дерзнувшие шагнуть за условный размерный порог «22 нм».

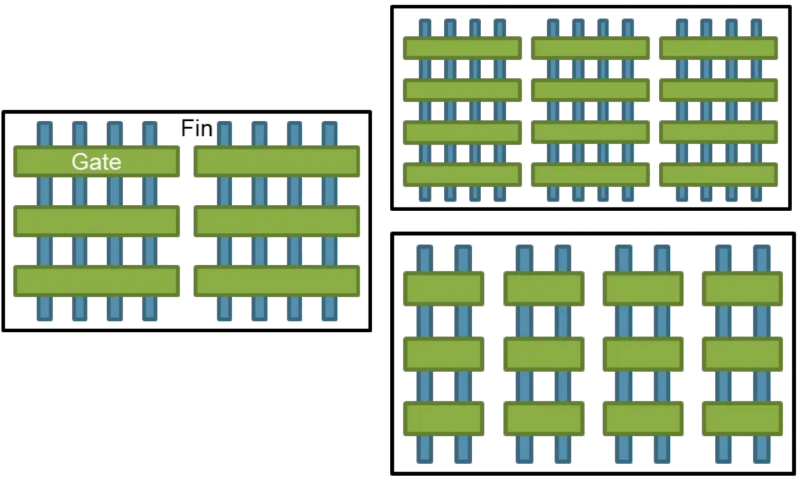

Наглядное представление разницы между FinFET-конструкцией в общем (слева; толщина слоя изоляции над вершиной гребня так велика, что полностью препятствует активированию соответствующего участка канала) и TrigateFET (источник: Princeton University) Кстати, строго говоря, термин FinFET относится к любым транзисторам с гребнями и по меньшей мере двумя затворными участками, расположенными по вертикали. Если толщина изолятора на вершине гребня слишком велика, конкретно этот узкий горизонтальный фрагмент канала работать не будет; вместо одного сплошного и изломанного в двух местах канала образуются два раздельных, — и вот тогда-то предложенная профессором Ху аналогия с пережиманием кровеносного сосуда с двух сторон оказывается полной. Intel же в 2011-м реализовала в серийном масштабе не просто гребенчатый транзистор, а трёхзатворный — Trigate FET, — поскольку толщина изолирующего слоя между плавником и обнимающим его затвором была выдержана одинаковой и по вертикали, и на узком горизонтальном участке. Однако для общего понимания сути дела это различие не принципиально, и потому мы будем понимать под FinFET любые разновидности гребенчатых транзисторов с неполным отделением «потенциального колодца» (на схемах обозначается как well; толща полупроводника, из которого изготовлен плавник) от основания, на котором транзистор выращивается в литографической установке. ⇡#В окруженииПоскольку затвор в случае FinFET охватывает тонкий плавник с трёх сторон, утечка заряда в толще гребня практически исключена, а значит, можно уменьшать управляющие транзистором токи, не опасаясь слишком малого различия между проводимостями канала в состояниях «затвор закрыт» и «затвор открыт». Это, в свою очередь, открывает дорогу к дальнейшей миниатюризации технологических процессов: в случае маленького транзистора снижается сила тока, что необходим для его активации, да и сама эта активация происходит быстрее за счёт увеличенной ширины канала, что позволяет одновременно перемещаться по нему значительному количеству электронов. По этой причине производительность более миниатюрного транзистора нового поколения (выраженная в отношении мощности, затраченной на его активацию, к пропускной способности канала проводимости) повышается достаточно ощутимо в сравнении с более крупным его предшественником. Пропускная способность (drive strength of the logic gate) — важная характеристика логической схемы, определяющая, насколько быстро рассматриваемый контур (в нашем случае единичный транзистор), получив некий входной сигнал, преобразует его в выходной. Для фиксированной производственной нормы («22 нм», «14 нм» и т. д.) длина (протяжённость) канала каждого транзистора от истока до стока — константа, и потому корректно утверждать, что чем больше ширина канала (а она для FinFET складывается из двух высот плавника и его толщины), тем лучше пропускная способность. Планарный транзистор можно, условно говоря, изготовить сколь угодно широким, чтобы повысить его пропускную способность, — правда, при этом будет он занимать очень много места на плоскости. Гребенчатый — дело другое: можно, во-первых, сделать его повыше, а во-вторых, охватить одним и тем же затвором сразу несколько плавников, формируя таким образом многогребенчатый FinFET. Отсюда, кстати, следует, что пропускная способность такого рода транзисторов квантуется: поскольку толщина гребня значительно меньше высоты, ею можно в первом приближении пренебречь, и тогда эффективная ширина многогребенчатого транзистора (и, как следствие, пропускная способность его канала) окажется прямо пропорциональна высоте единичного плавника. Необходимость иметь дело с (довольно крупными) квантами пропускной способности ограничивает свободу инженеров-микроэлектронщиков в плане балансировки электрических характеристик микросхемы в целом. Имеется в виду, в частности, невозможность снабдить часть транзисторов на одной и той же подложке чуть более широкими каналами (ради повышения производительности), а у других сделать каналы лишь несколько поуже (для снижения энергопотребления): в пределах выбранного техпроцесса остаётся оперировать только количеством гребней на процессор, без простора для более тонкой настройки. Зато для полупроводниковых FinFET-структур появляются сразу две новые возможности повышения плотности транзисторов на единицу площади — помимо линейного сокращения производственной нормы за счёт перехода ко всё более мелкомасштабным техпроцессам. Во-первых, можно уменьшать высоту гребней (одновременно наращивая их количество — с тем, чтобы итоговая пропускная способность как минимум не сокращалась); во-вторых, наоборот, делать гребни повыше — и заодно сокращать их число, приходящееся на каждый транзистор (с той же самой оговоркой). Сегодня чаще применяют как раз второй способ, поскольку он напрямую ведёт к уменьшению занимаемой отдельными транзисторами площади, т. е. к росту плотности полупроводниковых элементов на квадратный дюйм. Да, при этом приходится решать ряд нетривиальных инженерных задач по обеспечению достаточной механической прочности высоких и узких плавников-«небоскрёбов», но оно того в итоге стоит.

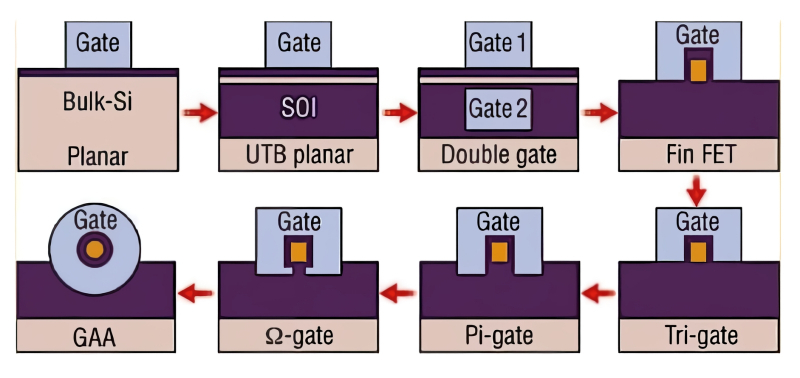

Взгляд на предполагавшуюся строго последовательной эволюцию полупроводниковых транзисторов из 2012 г. (Источник: EEPower) Точнее, стоило до самых недавних пор, — пока номинальные производственные нормы не подобрались к нижней границе единиц нанометров. Ещё в 2020 г. отдельные эксперты предсказывали, что на дистанциях около 5 нм подход FinFET потеряет актуальность — как раз по причине чрезмерного нарастания сложностей с изготовлением всё более высоких и узких транзисторных гребней. Предельные габариты мельчайшего из достижимых на нынешнем уровне развития технологий двухгребенчатого транзистора оцениваются как 5 нм для расстояния между плавниками и 15 нм — для длины проводящего канала. Предполагалось, что, пройдя через ряд эволюционных ступеней с поступательным сближением законцовок затвора — а именно pi-gate и omega-gate, — МОП-транзисторы достигнут стадии кольцевого, или замкнутого затвора, gate-all-around (GAA). На деле же, как уже упоминалось в самом начале, ведущие изготовители полупроводниковых устройств в мире — за исключением одной только Samsung Electronics (да и то в её случае речь идёт о ранней реализации техпроцесса, весьма скромно именуемой 3GAE, т. е. «3nm-class gate-all-around early») — по меньшей мере до 2024-го продолжат делать ставку именно на FinFET. Не прекращая, конечно же, тем временем доводить до ума свои собственные реализации GAAFET — RibbonFET, MBCFET (Multi-Bridge-Channel), Nanosheet transistor, Nanowire transistor и т. п. Связано это, как нетрудно догадаться, с экономическими соображениями: инвестиции, потребные для запуска серийного производства чипов на базе транзисторов с замкнутыми затворами, настолько велики, что пока ещё в целом разумнее оказывается вкладывать средства в дальнейшую модернизацию FinFET-технологий. По сути, GAAFET представляет собой предельный случай стратегии депопуляции гребенчатых транзисторов — сокращения числа гребней до одного без потери всех прочих полезных свойств этого полупроводникового «атома», а лучше даже с их ещё бóльшим усовершенствованием. Депопуляция выступает как альтернатива сокращению физических размеров транзисторных элементов (переходу на более миниатюрный техпроцесс), хотя нередко — пока позволяло доступное для сокращения среднее число плавников на транзистор — эти способы повысить плотность размещения транзисторов на квадратном дюйме микросхемы применялись совместно.

Две возможности повысить плотность транзисторов на единицу площади: уменьшить производственную норму (справа вверху) или, оставив техпроцесс прежним, снизить число гребней на один процессор (источник: Medium) Полупроводниковые структуры на подложке располагаются обычно прямоугольными блоками, напоминающими решётки: вытянутые ряды гребней перекрываются полосками затворов, и каждый транзистор представляет собой пересечение сплошного затвора со всеми гребнями, которые он накрывает (там есть тонкость, связанная с чередующимся размещением МОП-транзисторов p- и n-типа, но о ней чуть позже). При сокращении технологического процесса эти блоки-решётки пропорционально уменьшаются, так что один транзистор по-прежнему будет состоять из прежних, допустим, четырёх гребней на сплошной затвор, — только геометрические размеры этой конструкции станут меньше. А вот если грамотно организовать депопуляцию — добившись того, чтобы (в частности, за счёт увеличения высоты плавника) вместо четырёх каналов прежнюю суммарную пропускную способность обеспечивали два, — тогда получится удвоить число транзисторов на квадратный дюйм, не меняя производственной нормы. Физика! Вдобавок за десять с лишним лет активного развития FinFET-технологий инженеры предложили массу способов повышения пропускной способности многогребенчатых транзисторов и без депопуляции — помимо тривиального (и довольно сложно, кстати, реализуемого) вытягивания плавников по вертикали. В их числе — поиск новых материалов и/или присадок для затвора, источника/стока и изолирующего слоя в основании всей транзисторной конструкции, уменьшение толщины изолирующего материал гребней от затвора диэлектрика и т. п. Иными словами, физическая миниатюризация транзисторных элементов превратилась по сути в последнее средство, к которому прибегают лишь в самом крайнем случае: когда спасать закон (а на деле, напомним, самосбывающееся пророчество) Мура уже пора, а прорывов по другим направлениям изысканий совершить всё никак не удаётся. Однако как верёвочке ни виться, а концу быть: примерно к началу 2020-х стало ясно, что депопуляция как важнейший способ наращивания плотности транзисторов сходит со сцены — просто потому, что в подавляющем большинстве те и так уже оказались всего-навсего двухгребенчатыми. Остаётся пространство для единственного решительного шага — возврата к схеме «один плавник — один транзистор», которую часто используют для пояснения сути технологии FinFET, но которая изначально, пока делалась осознанная ставка на многогребенчатость, носила не прикладной, а чисто иллюстративный характер. Здесь-то и выходит на сцену GAAFET — кардинальное переосмысление морфологии единичного плавника, нацеленное на переход полупроводникового производства от формального выхода в третье измерение (когда канал, по которому перемещаются электрические заряды в транзисторе, всё равно остаётся плоским, — только вытягивается и изгибается) к предметному освоению пространства над плоскостью кремниевой заготовки, на которой фотолитографическим методом создаются полупроводниковые структуры. Суть технологии GAAFET в том, что теперь уже каждый плавник рассекается по горизонтали на этакие длинные бруски, проходящие сквозь толщу материала затвора один над другим. Отдельным элементом транзисторного канала становится таким образом замкнутая внутренняя граница между одним из фрагментов плавника (у которого по-прежнему на одной торцевой стороне располагается исток заряда, а на другой — сток) и пронзаемой им толщей затвора. Достаточно часто и плотно располагая брусья (ленты, прóволочки, листы — ribbons, wires, sheets — «фирменные» названия меняются в зависимости от фантазии конкретного разработчика), вполне можно добиться того, чтобы совокупная ширина нового канала превосходила таковую для одногребенчатой FinFET-структуры тех же геометрических размеров.

Поперечный срез инженерных прототипов транзисторов RibbonFET с четырьмя замкнутыми затворами на гребень — именно так они должны будут выглядеть после изготовления по не доведённому пока до серийной стадии техпроцессу «Intel 20A» (источник: Intel) Понятно, что чем больше число брусьев, на которые разрезается каждый плавник, и чем плотнее они укладываются один над другим, тем сложнее в производстве выйдет итоговая конструкция. Скачок уровня сложности чисто инженерных проблем здесь настолько внушительный, что предложенный едва ли не одновременно с FinFET подход GAAFET потребовал для перехода к первой серийной своей реализации (пока — только на мощностях компании Samsung Electronics, о чём шла речь в самом начале) примерно дюжину лет. Достаточно сказать, что там, где для формирования одного сплошного плавника требуется один цикл операций (нанесение фоторезиста на кремниевую подложку → экспонирование через фотоматрицу → смывка защитного слоя над предназначенными для удаления участками → протравливание → нанесение изолирующего слоя), GAAFET-структура нуждается в кратном увеличении числа шагов, поскольку после создания основы для будущей вертикальной стопки брусков придётся наносить «жертвенный» слой (sacrificial layer), устойчивый к процедурам засветки/травления, затем повторять эту процедуру после образования каждого очередного бруска, а в финале ещё и удалять «жертвенные» слои, после чего замещать их материалом затвора. ⇡#Важное дополнениеИнтуитивно ясно, что переход от двухгребенчатых FinFET к GAAFET с сохранением всех прочих параметров формирования полупроводниковых структур (и прежде всего — технологической нормы) позволит чипмейкерам «бесплатно» разом удвоить плотность транзисторов на квадратный дюйм. В кавычках — потому, что затраты на проведение всех необходимых дополнительных процедур бесспорно окажутся чрезвычайно велики, — надо полагать, именно по этой причине ни Intel, ни TSMC пока не спешат депопулировать свои транзисторы до единичных плавников. И всё-таки однажды — причём наверняка скорее раньше, чем позже, — наступит момент, когда и GAAFET-структуры придётся переводить на следующий уровень миниатюризации. Если учесть кратный рост числа необходимых производственных этапов, удовольствие это будет точно не из дешёвых, да и до бесконечности уходить в область единиц ангстрем точно не выйдет: длины транзисторных каналов начнут измеряться уже в считаных атомах, что больше не позволит игнорировать крайне неприятные для фоннеймановских вычислительных систем квантовые эффекты на уровне отдельных транзисторов. И что тогда? Конец прогрессу?

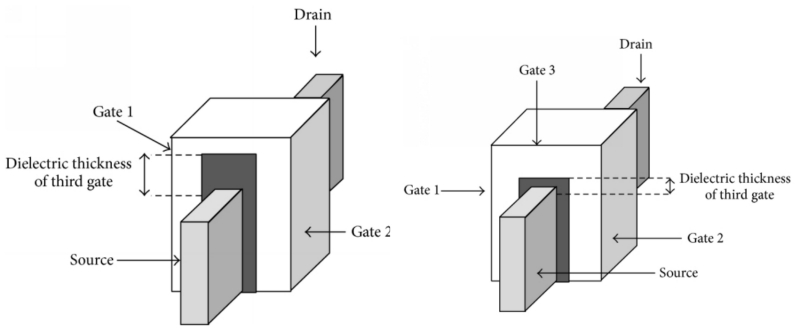

Наглядное пояснение, по какой именно причине Samsung Electronics так спешит с внедрением GAAFET: за счёт новой технологии плотность размещения транзисторов за год-два обещает практически удвоиться относительно достигнутого в конце 2022-го на технологии FinFET предела (источник: WikiChip) Ни в коем разе: как на излёте XX века разработчики уже обдумывали прототипы грядущих FinFET, так и сегодня полным ходом идёт работа над следующей после GAAFET (и потому пока весьма отдалённой в плане практической реализации) технологией организации транзисторов — complementary FET (CFET). «Дополнительными» эти структуры называют потому, что здесь уже не на один МОП-транзистор будет приходиться один плавник, а внутри одного плавника (точнее, сохранившей его общие очертания вертикальной структуры) расположатся сразу несколько отдельных транзисторов, причём не просто МОП, а КМОП — что представляют собой, как мы уже ранее упоминали, комплементарные (взаимодополняющие) связки транзисторов, построенных на каналах с электронной и с дырочной проводимостью: n-МОП и p-МОП. Транзисторы n-МОП, напомним, называют прямыми (они открываются при подаче напряжения на затвор), а p-МОП — инверсными (наоборот, открываются при снятии напряжения с затвора). Комплементарность — взаимодополняемость — их проявляется в том, что инверсный МОП-транзистор устроен обратным по отношению к прямому образом: основу p-МОП образует полупроводник n-типа, исток и сток формируют инклюзии p-типа, а вместо электронной проводимости в открытом канале образуется дырочная, тогда как у n-МОП всё наоборот. Подход FinFET, в частности, подразумевает, что чередующиеся гребни p- и n-типа (точнее, комплекты плавников — речь всё-таки не об одногребенных GAAFET) перекрываются одним и тем же затвором, что позволяет двум соседним транзисторам с комплементарным устройством образовывать эффективно работающую пару. Друг другу они при этом не мешают, поскольку одновременно действовать в принципе не могут, — если на затвор подано рабочее напряжение, то транзистор n-МОП открыт, а p-МОП закрыт, и наоборот. Так вот, ключевой принцип CFET заключается в том, что по высоте над основанием будущей микросхемы один над другим располагаются комплементарные пары транзисторов n-МОП/p-МОП с замкнутыми затворами, — привет, GAAFET! Звучит опять же совершенно логично, и на поясняющих схемах смотрится доходчиво, — отличия от предыдущей ступени транзисторной эволюции минимальны: всё те же бруски, проходящие сквозь толщу вытянутого по вертикали затвора, только других расцветок. Однако если уже технология GAAFET с инженерной точки зрения чрезвычайно непроста в реализации, то CFET в этом плане поднимает ставки ещё на порядок: располагать комплементарные транзисторные пары одну над другой неимоверно сложнее, чем на одной плоскости. Между транзисторами n-МОП и p-МОП — огромная прикладная разница в смысле инженерной реализации: для них необходимы разные металлы, различные присадки в полупроводниковые участки, и даже контакты для подключения их к логическим цепям должны быть размещены по-своему. Да и сама технология потокового производства CFET-транзисторов нуждается в разработке едва ли не с нуля. Дело в том, что все предшествующие усилия исследователей на данном направлении, не исключая и методику получения GAAFET-структур, концентрировались на избирательной формовке отдельных вертикальных конструкций с однотипным содержимым, будь то сплошной гребень FinFET или выстроенные лесенкой GAA-бруски. В случае же CFET необходимо выборочно формировать разнородные структуры — те же самые бруски, но с n- или с p-проводимостью — в пределах одной и той же вертикали.

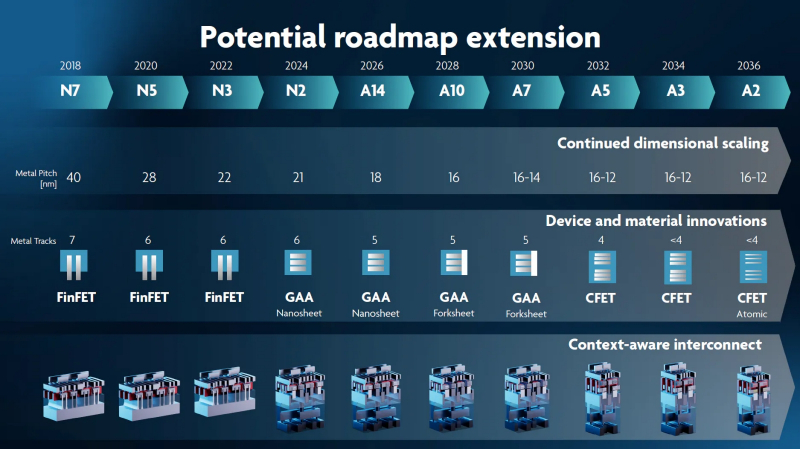

Хотя расстояние между металлическими контактами (metal pitch) после перехода на CFET будет меняться мало, толщина затворов внутри вертикально упакованных КМОП-транзисторов к 2036 г. выйдет, как предполагается, на атомарный уровень (источник: IMEC) До самого последнего времени полупроводниковая фотолитография развивалась, по сути, в пределах одной плоскости с «вытягиванием» из неё отдельных структур по вертикали, — и здесь инженеры достигли невероятных (для времён первого теоретического упоминания о FinFET) высот. Подлинно же трёхмерная фотолитография, нацеленная на создание разнородных сверхминиатюрных полупроводниковых конструкций в объёме, только зарождается, — так что путь к освоению серийного выпуска микросхем с транзисторами CFET навряд ли займёт меньше десятилетия. По крайней мере, осторожные оценки аналитиков IMEC указывают на 2032 год, не ранее. Вполне возможно, что промежуточным звеном между GAAFET и CFET станет предложенная Intel в качестве концепта ещё в 2019 г. технология Forksheet FET, предусматривающая укладку высоких штабелей из изолированных брусков с n- и p-проводимостью по соседству, но с вертикальной разделительной стенкой из диэлектрика между ними — и так, чтобы их охватывал единый затвор. Принципиальной разницы с GAA-подходом здесь нет, однако более плотная компоновка составляющих транзисторы комплементарных элементов позволит, как надеются инженеры, лучше отработать необходимые для налаживания потокового CFET-производства технологии. Самое же занимательное в том, что пока эксперты в области полупроводниковых технологий не могут сколько-нибудь определённо сказать, что же будет после CFET — за пределами производственных норм в условный 1 ангстрем. Старый добрый кремний со всевозможными присадками заменят углеродные нанотрубки? Быть может, произойдёт фундаментальный прорыв в области фотоники, и полупроводники в принципе сойдут со сцены? Поразительно, но в конце 1980-х вполне реально было заглянуть в передовые технологии 2020-х, — а сегодня сделать обоснованный прогноз «всего лишь» на десятилетие представляется чрезвычайно сложной задачей. Таковы уж современные темпы технического прогресса — слишком велика оказывается неопределённость в интервале уже единиц лет. Тем интереснее будет, когда появится хоть какая-то определённость. Скучать инженерам-микроэлектронщикам в обозримом будущем уж точно не придётся!

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|