|

Опрос

|

реклама

Быстрый переход

Intel показала образец огромного ИИ-чипа с четырьмя логическими блоками и 12 стеками HBM4

01.02.2026 [15:59],

Николай Хижняк

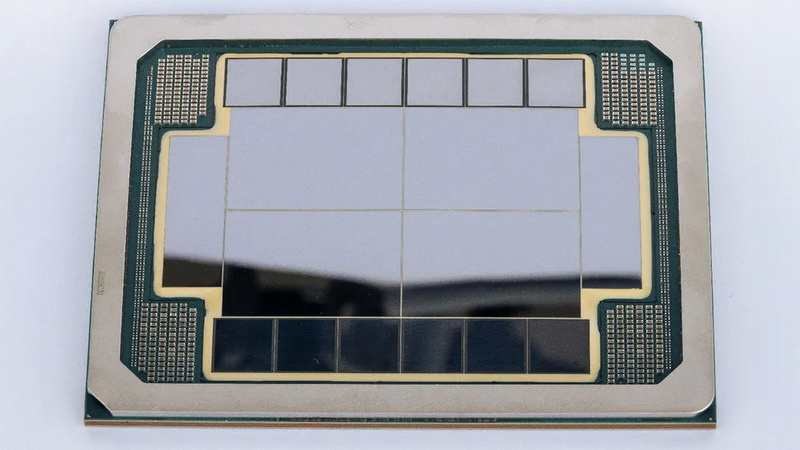

Intel Foundry выпустила рекламный документ, подробно описывающий передовые решения компании в области разработки и реализации аппаратных средств для приложений искусственного интеллекта и высокопроизводительных вычислений. Intel также продемонстрировала «тестовый образец чипа для ИИ», показывающий текущие возможности компании в области корпусирования.

Источник изображений: Intel Intel показала систему в корпусе (SiP) размером в восемь фотошаблонов стандартных микросхем, включающую четыре логических блока, 12 стеков HBM4-класса и два блока ввода-вывода. В отличие от масштабной концепции с 16 логическими блоками и 24 стеками HBM5, представленной компанией в прошлом месяце, эта система действительно пригодна для производства уже сегодня. Важно отметить, что Intel Foundry показала не работающий ускоритель ИИ, а «тестовый образец чипа для ИИ», демонстрирующий, как можно физически создавать (или, скорее, собирать) будущие процессоры для ИИ и высокопроизводительных вычислений. Intel показывает весь метод конструирования, который объединяет большие вычислительные блоки, стеки высокоскоростной памяти, сверхбыстрые межчиповые соединения и новые технологии питания в одном технологичном корпусе. Этот корпус значительно отличается от того, что предлагает сегодня такие компании, как TSMC. Intel хочет показать, что процессоры следующих поколений для высокопроизводительного ИИ могут иметь многочиплетную конструкцию, и Intel Foundry уже способна их производить. В основе продемонстрированной платформы лежат четыре больших логических блока, предположительно построенных на технологическом процессе Intel 18A (следовательно, с транзисторами RibbonFET с круговым затвором и системой питания PowerVia с обратной стороны), которые окружены стеками памяти класса HBM4 и блоками ввода-вывода. Все ключевые элементы, предположительно, соединены мостами EMIB-T 2.5D, встроенными непосредственно в подложку корпуса. Intel использует технологию межчиплетного интерфейса EMIB-T, который добавляет сквозные кремниевые переходные отверстия внутри мостов, чтобы питание и сигналы могли проходить как вертикально, так и горизонтально, для максимизации плотности межсоединений и подачи питания. Платформа разработана для межкристальных интерфейсов UCIe, работающих на скорости 32 ГТ/с и выше, которые, по-видимому, также используются для подключения стеков C-HBM4E. Тестовый образец чипа также демонстрирует переход Intel к вертикальной сборке. Дорожная карта техпроцессов компании включает технологию Intel 18A-PT, разработанную специально для чиплетов, которые подразумевают размещение других логических кристаллов или памяти сверху. Следовательно, чиплеты должны иметь подачу питания с обратной стороны, а также использовать сквозные и гибридные межсоединения. В случае «тестового образца ИИ-процессора» базовые кристаллы 18A-PT располагаются под вычислительными кристаллами 18A/18A-P и либо действуют как большие чипы кеш-памяти, либо выполняют иную вспомогательную функцию. Для вертикального соединения чиплетов Intel использует семейство технологий упаковки Foveros — Foveros 2.5D, Foveros-R и Foveros Direct 3D. Они позволяют реализовать тонкошаговое медное соединение между активными кристаллами для обеспечения максимальной пропускной способности и энергоэффективности верхних кристаллов. Вместе с мостами EMIB эти методы позволяют Intel создавать гибридную латерально-вертикальную сборку, которую компания позиционирует как альтернативу большим кремниевым интерпозерам с более высоким коэффициентом использования пластины и выходом годных изделий. Для многочиплетных ускорителей ИИ и высокопроизводительных вычислений основным конструктивным ограничением является питание. С этой целью платформа Intel должна объединить все последние инновации Intel в области энергосбережения, включая PowerVia, встроенные конденсаторы Omni MIM, развязку на уровне моста в EMIB-T, конденсаторы eDTC и eMIM-T на базовом кристалле, а также встроенные индукторы CoaxMIL для поддержки полуинтегрированных регуляторов напряжения (IVR), расположенных под каждым стеком и под самим корпусом (в отличие от IVR в случае CoWoS-L от TSMC, которые являются частью интерпозера). Эта многоуровневая сеть предназначена для поддержки стабильного тока в рабочих нагрузках генеративного ИИ без снижения уровня напряжения. Своей демонстрацией Intel, очевидно, пытается привлечь клиентов. На данный момент неизвестно, будет ли ИИ-ускоритель нового поколения под кодовым Jaguar Shores, запуск которого запланирован на 2027 год, использовать архитектуру, которую Intel демонстрирует сегодня. Intel собрала гигантский ИИ-чип из 16 вычислительных кристаллов и 24 стеков HBM5

26.12.2025 [23:05],

Николай Хижняк

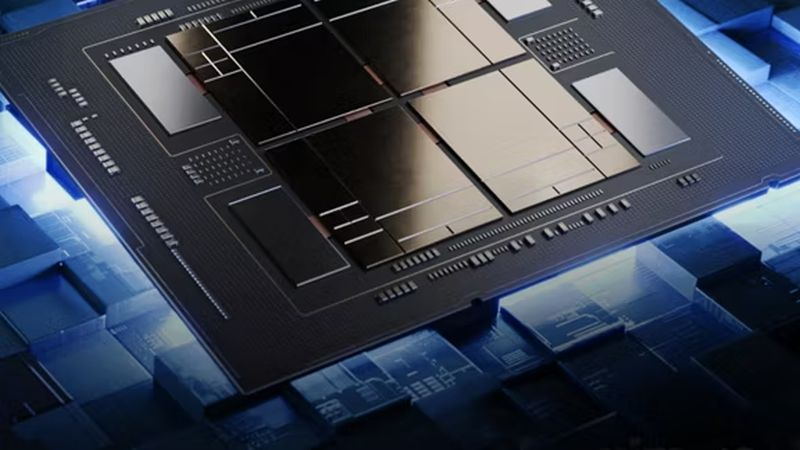

Intel первой разработала явно дезагрегированную чиплетную архитектуру — серверные GPU Ponte Vecchio для приложений ИИ и высокопроизводительных вычислений состояли из 47 чиплетов. Этот продукт до сих пор удерживает рекорд по количеству элементов в многослойной архитектуре, но Intel Foundry планирует нечто гораздо более экстремальное: многочиплетный корпус, объединяющий не менее 16 вычислительных элементов на восьми базовых кристаллах и 24 стека памяти HBM5.

Источник изображений: Intel Предполагается, что такая конструкция будет иметь возможность 12-кратного масштабирования до самых больших чипов для ИИ на рынке (12-кратный размер фотошаблона, превосходящий 9,5-кратный размер фотошаблона TSMC). Концептуальный многочиплетный корпус Intel 2.5D/3D демонстрирует 16 больших вычислительных элементов (движков искусственного интеллекта или процессоров), изготовленных по технологическому процессу Intel 14A или даже более сложному 14A-E (1,4 нм, расширенные возможности, транзисторы RibbonFET 2 второго поколения с круговым затвором, улучшенная система питания PowerVia Direct с обратной стороны). Вычислительные элементы расположены поверх восьми (предположительно, размером с фотошаблон) базовых вычислительных кристаллов, изготовленных по техпроцессу 18A-PT (1,8 нм, повышенная производительность за счёт сквозных кремниевых соединений TSV и системы питания с обратной стороны), которые могут либо выполнять дополнительную вычислительную работу, либо содержать большой объём кэш-памяти SRAM для «основных» вычислительных кристаллов, как показано в примере Intel. Базовые кристаллы в такой конструкции соединены с вычислительными блоками с помощью передовой технологии упаковки Foveros Direct 3D, использующей сверхплотное гибридное соединение медных контактов толщиной менее 10 мкм для обеспечения максимальной пропускной способности и энергоэффективности верхних кристаллов. Базовые кристаллы используют EMIB-T (улучшенная версия Embedded Multi-Die Interconnect Bridge с TSV), а сверху — UCIe-A для боковых (2.5D) межсоединений между собой и с кристаллами ввода-вывода, изготовленными по технологии 18A-P (1,8 нм, с улучшенной производительностью), а также с изготовленными по заказу того или иного клиента базовыми кристаллами, что позволяет разместить до 24 стеков памяти HBM5. Примечательно, что Intel предлагает использовать EMIB-T с интерфейсом UCIe-A для подключения специализированных модулей HBM5, а не стеки HBM5 стандарта JEDEC с традиционным отраслевым интерфейсом, что, возможно, призвано повысить производительность и ёмкость. Учитывая концептуальный характер разработки, использование специализированных стеков HBM5 не является обязательным требованием проектирования. Это лишь способ показать, что Intel также может интегрировать такие чипы. Весь пакет также может поддерживать PCIe 7.0, интерфейс 224G SerDes, некогерентные коммутационные сети, содержать оптические модули и собственные ускорители для таких задач, как безопасность, а также память LPDDR5X для увеличения ёмкости DRAM. Intel Foundry продемонстрировала два концепта: «среднего масштаба» с четырьмя вычислительными блоками и 12 модулями HBM и «экстремальный» — с 16 блоками и 24 стеками HBM5, о котором говорится в данной заметке. Даже конструкция среднего масштаба достаточно продвинута по сегодняшним стандартам, и Intel может производить её уже сегодня. Что касается экстремального варианта, он может появиться к концу десятилетия, когда Intel усовершенствует не только технологию 3D-упаковки Foveros Direct, но и свои производственные узлы 18A и 14A. Возможность производить такие корпуса чипов экстремального размера к концу десятилетия поставит Intel на один уровень с TSMC, которая планирует нечто подобное и даже ожидает, что по крайней мере некоторые клиенты будут использовать её решения для интеграции компонентов размером с целую кремниевую пластину примерно в 2027–2028 годах. Технически Intel готова упаковывать чипы для клиентов TSMC

31.03.2025 [04:59],

Алексей Разин

Спрос на ускорители вычислений Nvidia растёт опережающими темпами, и одной из причин непропорционального увеличения предложения являются проблемы с упаковкой чипов на мощностях TSMC. Представители Intel утверждают, что решения клиентов TSMC с упаковкой типа CoWoS можно без проблем перенести на фирменную технологию Foveros.

Источник изображения: Intel Об этом в переписке с группой репортёров, как сообщает EE Times, заявил недавно Марк Гарднер (Mark Gardner), вице-президент Intel Foundry по упаковке и тестированию: «Что касается Foveros, то она способна обеспечить бесшовный переход. Мы взяли продукты, которые используют технологию CoWoS, и прямым образом портировали их без каких-либо изменений в дизайне на технологию Foveros». Если учесть, что чипы для ускорителей вычислений Nvidia используют технологию упаковки CoWoS, есть вероятность их успешного переноса на конвейер Intel Foundry — хотя бы на стадии упаковки и тестирования. Важно, что тем самым Nvidia быстрее исключит транспортировку кремниевых пластин на Тайвань при условии их предварительной обработки в США на предприятии TSMC в Аризоне. То есть, политические факторы могут сыграть Intel на руку сильнее, чем технологические или экономические. По словам представителя Intel, компания с прошлого года выпускает решения, которые изначально разрабатывались под CoWoS, но позже были приспособлены под фирменные технологии EMIB или Foveros. Для потенциальных клиентов это важно, как добавил Гарднер, поскольку это не вынуждает их долго ждать адаптации дизайна своих компонентов под возможности нового подрядчика. Внутри Intel есть команда специалистов, которые взаимодействуют с TSMC, Samsung, SK hynix и Micron в вопросах унификации правил дизайна, позволяющих использовать интерфейсы в сложной пространственной компоновке чипов с минимальными изменениями при переносе с одного конвейера на другой. Как признался Гарднер, компания Intel разработала технологию упаковки EMIB-T с использованием межслойных соединений, которая позволяет создавать чипы с трёхмерной компоновкой и высокой пропускной способностью интерфейсов без высокого энергопотребления. Клиенты Intel уже готовы использовать эту технологию в последующие год или два. Впрочем, имена своих клиентов контрактное подразделение Intel до сих пор раскрывает неохотно, и в конкретной беседе с представителями EE Times упоминались только Mediatek и AWS (Amazon). Эксперты TechInsights утверждают, что Intel не особо продвигает свои возможности по контрактной упаковке чипов, тогда как компания располагает не только передовыми технологиями в этой сфере, но и свободными производственными мощностями. Траектория развития полупроводниковой отрасли такова, что на нынешнем этапе упаковке важно уделять внимание, поскольку она позволяет эффективно повышать производительность компонентов без видимого прогресса в литографии. Intel открыла в Нью-Мексико завод Fab 9, который будет массово выпускать чипы с передовой 3D-упаковкой

25.01.2024 [10:27],

Павел Котов

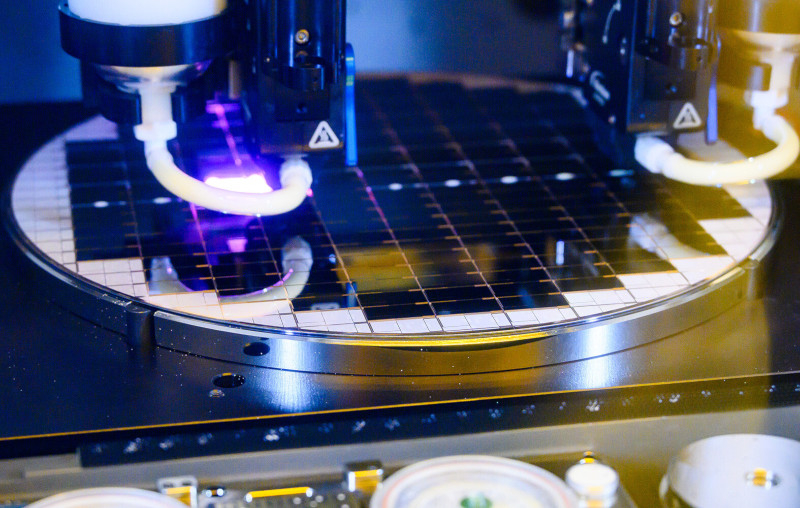

Intel торжественно открыла в городе Рио-Ранчо (шт. Нью-Мексико, США) завод Fab 9 — предприятие запущено в рамках инвестиционной программы с бюджетом $3,5 млрд, направленной на организацию производства с использованием передовых решений в области упаковки чипов, в том числе технологии 3D-упаковки Intel Foveros, предлагающей гибкие возможности компоновки чиплетов с оптимизацией по мощности, производительности и стоимости.

Источник изображений: intc.com Расположенные в Рио-Ранчо заводы Fab 9 и Fab 11x составляют первую действующую площадку для массового производства чипов с передовой 3D-упаковкой Intel, образуя сквозной производственный процесс, направленный на формирование эффективной цепочки поставок. Полупроводниковая промышленность вступает в эпоху гетерогенных решений, предусматривающей сочетание нескольких чиплетов в одном корпусе с передовыми технологиями, такими как Foveros и EMIB (Embedded Multi-die Interconnect Bridge) — они представляют эффективный способ достичь 1 трлн транзисторов на чипе, продлевая действие закона Мура в следующее десятилетие.  Технология 3D-упаковки Intel Foveros — первое в своём роде решение, позволяющее создавать процессоры, тайлы в которых располагаются не рядом, а вертикально. Это поможет Intel и её заказчикам комбинировать вычислительные модули для оптимизации затрат и энергоэффективности. Инвестиционная программа Intel в Рио-Ранчо с бюджетом $3,5 млрд позволила создать 3000 рабочих мест на строительстве и ещё 3500 — по всему штату. |