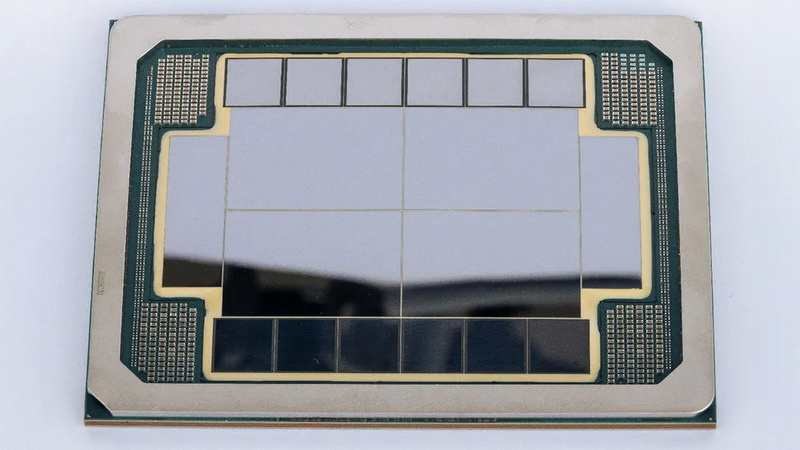

Intel Foundry выпустила рекламный документ, подробно описывающий передовые решения компании в области разработки и реализации аппаратных средств для приложений искусственного интеллекта и высокопроизводительных вычислений. Intel также продемонстрировала «тестовый образец чипа для ИИ», показывающий текущие возможности компании в области корпусирования.

Источник изображений: Intel

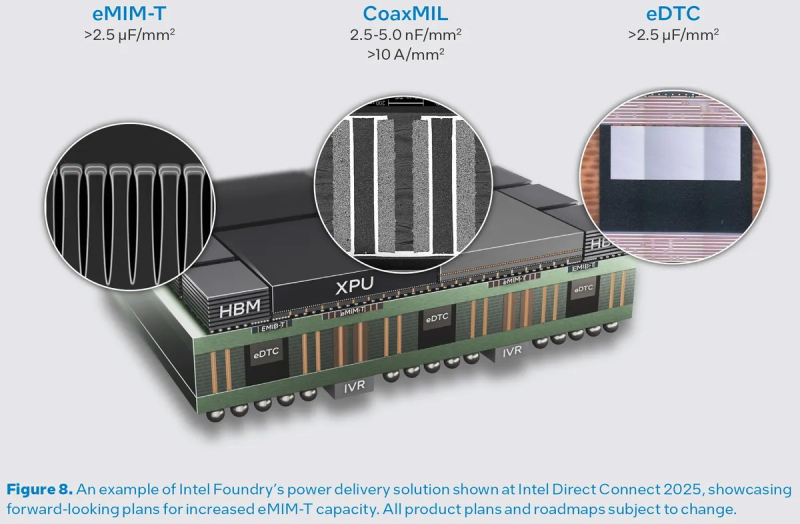

Intel показала систему в корпусе (SiP) размером в восемь фотошаблонов стандартных микросхем, включающую четыре логических блока, 12 стеков HBM4-класса и два блока ввода-вывода. В отличие от масштабной концепции с 16 логическими блоками и 24 стеками HBM5, представленной компанией в прошлом месяце, эта система действительно пригодна для производства уже сегодня.

Важно отметить, что Intel Foundry показала не работающий ускоритель ИИ, а «тестовый образец чипа для ИИ», демонстрирующий, как можно физически создавать (или, скорее, собирать) будущие процессоры для ИИ и высокопроизводительных вычислений. Intel показывает весь метод конструирования, который объединяет большие вычислительные блоки, стеки высокоскоростной памяти, сверхбыстрые межчиповые соединения и новые технологии питания в одном технологичном корпусе. Этот корпус значительно отличается от того, что предлагает сегодня такие компании, как TSMC. Intel хочет показать, что процессоры следующих поколений для высокопроизводительного ИИ могут иметь многочиплетную конструкцию, и Intel Foundry уже способна их производить.

В основе продемонстрированной платформы лежат четыре больших логических блока, предположительно построенных на технологическом процессе Intel 18A (следовательно, с транзисторами RibbonFET с круговым затвором и системой питания PowerVia с обратной стороны), которые окружены стеками памяти класса HBM4 и блоками ввода-вывода. Все ключевые элементы, предположительно, соединены мостами EMIB-T 2.5D, встроенными непосредственно в подложку корпуса. Intel использует технологию межчиплетного интерфейса EMIB-T, который добавляет сквозные кремниевые переходные отверстия внутри мостов, чтобы питание и сигналы могли проходить как вертикально, так и горизонтально, для максимизации плотности межсоединений и подачи питания. Платформа разработана для межкристальных интерфейсов UCIe, работающих на скорости 32 ГТ/с и выше, которые, по-видимому, также используются для подключения стеков C-HBM4E.

Тестовый образец чипа также демонстрирует переход Intel к вертикальной сборке. Дорожная карта техпроцессов компании включает технологию Intel 18A-PT, разработанную специально для чиплетов, которые подразумевают размещение других логических кристаллов или памяти сверху. Следовательно, чиплеты должны иметь подачу питания с обратной стороны, а также использовать сквозные и гибридные межсоединения. В случае «тестового образца ИИ-процессора» базовые кристаллы 18A-PT располагаются под вычислительными кристаллами 18A/18A-P и либо действуют как большие чипы кеш-памяти, либо выполняют иную вспомогательную функцию. Для вертикального соединения чиплетов Intel использует семейство технологий упаковки Foveros — Foveros 2.5D, Foveros-R и Foveros Direct 3D. Они позволяют реализовать тонкошаговое медное соединение между активными кристаллами для обеспечения максимальной пропускной способности и энергоэффективности верхних кристаллов. Вместе с мостами EMIB эти методы позволяют Intel создавать гибридную латерально-вертикальную сборку, которую компания позиционирует как альтернативу большим кремниевым интерпозерам с более высоким коэффициентом использования пластины и выходом годных изделий.

Для многочиплетных ускорителей ИИ и высокопроизводительных вычислений основным конструктивным ограничением является питание. С этой целью платформа Intel должна объединить все последние инновации Intel в области энергосбережения, включая PowerVia, встроенные конденсаторы Omni MIM, развязку на уровне моста в EMIB-T, конденсаторы eDTC и eMIM-T на базовом кристалле, а также встроенные индукторы CoaxMIL для поддержки полуинтегрированных регуляторов напряжения (IVR), расположенных под каждым стеком и под самим корпусом (в отличие от IVR в случае CoWoS-L от TSMC, которые являются частью интерпозера). Эта многоуровневая сеть предназначена для поддержки стабильного тока в рабочих нагрузках генеративного ИИ без снижения уровня напряжения.

Своей демонстрацией Intel, очевидно, пытается привлечь клиентов. На данный момент неизвестно, будет ли ИИ-ускоритель нового поколения под кодовым Jaguar Shores, запуск которого запланирован на 2027 год, использовать архитектуру, которую Intel демонстрирует сегодня.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018