⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Тут надо технически, или Каким образом DUV-технологии всё же добрались до единиц нанометров

⇡#Пропустить нельзя заблокироватьЕсли свободных электронов в образце много, время от времени неизбежна рекомбинация заряда: очередной электрон «взаимоуничтожится» с дыркой, сев на внешнюю оболочку к атому, у которого как раз одного электрона в данный момент недостаёт. Логично поэтому легировать полупроводниковый материал — добавлять к нему в небольших количествах примеси, которые будут обеспечивать избыток дополнительных зарядов в образце. «Небольшие» — это примерно один-два атома примеси на десять миллионов атомов кремния, иначе свободных зарядов окажется слишком много, и образец начнёт вести себя не как полупроводник, а как сильно загрязнённый шлаками металл. Важно, что легирование возможно как электронами, так и дырками. Если у атома, физико-химические свойства которого позволят ему без труда встроиться в кремниевую кристаллическую решётку, больше электронов на внешней оболочке, чем у Si (т. е. больше 4 — например, 5, как у фосфора, P), то это будет примесь так называемого n-типа, negative: она сразу же обеспечивает присутствие в образце дополнительных свободных — точнее, не обременённых ковалентными связями — электронов. А если число электронов на внешней оболочке меньше 4 (как у бора, B, у которого их 3), получается легирующая примесь p-типа, positive, автоматически порождающая в образце дополнительные дырки. Теперь, хочется верить, значительно более ясной становится схема работы МОП-транзистора, наверняка уже неоднократно встречавшаяся пытливому читателю. В данном случае на схеме изображён транзистор типа n-МОП (NMOS), с каналом на электронной (а не дырочной) проводимости: На подложке с проводимостью p-типа (дырочной, т. е. с усиленной легированием нехваткой свободных электронов) создают — опять-таки за счёт локального точечного легирования другого типа — две зоны с n-проводимостью, разнесённые на небольшое расстояние (длину канала L): исток и сток будущего транзистора. Далее на поверхность полупроводника наносят изолирующий слой, через который к истоку и стоку подводят металлические контакты, а над зоной канала размещают затвор. Если включить такой транзистор в схему с источником питания, ток через неё не потечёт, поскольку сток изолирован от истока областью p-проводимости, — электроны там перемещаться не могут (точнее, могут, но сразу же будут рекомбинировать с имеющимися в избытке дырками). При подаче положительного управляющего напряжения на затвор тот формирует положительный заряд, который выталкивает избыточные дырки из области канала в сторону подложки (базы), а в зону непосредственно под затвором стекаются доступные в толще полупроводника свободные электроны. Даже невзирая на оставшиеся в толще p-легированного образца дырки, свободные электроны неизбежно будут возникать под затвором вследствие теплового разрыва ковалентных связей, и для временного формирования канала их вполне хватит. В какой-то момент концентрация электронов в области непосредственно под затвором станет достаточной, чтобы канал, на время приобретя проводящие свойства, открылся. Именно тогда по нему и пойдёт перенос заряда. Чем выше уровень напряжения на затворе, тем шире получающийся под ним канал — и тем выше сила тока через транзистор. ⇡#Это логично!Одиночный МОП-транзистор — по сути, простейший переключатель: в зависимости от внешней команды (открыть/закрыть затвор) он пропускает либо не пропускает ток. В принципе, можно было бы всю микроэлектронику выстраивать на n-МОП-транзисторах, однако выяснилось, что с точки зрения и логики, и инженерии лучше использовать комплементарные (взаимодополняющие) связки n-МОП и p-МОП, получая тем самым структуры КМОП (CMOS в англоязычном обозначении).

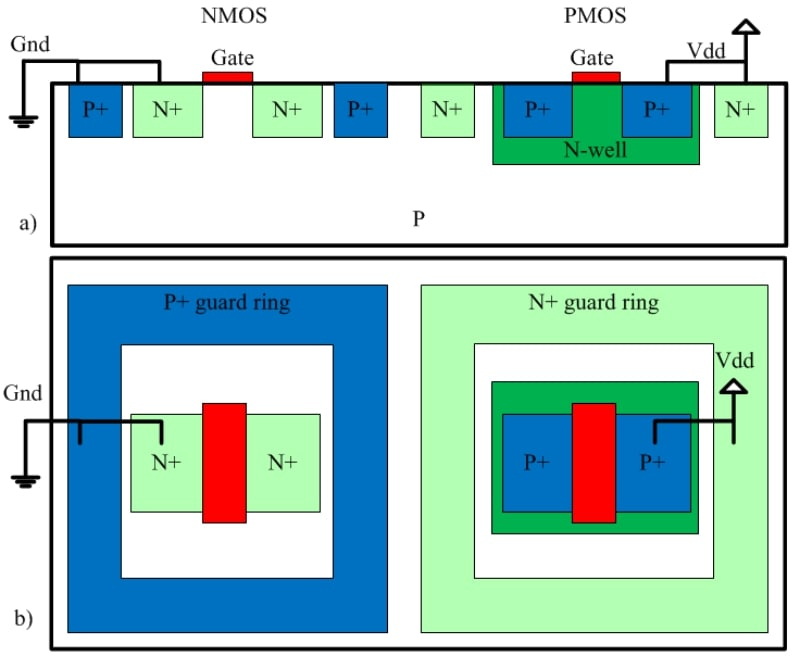

Комплементарная структура из NMOS- и PMOS-транзисторов (виды в разрезе и сверху): на единой подложке с p-проводимостью создан обширный участок с n-легированием (n-well), а уже внутри него сформирован PMOS-транзистор, причём транзисторы обоих типов отграничены от соседних структур защитными кольцами, препятствующими бесконтрольному перетоку зарядов (источник: German Aerospace Center) Транзисторы n-МОП называют прямыми (они открываются при подаче на затвор напряжения), а p-МОП — инверсными (наоборот, открываются при снятии напряжения с затвора). Комплементарность их проявляется в том, что инверсный МОП-транзистор устроен обратным по отношению к прямому образом: основу p-МОП образует полупроводник n-типа, исток и сток формируют инклюзии p-типа, а вместо электронной проводимости в открытом канале образуется дырочная. Работа компьютеров архитектуры фон Неймана основана на операциях бинарной (двоичной) логики, воплощать которые при помощи КМОП-транзисторов оказывается легко и просто. Ну как — просто…

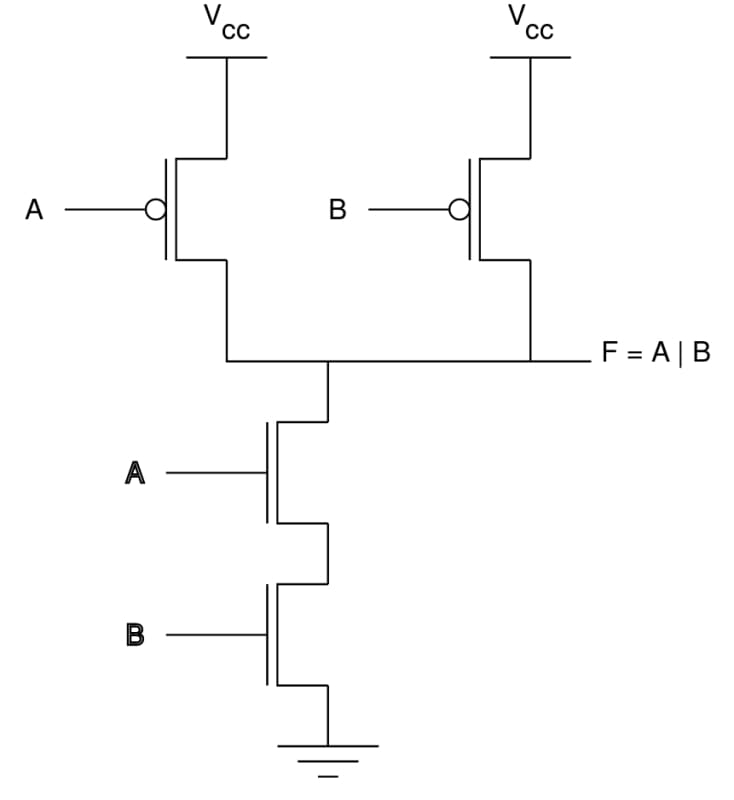

Штрих Шеффера на КМОП-транзисторах: Vcc обозначает «Voltage Collector Collector», напряжение источника питания на общей шине (источник: Wikimedia Commons) Здесь приведена схема реализации на четырёх МОП-транзисторах так называемого штриха Шеффера — бинарной логической операции И-НЕ (в англоязычном варианте — NAND; одно из принятых для него обозначений в формулах бинарной логики— собственно вертикальный штрих, «|»), «отрицания конъюнкции» для двух аргументов. Смысл штриха Шеффера в том, что если оба аргумента, A и B, истинны одновременно, то результат применения штриха Шеффера к ним — F = A | B — получается ложным. Во всех же остальных случаях, т. е. когда хотя бы один из аргументов ложен, штрих Шеффера даёт значение «истина». В плане удобства вычислений вручную эта операция может показаться чрезмерно громоздкой: логическое И, логическое ИЛИ, логическое НЕ значительно проще для бытового восприятия. Однако с точки зрения прикладной микроэлектроники он ценен тем, что все базовые операции бинарной логики могут быть представлены через один только штрих Шеффера: ⇡#(A | A) | (B | B) = A || B (логическое ИЛИ), ⇡#(A | B) | (A| B) = A & B (логическое И) и т. д. В результате — если сразу подходить к проблеме построения сложных логических схем с учётом перспективы их реализации на некой элементной базе — выходит, что заполненная штрихами Шеффера (точнее, реализующими эту элементарную операцию блоками транзисторов) микросхема может стать основой для создания вычислительных систем любой сложности. «Любой» лишь в пределах архитектуры фон Неймана, само собой, — но для машин такого рода задач имеется предостаточно, а для более сложных уже ведётся разработка квантовых компьютеров. С точки же зрения полупроводникового производства чем выше степень однотипности миниатюрных элементов разрабатываемой микросхемы, тем проще её проектировать и легче изготавливать.

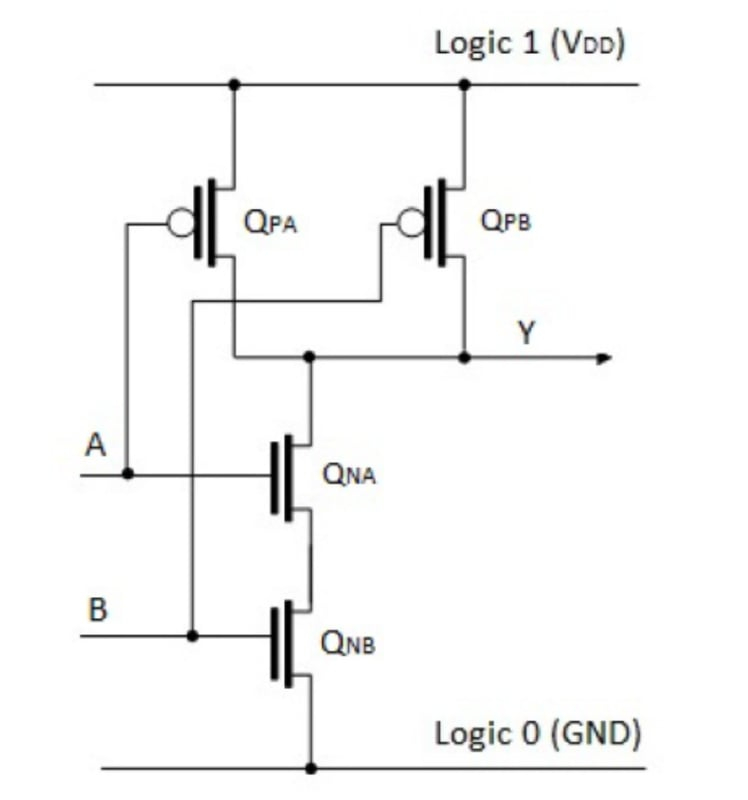

Ещё одна схема штриха Шеффера на КМОП-транзисторах: здесь Vdd, «Voltage Drain Drain», обозначает напряжение на стоке транзистора, подключённом к общей шине, и по смыслу эквивалентно Vcc с предыдущего рисунка (источник: Wikimedia Commons) Читать схему реализации штриха Шеффера (n-МОП- и p-МОП-транзисторы на ней несложно различить по отсутствию либо, соответственно, наличию кружка на условном обозначении затвора) особенно просто, если представить, что по шине Vcc /Vdd на подключённые к ней элементы СБИС «подаётся» логическая единица, а шина заземления «генерирует» логический ноль. Штрих Шеффера же выступает при этом допущении в роли сложного вентиля, что под воздействием управляющих сигналов по определённым правилам коммутирует на выход либо логический ноль снизу, либо логическую единицу сверху. Тогда если оба (подаваемых, напомним, на затворы каждой комплементарной пары n-МОП- и p-МОП-транзисторов) управляющих сигнала A и B одновременно принимают значение «истина», то два прямых МОП-транзистора (внизу, соединены последовательно) будут открыты, а инверсные (вверху, соединены параллельно) — оба закрыты. Значит, на выход такой схемы свободно «пройдёт» логический ноль от шины заземления снизу, а логическая единица от шины питания будет «блокирована» разомкнутыми инверсными транзисторами. Теперь пусть хотя бы один из управляющих сигналов A и B равен логическому нулю. В этом случае окажется разомкнута нижняя часть схемы (через включённые последовательно прямые транзисторы, хотя бы один из которых непременно окажется разомкнут, «не пройдёт» логический ноль), а сверху хотя бы один из параллельных инверсных транзисторов свободно «пропустит» логическую единицу. Таким образом, для построения единичного штриха Шеффера по приведённой ранее схеме достаточно будет расположить поблизости два ряда чередующихся полупроводниковых элементов n- и p-типов с соответствующими инклюзиями для истоков и стоков, перпендикулярно разместить управляющие затворы — и всё это соединить металлическими шинами. Получается примерно вот что — это вид сверху на плоскость, на которой размещены в три слоя элементы, формирующие транзисторы и соединения между ними: Чёрные квадраты обозначают металлические контакты, соединяющие слои насквозь, по вертикали. Для того чтобы строить более сложные логические схемы, необходимо объединять особым образом штрихи Шеффера — именно для этого служат дополнительные металлические слои (не показанные здесь) поверх изображённого голубым цветом. В последнее время идут работы по созданию транзисторов с вертикально, а не на одном уровне расположенными транзисторами n-МОП и p-МОП — это позволит без каких бы то ни было дополнительных ухищрений в очередной раз выполнить «закон Мура», удвоив плотность транзисторов на квадратный дюйм на уже имеющемся оборудовании. Но пока вертикальное размещение комплементарных транзисторов (реализуемое, кстати, при помощи технологии, родственной SAMP, о которой речь пойдёт чуть ниже) остаётся перспективной разработкой, не вышедшей на уровень серийного производства.

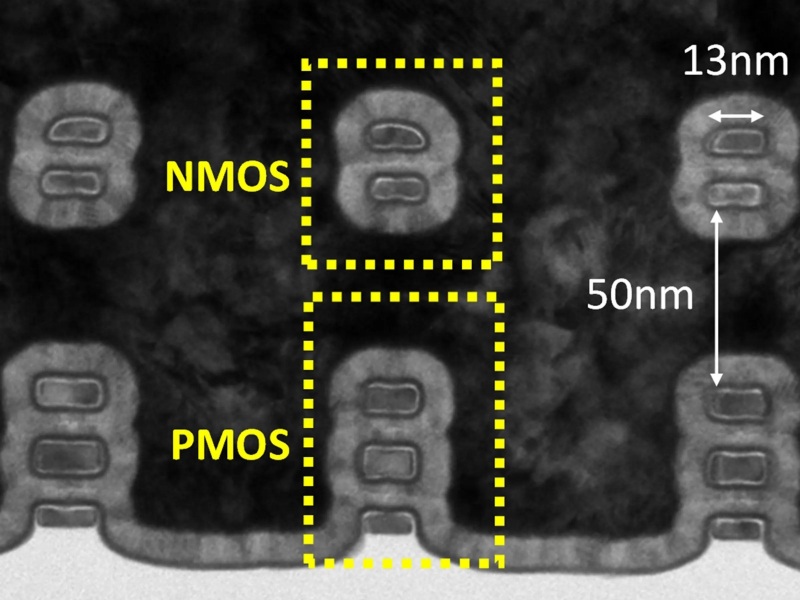

Микрофотография лабораторного образца полупроводниковой микросхемы, у которого транзисторы n-МОП размещаются над комплементарными им p-МОП (источник: Intel) Остаётся теперь выяснить в деталях, каким же образом сверхминиатюрные полупроводниковые компоненты будущих транзисторов формируют при серийном производстве микропроцессоров технически — и за счёт чего чипмейкерам удаётся всё-таки перешагнуть через достигнутый на уровне оптической системы порог предельно допустимого разрешения 82 нм (или ~40 нм, если брать половинную ширину зазора между повторяющимися компонентами). ⇡#Как Левша оправку вытравливалОдно из наиболее эффективных технических ухищрений на этом пути — многопроходная (multiple patterning) обработка заготовки. Базовая процедура фотолитографии на полупроводнике предусматривает однократное экспонирование фоторезиста (photoresist, PR), за которым следуют проявка и смывка, после чего полупроводниковую подложку на обнажившихся участках протравливают (etch) и, наконец, удаляют остатки фоторезиста. Допустим, эта процедура проводится уже на пределе реально достижимого разрешения системы (те самые 82 нм для DUV-фотолитографии). Однако никто не запрещает, точно нацелившись, второй раз проэкспонировать тот же самый образец со сдвигом в половину этого самого предела разрешения — так, чтобы создаваемые при этом на поверхности полупроводника структуры помещались точно между изготовленными за первый проход. Без каких бы то ни было дополнительных усилий сразу выходит сокращение фактической производственной нормы вдвое. Здесь как раз очень помогает тот факт, что базовые структуры в составе полупроводникового чипа — будь это микросхема памяти или логическая — однотипны и довольно равномерно расположены. Грубо говоря, они представляют собой выстроенные шеренгами штрихи Шеффера, а все сложные нетривиальные комбинации из них — логические вентили, сумматоры и т. п. — образуются за счёт соединения между собой в нужном порядке элементов И-НЕ металлическими контактами, выполняемыми уже на более высоких слоях микросхемы и с бóльшим характерным масштабом.

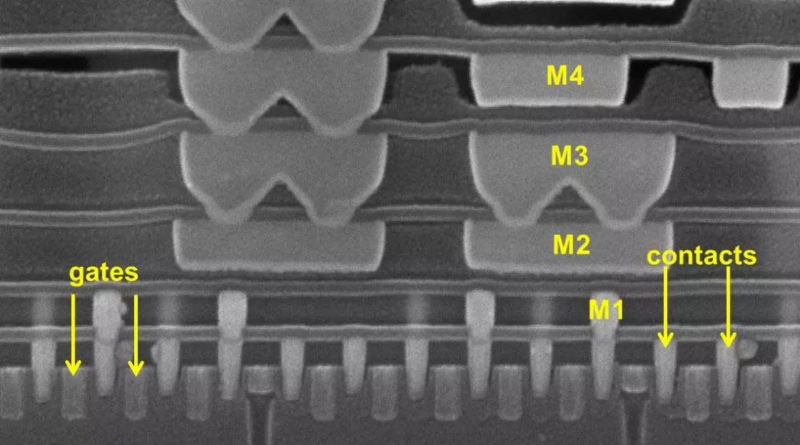

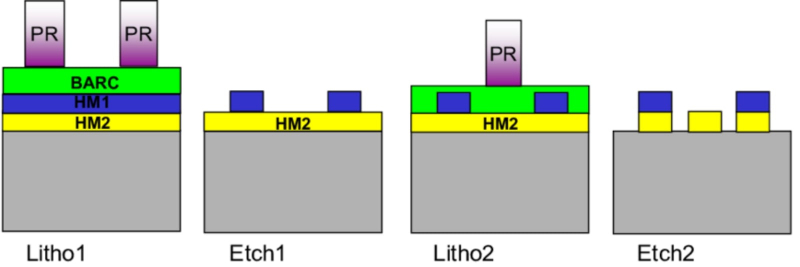

Микрофотография сечения «16-нм» процессора Exynos 7420, литографированного по многопроходной технологии, вдоль одного из рядов плавников FinFET и поперёк транзисторных затворов: показаны сами затворы, подходящие к истокам/стокам контакты и лежащие сверху металлические слои межсоединений (источник: TechInsights) Для реализации двухпроходной фотолитографии разработали несколько методик, предусматривающих использование так называемых жёстких масок (hardmasks). Жёсткими их называют потому, что они должны выдерживать процедуру смывки первичного слоя фоторезиста, так что в их роли не могут выступать гелеподобные по консистенции органические полимеры, применяемые при однопроходном процессе. Более того, вторая жёсткая маска обязана выдерживать протравливание и смывку первой, так что это должны быть ещё и разные по химическим свойствам вещества: карбид и оксид кремния, например. В итоге операция понижения реально достижимого масштаба микроструктур вдвое сводится к последовательности «литография — травление — литография — травление» (lithography-etching-lithography-etching, отсюда аббревиатура LELE).

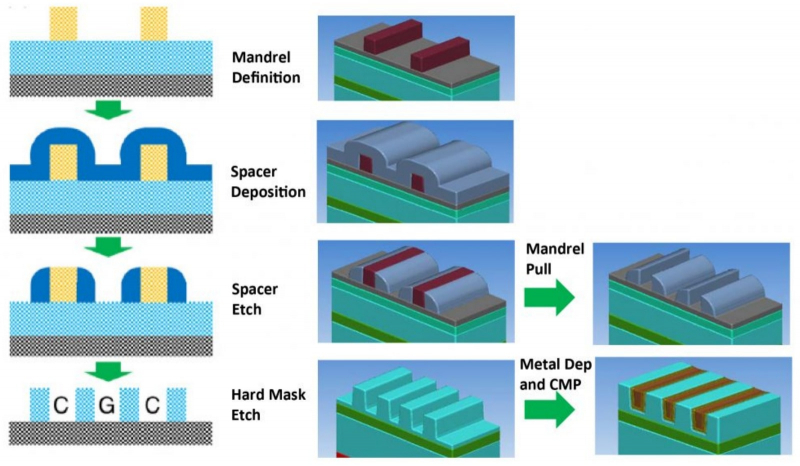

Двухпроходная фотолитография по методу LELE: фоторезист (PR) наносится на особый противоотражающий слой (Bottom Anti-Reflectant Coating, BARC) и две жёсткие маски. После первого цикла ««литография — травление» снова производится нанесение BARC и PR на нужных участках, затем цикл повторяется (источник: IEEE Xplore) Усовершенствованный вариант этого метода — многопроходная литография с самовыравниванием (self-aligned multiple patterning, SAMP). Дело в том, что проэкспонировать кремниевую пластину диаметром 300 мм (стандартная заготовка для DUV-машин) дважды с идеально точным сдвигом всего лишь на десятки нанометров — задача, мягко говоря, технологически сложная. Проще сразу позаботиться о том, чтобы на поверхности полупроводника, покрытой фоторезистом, образовались структуры с характерным шагом вдвое меньшим, чем реально достижимый предел разрешения. Проще это опять-таки благодаря заведомой регулярности таких структур — и, соответственно, применяемых для экспонирования шаблонов. В классическом однопроходном процессе на фоторезисте формируют отдельные узкие полосы, каждая из которых после травления станет зазором между соседними полупроводниковыми рёбрами (те в итоге окажутся гребнями транзисторов FinFET), и потому расстояние между полосами соответствует толщине этих самых рёбер. Шаблон же для SAMP построен так, чтобы через него экспонировался лишь каждый второй зазор между полупроводниковыми рёбрами. Вертикальные структуры, возникающие после проявки и смыва первого слоя фоторезиста, выступают в роли оправок или мандрелей (mandril) — так в слесарном деле называют приспособление в виде слабо сужающегося к одному из торцов конуса для штамповки/формовки кольцевых или цилиндрических деталей, а также для выправки мятых труб.

Двухпроходная фотолитография по методу SADP: формовка оправок на жёсткой маске — нанесение разделителя — травление разделителя и выемка материала оправок — финальное травление жёсткой маски (источник: Lam Research) На стенки этих оправок с использованием тонких методов равномерного осаждения (atomic layer deposition, ALD, или chemical vapor deposition, CVD) наносится буквально атом за атомом слой разделительного материала, образующий словно бы облицовку созданных на пределе разрешения фотолитографа структур. Расстояние между внешними границами соседних облицовок несложно сделать вдвое меньше этого самого предела, зная скорость осаждения облицовочного материала и контролируя время. Тогда после удаления уже самих оправок (в ходе процесса, аналогичного смыву засвеченного фоторезиста, но с другими химикатами) и травления оставшейся не закрытой разделительным материалом поверхности соседние полупроводниковые рёбра будут отстоять одно от другого на расстояние вдвое меньшее, чем реально достижимый на данном литографе процесс. И никакого противоречия с законами физики — просто на помощь оптике пришла изобретательная инженерия. Ставка на SAMP избавляет от необходимости производить два раздельных экспонирования пластины-заготовки с микроскопически точным её сдвигом. Более того: можно и повторять эту процедуру, если озаботиться предварительно нанесением нескольких жёстких масок для формирования оправок, — и два раза, и четыре. В результате если двухпроходный SADP (multiple в аббревиатуре конкретизировано до double) позволяет на базовой DUV-установке достигать зазора между элементами (pitch) примерно в 40 нм вместо 82, то четырёхпроходный SAQP (quadruple) — уже почти 20 нм. При этом толщина полупроводникового гребня (одиночной мельчайшей детали на поверхности подложки) для уже упоминавшегося техпроцесса TSMC «7 нм» составляет 6 нм — кстати, практически столько же, сколько и для предшествующей производственной нормы «10 нм». Так что, в принципе, маркетинговое наименование «7 нм» всё же имеет некий физический смысл, хотя уже и не указывает напрямую на размер главного активного полупроводникового элемента МОП-транзистора — длину его канала.

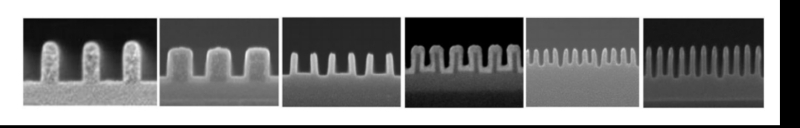

Последовательные микрофотографии поперечных срезов заготовки, литографируемой по методу SAQP, слева направо: формирование оправок — нанесение разделителя — выемка материала оправок верхнего ряда — нанесение нового разделителя на остатки прежнего, выступающие теперь в роли новых оправок, — выемка материала между разделителями — финальное протравливание заготовки до подложки с получением структур шириной 15 нм и дистанцией (pitch) 30 нм (источник: SPIE) Но, как было подчёркнуто не раз, «закон Мура» сформулирован вовсе не для размеров единичного транзистора, а для плотности транзисторов на готовом чипе. Именно поэтому габариты типового полупроводникового элемента не так уж важны: значение имеет то самое расстояние между соседними гребнями (fin pitch, FP) и, в несколько меньшей степени, зазор между соседними металлическими токоведущими дорожками (minimum metal pitch, MMP). Так вот, при переходе от «10-нм» к «7-нм» техпроцессу FP стало меньше примерно на 17% (было 34-36 нм, стало 27-30 нм), MMP — всего-то на 5% (было 36-44 нм, стало 36-40 нм для различных реализаций соответствующих производственных норм у Intel и TSMC). Плотность размещения транзисторов на чипе для воплощённых сегодня в серийных DUV-установках технологических норм составляет 90-102 млн на 1 мм2, и это, судя по всему, уже предел эксимерной лазерной фотолитографии. Именно теперь приходит черёд основанной на принципиально другой оптической схеме технологии EUV, а вместе с ней и совершенно иных физических проблем, технологических находок и ухищрений. Но это уже совсем, совсем другая история.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|