На Североамериканском технологическом симпозиуме 2023 года TSMC выпустила обновление дорожной карты для своих 3-нм техпроцессов — семейства N3. Ожидается, что это семейство станет последним поколением технологических норм TSMC на основе транзисторов FinFET, и на многие годы останется самым плотным техпроцессом, доступным клиентам, которым не нужен более современный техпроцесс на транзисторах GAAFET.

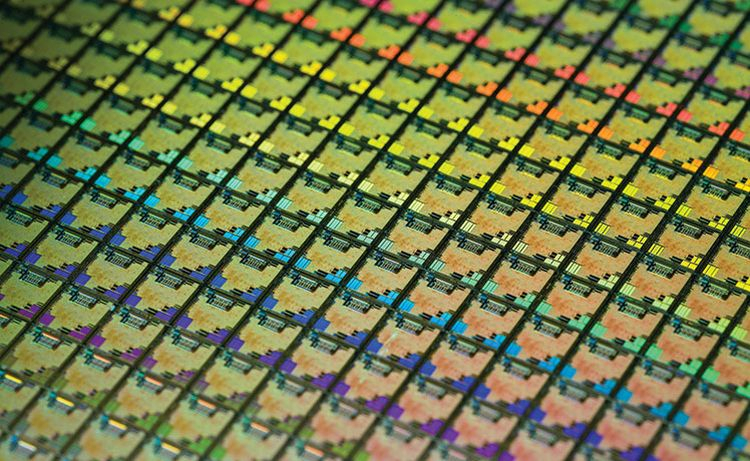

Источник изображения: TSMC

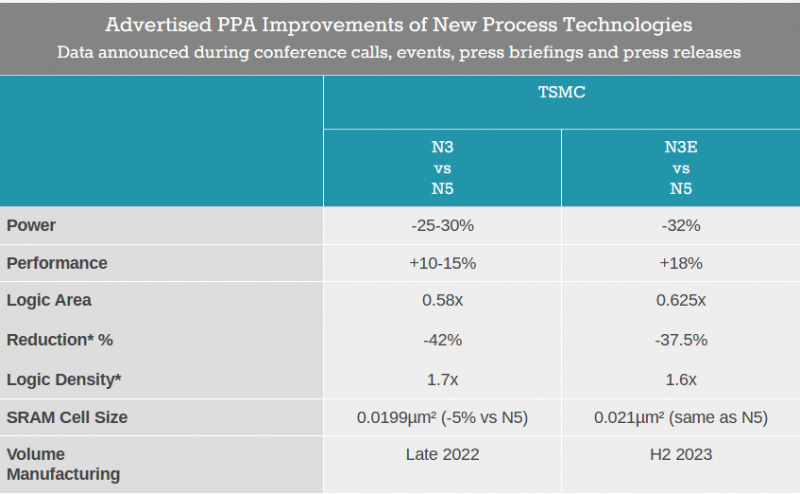

TSMC уже запустила производство 3-нм чипов по технологии N3, но в будущем готовит сразу несколько улучшенных версий данного техпроцесса. По мнению TSMC большинство клиентов, будут использовать упрощённый техпроцесс N3E, разработка которого и в частности достижение целей по производительности идёт согласно графику. N3E использует до 19 слоёв EUV и не полагается на двойную структуру EUV, что снижает его сложность и стоимость. Компромисс заключается в том, что N3E предлагает более низкую плотность, чем стандартная версия N3, и имеет тот же размер ячейки SRAM, что и техпроцесс TSMC N5. Это делает его несколько менее привлекательным для тех клиентов, которые стремятся к увеличению плотности или сокращению площади чипов.

Источник изображения: Anandtech

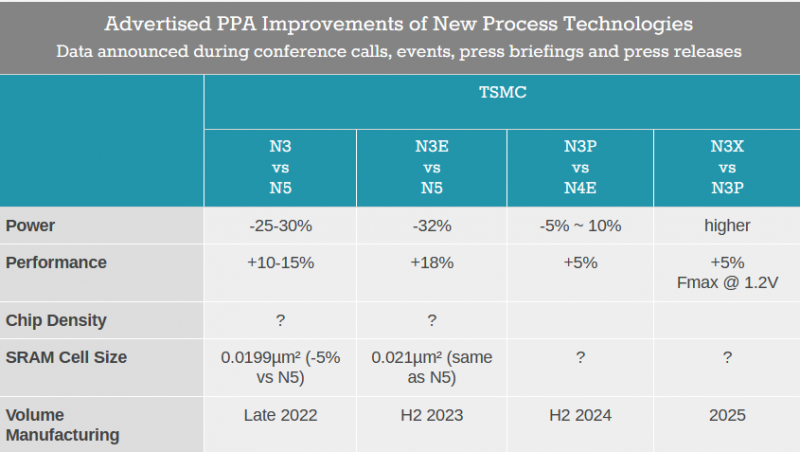

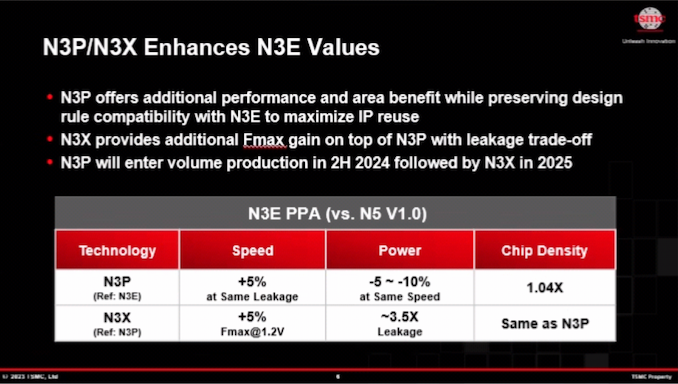

Вслед за N3E компания TSMC продолжит оптимизацию плотности транзисторов семейства N3 в техпроцессе N3P, который будет основываться на N3E, предлагая улучшенные характеристики. Усовершенствованный техпроцесс позволит разработчикам микросхем либо увеличить производительность на 5 % при том же потреблении, либо снизить энергопотребление на 5–10 % при тех же тактовых частотах. Новый техпроцесс также увеличит плотность транзисторов на 4 % для «смешанной» конструкции микросхемы, которую TSMC определяет как микросхему, состоящую из 50 % логики, 30 % SRAM и 20 % аналоговых схем.

Источник изображения: Anandtech

В конце своего выступления TSMC рассказала о своём самом производительном 3-нм техпроцессе — N3X. По сравнению с N3P, N3X будет предлагать как минимум на 5 % более высокую тактовую частоту. TSMC утверждает, что N3X будет поддерживать напряжение 1,2 В, что является довольно экстремальным для техпроцесса класса 3 нм.

Источник изображения: TSMC

При этом компания прогнозирует колоссальное увеличение утечки мощности на 250 % по сравнению с более сбалансированным узлом N3P — это подчёркивает, почему N3X на самом деле можно использовать только для процессоров класса HPC.

Компания заявляет, что технология N3P будет готова к производству во второй половине 2024 года, а последняя версия техпроцесса семейства N3 — технология N3X — в текущей дорожной карте TSMC будет готова к производству в 2025 году.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться