Аналитики TrendForce ожидают, что в 2023-м и 2024-м годах на рынке будет наблюдаться повышенный спрос на высокопроизводительную память HBM. На фоне этого эксперты прогнозируют увеличение объёмов выпуска чипов с использованием передовых технологий упаковок на 30–40 %.

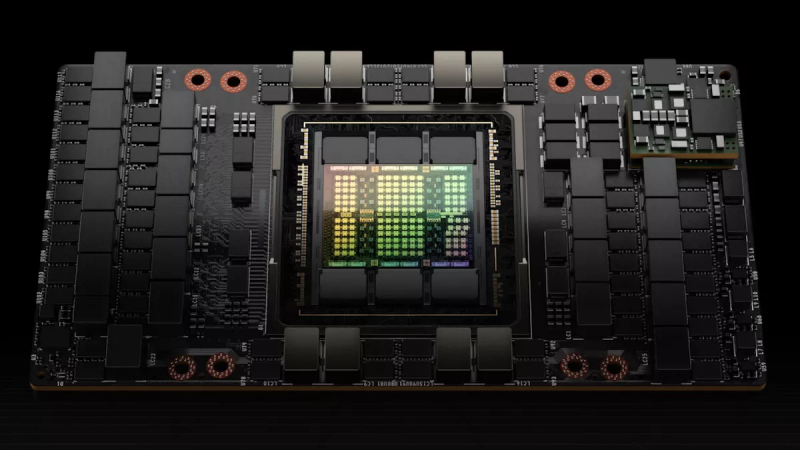

Источник изображения: NVIDIA

Взрывной рост популярности приложений генеративного ИИ, таких как чат-боты, привёл к значительным изменениям на серверном рынке в 2023 году. Ключевые западные поставщики услуг в области информационных технологий, такие как Microsoft, Google, AWS, а также китайские компании Baidu и ByteDance вкладывают значительные средства в передовые высокопроизводительные серверы для обучения и оптимизации своих моделей ИИ.

Для повышения эффективности ИИ-серверов и увеличения пропускной способности их подсистем памяти ведущие производители микросхем для ИИ, такие как NVIDIA, AMD и Intel, активно внедряют высокопроизводительную память HBM в свои продукты. В частности, ускорители вычислений NVIDIA A100 и H100 предлагают до 80 Гбайт памяти стандартов HBM2e и HBM3. В своём самом передовом ускорителе Grace Hopper производитель использует стеки памяти HBM с увеличенным на 20 % (до 96 Гбайт) объёмом. Ускорители вычислений MI300 от компании AMD тоже оснащаются памятью HBM3. Те же модели MI300A предлагают 128 Гбайт памяти, а более передовые MI300X — до 192 Гбайт указанной памяти. Ожидается, что компания Google в рамках расширения своей ИИ-инфраструктуры укрепит сотрудничество с Broadcom и концу текущего года начнёт производство чипа-ускорителя искусственного интеллекта TPU, в состав которого также будет входить память HBM.

По прогнозам TrendForce, совокупный объём памяти HBM, использующейся в ускорителях вычислений ИИ, включая NVIDIA H100 и A100, AMD MI200 и MI300, а также Google TPU, составит 290 млн гигабайт, что на 60 % больше, чем годом ранее. В 2024 году этот рост сохранится на уровне 30 или более процентов.

В сфере ИИ и HPC также растёт спрос на передовые технологии упаковки чипов. Преобладающим выбором для производства серверных чипов ИИ является технология Chip on Wafer on Substrate (CoWoS) компании TSMC. Технология упаковки CoWoS включает два этапа: CoW и oS. На этапе CoW между собой объединяются различные логические микросхемы (центральные и графические процессоры, ASIC), а также память HBM. На этапе oS элементы сборки CoW устанавливаются на подложку чипа. Впоследствии формируется SoC, которая интегрируется в серверную материнскую плату, на основе которой создаётся ИИ-платформа с сетевым оборудованием, подсистемой памяти, источниками питания и прочими компонентами.

Эксперты прогнозируют, что на фоне высокого спроса на передовые ИИ-чипы в целом и HBM-память в частности ежемесячный объём выпуска микросхем с использованием технологии упаковки CoWoS компании TSMC к концу 2023 года увеличится до 12 тыс. единиц. С начала 2023 года спрос на CoWoS вырос почти на 50 %, что обусловлено высокой популярностью ускорителей NVIDIA A100 и H100, а также ИИ-серверов на их основе. В то же время на фоне растущего интереса к CoWoS со стороны AMD, Google и других компаний количество свободных линий для производства чипов с CoWoS, вероятно, будет ограничено во второй половине текущего года, считают аналитики. Высокий спрос на CoWoS сохранится как минимум до 2024 года, а поэтому в следующем году ожидается увеличение соответствующих доступных мощностей на 30–40 % с учётом готовности необходимого оборудования.

Если высокий спрос на технологии ИИ сохранится, то вполне вероятно, что та же NVIDIA может рассмотреть возможность использования альтернативных передовых упаковок для производства чипов. Такие, например, предлагают компании Amkor и Samsung.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018