|

Опрос

|

реклама

Быстрый переход

Пока мир гонится за ИИ-чипами, китайская SMIC зарабатывает на зрелых техпроцессах

15.05.2026 [13:53],

Павел Котов

Крупнейший в Китае контрактный производитель микросхем SMIC сообщил, что у него выросло число зарубежных заказчиков — из-за мирового бума технологий искусственного интеллекта подрядчики в других странах всё чаще оказываются заняты.

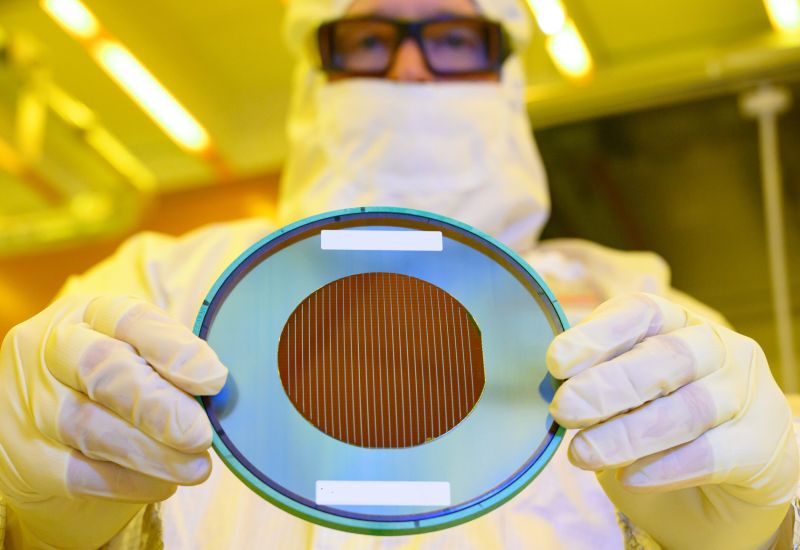

Источник изображения: smics.com «В Китае по-прежнему реализуется довольно много проектов, компании расширяют производственные мощности. Они — одни из немногих, кто располагает свободными производственными мощностями, и мы отмечаем, как многие зарубежные клиенты перенаправляют свои заказы на производство в Китай. Как крупнейший отечественный производитель чипов, SMIC, вероятно, имеет здесь наибольшую долю. Это происходит повсеместно», — рассказал гендиректор компании Чжао Хайцзюнь (Zhao Haijun). У подрядчиков в других странах сокращаются доступные мощности для производства продукции, связанной с ИИ, памятью и другими высокоскоростными компонентами, а часть продукции они вообще перестали выпускать. SMIC же активно наращивает мощности в расчёте на высокий спрос со стороны китайских разработчиков чипов. По сравнению с прошлым годом компания ожидает роста амортизационных расходов на 30 %; только в I квартале этот показатель вырос на 26 % по сравнению с аналогичным периодом прошлого года. Компания добавила 9000 эквивалентных 12-дюймовых пластин. Коэффициент использования производственных мощностей в отчётный период составил 93 %, немного снизившись квартал к кварталу. «В IV квартале прошлого года производители смартфонов сократили заказы из-за опасений по поводу нехватки вспомогательных чипов памяти, и отчасти это влияние сказалось в I квартале. В то же время в I квартале начали работать новые заводы, что увеличило общую мощность и создало впечатление более низкой загрузки», — добавил гендиректор SMIC. Крупнейшим рынком для SMIC остался Китай, который принёс ей 89 % выручки, на США пришлись 9 %. В минувшем квартале компания отгрузила 2,5 млн эквивалентных 8-дюймовых пластин — столько же, сколько и тремя месяцами ранее. В этом году доля китайских производителей в сегментах от 22 до 40 нм достигнет 37 %, а в 2027 году вырастет до 41 % — в 2025 году этот показатель составлял 32 %. «Поскольку спрос на связанные с ИИ чипы и периферийные приложения в следующем году будет продолжать расти, мощности по производству не связанных с ИИ продуктов могут ещё больше сократиться. Считаем, что это долгосрочная тенденция», — отметил Чжао Хайцзюнь. Samsung начала экстренно сокращать производство перед массовой забастовкой

15.05.2026 [11:15],

Владимир Фетисов

Samsung Electronics готовится к 18-дневной всеобщей забастовке, которая запланирована профсоюзными организациями работников компании на 21 мая. На этом фоне вендор вводит меры на случай непредвиденных обстоятельств для минимизации вероятности сбоев, в том числе корректирует процесс производства полупроводниковой продукции и ограничивает объём поставки кремниевых пластин.

Источник изображения: Samsung По мнению отраслевых экспертов, потенциальное сокращение производства может нарушить глобальную цепочку поставок чипов. В сообщении сказано, что Samsung вводит меры управления в чрезвычайных ситуациях, поскольку вероятность начала забастовки на следующей неделе возросла, а последний раунд переговоров между руководством компании и представителями профсоюзов завершился без прогресса. Профсоюзы отвергли возможность дальнейших переговоров и подтвердили свои требования. Поскольку забастовка может вызвать масштабные сбои в производстве и проблемы с качеством из-за нехватки рабочей силы в полупроводниковом подразделении Samsung, компания рассматривает возможность проведения процесса постепенного снижения производства. На производстве полупроводниковой продукции обычно требуется упреждающая корректировка производственных операций как минимум за неделю, поскольку резкая остановка производственных процессов может привести к огромным потерям. «В отличие от других отраслей, производителям полупроводников необходимо начинать корректировать объёмы производства и меры контроля качества как минимум за неделю до забастовки, чтобы минимизировать ущерб. Для поддержания контроля качества производство необходимо масштабировать заранее перед забастовкой», — рассказал один из отраслевых экспертов. Официальные представители Samsung заявили, что компании необходимо скорректировать подачу новых кремниевых пластин и свой продуктовый портфель в пользу продуктов с высокой маржой, таких как чипы памяти HBM. Вместе с этим компания предложила профсоюзам провести ещё один раунд переговоров.

Источник изображения: Samsung Electronics По данным источника, Samsung направила официальное письмо Объединённому профсоюзу Samsung Electronics (SELU) и Национальному объединённому профсоюзу Samsung Electronics (NSEU), которые ведут переговоры с компанией совместно. В письме руководство вендора предложило провести дополнительный раунд переговоров. «Во время недавней посреднической сессии, организованной Национальной комиссией по трудовым отношениям (LRC), руководство и профсоюзы изложили свои позиции, но не смогли достичь соглашения. Компания предлагает прямой диалог между руководством и профсоюзами. Мы просим профсоюзы положительно отнестись к данному предложению и дать ответ», — сказано в письме компании. Возможная дата и формат нового раунда переговоров, озвучены не были. Ранее профсоюзы отказались от дальнейших переговоров, если руководство Samsung не примет их требования. «Если компания искренне хочет диалога, она должна предложить более конкретные планы <…> Мы готовы участвовать в переговорах, если компания продемонстрирует готовность обсуждать прозрачность бонусов, отмену верхнего предела выплат и институционализацию бонусной системы», — говорится в заявлении профсоюзов. Напомним, стороны не достигли соглашения по вопросу институционализации бонусной системы компании: руководство отвергло требования профсоюзов о предоставлении юридических гарантий выделения 15 % операционной прибыли на премии по результатам работы, а также об отмене верхнего предела бонусных выплат. Руководство Samsung хочет сохранить действующую практику, в рамках которой на бонусы направляется сумма, эквивалентная 10 % операционной прибыли, без фиксации этого соотношения в коллективном договоре. В дополнение к этому руководство компании отвергло предложение об отмене верхнего предела бонусных выплат. По состоянию на вечер четверга 44 816 членов профсоюзов Samsung выразили готовность присоединиться к забастовке, тогда как днём ранее об этом заявляли около 42 тыс. человек. Компания ожидает, что в случае, если все выразившие желание бастовать работники примут участие в забастовке, может возникнуть ситуация, сопоставимая с полномасштабной остановкой производства. По оценке отраслевых экспертов, это может привести к потерям до 40 трлн вон ($26,8 млрд), а в случае полной остановки производственных линий — до 100 трлн вон. Гулять так гулять: TSMC предсказала, что мировое производство чипов раздуется до $1,5 трлн к 2030 году

14.05.2026 [07:38],

Алексей Разин

На протяжении последних нескольких лет многие эксперты, включая руководство TSMC, называли $1 трлн ориентиром для оборота мировой полупроводниковой отрасли по состоянию на конец десятилетия. Эта цель долго время казалась весьма амбициозной, но теперь TSMC поднимает планку сразу до $1,5 трлн без пересмотра сроков.

Источник изображения: TSMC Агентству Reuters удалось ознакомиться с материалами, которые TSMC подготовила для выступления своих представителей на техническом симпозиуме. Новый ориентир призван оправдать увеличивающиеся темпы экспансии производства чипов самой TSMC. Распределение выручки по состоянию на 2030 год будет выглядеть следующим образом: 55 % из полутора триллионов долларов США придутся на ИИ и высокопроизводительные вычисления, 20 % достанутся смартфонам, а 10 % займёт автомобильная электроника. В прошлом и текущем году TSMC ускорила расширение производственных мощностей, в этом году она собирается построить девять предприятий по обработке кремниевых пластин и упаковке чипов. В сегменте 2-нм техпроцесса и его более продвинутых преемников TSMC в ближайшие два года будет наращивать производственные мощности в среднем на 70 % в год. Мощности по упаковке чипов с использованием метода CoWoS в период с 2022 по 2027 годы будут в среднем расти на 80 % в год. Эти услуги востребованы в сегменте ИИ, особенно при производстве ускорителей Nvidia. Спрос на кремниевые пластины, содержащие чипы для ИИ-ускорителей, в период с 2022 по 2026 годы вырастет в 11 раз, по прогнозам TSMC. В Аризоне у TSMC уже функционирует первое предприятие, выпускающее 4-нм чипы. Второе уже построено, во второй половине текущего года оно начнёт принимать оборудование. Ведётся строительство третьего предприятия, в текущем году TSMC рассчитывает приступить к строительству четвёртого и возведению первой американской площадки по тестированию и упаковке чипов. Она позволит исключить необходимость возить обработанные кремниевые пластины на Тайвань для их превращения в готовые чипы для американских заказчиков. По итогам этого года первое американское предприятие TSMC в Аризоне увеличит объёмы выпуска продукции в 1,8 раза, уровень выхода годной продукции на его конвейере уже сопоставим с тайваньскими площадками. Компания купила большой участок земли в Аризоне по соседству с уже строящимися предприятиями, рассчитывая использовать его аналогичным образом в будущем. В Японии совместное предприятие JASM выпускает 22-нм и 28-нм чипы, его вторая фаза будет ориентирована на производство 3-нм чипов. В Германии TSMC при участии местных партнёров возводит предприятие, которое на первых порах займётся выпуском 28-нм и 22-нм чипов, а позже приступит к производству 16-нм и 12-нм продукции. Рынок материалов для производства полупроводниковых компонентов в прошлом году вырос на 6,8 % до $73,2 млрд

13.05.2026 [08:07],

Алексей Разин

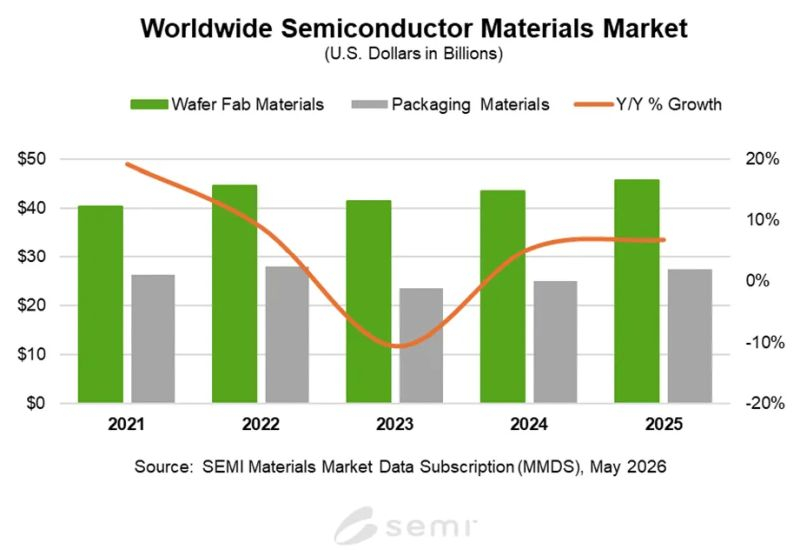

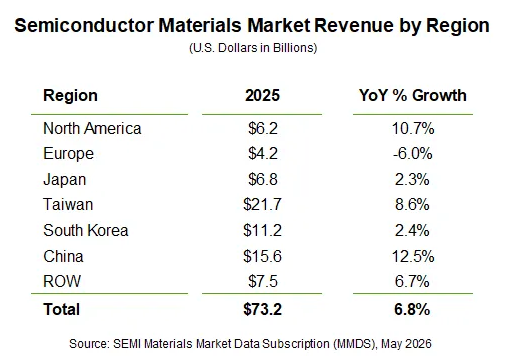

Бум искусственного интеллекта с осени 2022 года увеличивает спрос на полупроводниковые компоненты, поэтому закономерно, что и материалы для их производства пользуются более высокой популярностью. В прошлом году выручка от их реализации увеличилась на 6,8 % до $73,2 млрд.

Источник изображений: SEMI Как гласит отчёт отраслевой ассоциации SEMI, рост выручки наблюдался как по материалам, необходимым для обработки кремниевых пластин, так и по сегменту упаковки чипов. Передовые техпроцессы пользовались спросом, а технологии упаковки чипов становились всё сложнее с учётом концентрации роста рынка в сегменте высокопроизводительных вычислений для ИИ. Отдельно материалы для обработки кремниевых пластин увеличили выручку поставщиков на 5,4 % до $45,8 млрд. Сегмент материалов для литографии вообще продемонстрировал рост выручки на двузначное количество в процентах. Сегмент упаковки чипов продемонстрировал рост выручки от реализации материалов на 9,3 % до $27,4 млрд. Помимо прочего, выручку толкали вверх мировые цены на золото, которое используется при изготовлении контактов микросхем.  В географическом выражении Тайвань продолжает оставаться крупнейшим рынком сбыта материалов для производства чипов на протяжении 16 лет подряд. Профильная выручка в прошлом году выросла на 8,6 % до $21,7 млрд. Китай с ростом выручки на 12,5 % до $15,6 млрд занимает второе место, но опережает все прочие регионы по динамике роста. Южная Корея благодаря концентрации производителей памяти занимает третье с $11,2 млрд выручки, но темпы роста здесь ограничены 2,4 %. Северная Америка в этом рейтинге со своими $6,2 млрд уступает даже Японии ($6,8 млрд), но демонстрирует хорошую динамику в виде роста выручки на 10,7 %. Европа оказалась единственным регионом, в котором профильная выручка сократилась на 6 % до $4,2 млрд. Переговоры профсоюза и руководства Samsung провалились — забастовка намечена на 21 мая

13.05.2026 [05:48],

Алексей Разин

Подключение к переговорам между руководством Samsung и профсоюзом сотрудников медиатора в лице представителей правительственной комиссии не способствовало прогрессу, как вынужден был заявить лидер объединения работников компании. Всеобщая забастовка сотрудников Samsung не снимается с повестки.

Источник изображения: Samsung Electronics О том, что переговоры носили напряжённый характер, свидетельствует хотя бы тот факт, что своё заявление об их итогах глава профсоюза Samsung Electronics Цой Сон Хо (Choi Seung-ho) сделал в среду в три утра по местному времени. Работодатель, по его словам, не прислушался к требованиям профсоюза пересмотреть схему оплаты труда, которая сейчас ограничивает размер годовой премии на уровне 50 % от зарплаты за период. Профсоюз настаивал, что на премиальные выплаты сотрудникам необходимо направлять до 15 % операционной прибыли Samsung, и делать это ежегодно. Как признался Цой, ни один из вопросов, которые профсоюз вынес на переговоры, не был решён руководством Samsung Electronics. Профсоюз оставляет за собой право инициировать 21 мая всеобщую забастовку, которая будет длиться 18 дней. Samsung в результате понесёт серьёзные убытки, утратит доверие клиентов и уступит часть рыночных позиций конкурентам, как ожидается. При этом цены на память вырастут везде, поскольку именно Samsung является её крупнейшим производителем в мире. Глава профсоюза дал понять, что не намерен до 21 мая возобновлять переговоры с руководством компании, но если оно выступит с нужным предложением, то он готов его выслушать. Представители правительственной комиссии, которая на этой неделе выступала медиатором в споре сторон, пытались предложить различные сценарии решения спора, но в итоге отстранилась от процесса, признав слишком большой разрыв между позициями участников переговоров. Кроме того, профсоюз потребовал завершить переговоры, видя, что не находит понимания у руководства. Последнее отделалось кратким комментарием о намерениях продолжать «искренний диалог с профсоюзом в надежде предотвратить худший сценарий». Министерство финансов страны также выразило надежду, что до забастовки дело не дойдёт. По некоторым данным, руководство Samsung предлагало профсоюзу распределять в виде премий сотрудникам не более 10 % годовой операционной прибыли, а также выплатить единовременную компенсацию в этом году. Провал очередного этапа переговоров вызвал снижение капитализации Samsung Electronics на $66 млрд или 6 %. Производству чипов грозит новый дефицит — война на Ближнем Востоке спровоцировала нехватку цистерн для гелия

12.05.2026 [14:41],

Алексей Разин

Кризисные ситуации на мировом рынке полупроводниковых компонентов развиваются порой по непредсказуемому сценарию, и если до недавних пор на слуху была история с дефицитом гелия из-за войны на Ближнем Востоке, то теперь она получила развитие. Производству чипов далеко за пределами региона угрожает нехватка специализированных резервуаров для транспортировки гелия.

Источник изображения: Unsplash, Joshua J. Cotten Как поясняет Nikkei Asian Review, в мире всего несколько компаний, выпускающих сосуды для безопасной транспортировки гелия при сверхнизких температурах и большом давлении. Поскольку из того же Катара до начала военных действий в Иране и окрестностях гелий экспортировался на регулярной основе, в регионе скопился некоторый запас таких цистерн, ранее находившихся в обращении. Теперь эти сосуды не могут быть вывезены из района боевых действий, и для поставки гелия из других стран просто не хватает свободных ёмкостей. Производители резервуаров для транспортировки гелия не спешат компенсировать это увеличением объёмов выпуска своей продукции, поскольку это не только занимает время, но и создаёт некоторую неопределённость с дальнейшей судьбой «излишних» сосудов в случае скорой нормализации ситуации. На долю Катара приходилось до трети поставок гелия на мировой рынок, но после начала боевых действий на Ближнем Востоке экспорт этого газа, востребованного при производстве полупроводниковых компонентов, прекратился из этой страны. Россия, как отмечает Nikkei, ограничила экспорт гелия ради стабилизации внутреннего рынка, хотя исторически могла претендовать на 9 % мирового рынка. Американские поставщики контролируют до 43 % мирового рынка, но азиатским производителям чипов их сырьё наверняка будет обходиться дороже катарского. По данным TechInsights, из-за проблем на Ближнем Востоке не менее 14 % экспорта гелия из Катара пострадают в перспективе ближайшего года или двух. В Китае цены на гелий после начала боевых действий в Иране выросли до десяти раз. Российские поставки тоже прекратились. Если большие производители чипов ещё могут закупать гелий с запасом, то мелким участникам рынка порой ничего не достаётся вообще. Многие специализированные растворители, используемые при производстве чипов, с марта выросли в цене как минимум на 40 %, включая метанол, ксилол и другие вещества, применяемые в отрасли. Подложки для микросхем и печатные платы производятся с применением различных видов смол, которым нужны растворители. При этом бум ИИ повышает цены на специальные виды стекловолокна, которые применяются при производстве печатных плат. Цены растут на десятки процентов буквально ежеквартально. Дорожают и металлы вроде меди, никеля и золота, без которых производство чипов и печатных плат тоже не обходится. Участникам рынка сложно перекладывать растущие расходы на плечи потребителей, поэтому у многих из них прибыли стремительно падают. Если конфликт на Ближнем Востоке затянется надолго, это негативно скажется на всей мировой экономике и различных отраслях промышленности, пусть и не сразу. Рекордными в текущем году стали цены на паравольфрамат аммония, который необходим при изготовлении вольфрама. Соединения этого металла входят в состав некоторых технических газов, применяемых при производстве микросхем, а ещё с его помощью легируют сплавы, из которых изготавливаются свёрла, используемые при механической обработке печатных плат. Нефтехимическая промышленность в целом снабжает производителей полупроводниковых компонентов многими видами расходных материалов, и конфликт на Ближнем Востоке усугубляет ситуацию с их доступностью. Даже если военные действия прекратятся, инфляционное давление на цепочки поставок уже нельзя будет остановить. На фоне роста капитальных расходов и фонда оплаты труда возникают все условия для подорожания чипов, как отмечают производители. Профсоюз Samsung назвал условие отмены всеобщей забастовки, которая может обернуться потерями до $680 млн в день

12.05.2026 [10:29],

Алексей Разин

На этой неделе к переговорам между руководством Samsung Electronics и профсоюзом работников компании подключился медиатор в лице Центральной комиссии по трудовым отношениям в составе Министерства занятости и труда Южной Кореи. Глава профсоюза сотрудников Samsung при этом заявил, что его единомышленники готовы отказаться от всеобщей забастовки, если принципы назначения премий в компании станут более прозрачными.

Источник изображения: Samsung Electronics Напомним, помимо повышения базового уровня оплаты труда на 7 %, профсоюз Samsung требует распределения до 15 % операционной прибыли компании за год между сотрудниками в качестве премии. Сейчас предельная сумма премии ограничена 50 % годовой зарплаты, но в условиях бума ИИ прибыль Samsung кратно увеличилась за год, и наличие подобных ограничений кажется представителям профсоюза несправедливым. Сейчас членами профсоюза являются 70 000 сотрудников Samsung, что превышает половину списочной численности персонала компании. Если нынешний этап переговоров не приведёт к желаемому для профсоюза результату, то всеобщая забастовка сотрудников Samsung может продлиться с 21 мая по 7 июня. Профсоюз оценивает потенциальные потери компании от каждого дня забастовки в $680 млн, и это без учёта затрат времени и средств на последующее восстановление нормальной работы оборудования, на котором выпускаются чипы. Когда в конце прошлого года стартовали переговоры с работодателем об увеличении премиальных выплат, в профсоюзе никто и не думал, что дело дойдёт до всеобщей забастовки. Лидера профсоюза Цоя Сон Хо (Choi Seung-ho) напрягает непрозрачность процесса принятия решений руководством Samsung в сфере назначения премий и зарплат, а также повышения по карьерной лестнице. В 2023 году полупроводниковое подразделение Samsung несло убытки, рядовые сотрудники не получили годовых премий, но руководители их не лишились. Перекосы в сфере оплаты труда сейчас приводят к тому, что сотрудники Samsung массово переходят на работу в SK hynix, где премии выше. За четыре месяца с декабря прошлого года более 400 членов профсоюза Samsung перешли на работу в SK hynix. Цой подчеркнул, что профсоюз Samsung не намерен сближаться с политическими партиями Южной Кореи, как это делают некоторые профессиональные объединения сотрудников других компаний. Он при этом ратует за успех национальной полупроводниковой промышленности в целом и вспоминает, что когда в августе 2017 года он получил работу в Samsung, его родители буквально плакали от счастья. Samsung глава профсоюза продолжает считать «превосходной компанией». TSMC готова вложить $250 млрд в производство чипов в США, несмотря на проблемы

12.05.2026 [08:40],

Алексей Разин

Первоначально реализуемый под нажимом американских властей проект по организации производства передовых чипов в Аризоне приносил TSMC только убытки, но недавно первое предприятие в этом штате вышло в прибыль. Компания поверила в перспективы данного проекта, теперь готова расширить присутствие в США и вложить до $250 млрд, но специфические трудности всё же сохраняются.

Источник изображения: TSMC К таковым можно отнести, по словам тайваньских чиновников, на которые ссылается TrendForce, проблемы с инженерной инфраструктурой (водоснабжением, в частности), сложности с согласованиями, визовые ограничения и нехватку квалифицированной рабочей силы в США. Для ускорения отладки технологических процессоров на предприятии в Аризоне TSMC изначально направила в США около 1000 инженеров с Тайваня, но у них скоро истекает срок действия трёхлетнего контракта, и не факт, что в новых условиях компании удастся согласовать продление виз для всех из них. Кроме того, компенсировать отток тайваньских специалистов за счёт местной рабочей силы всё равно не удастся. Во второй половине следующего года TSMC собирается наладить в Аризоне выпуск 3-нм продукции, для этого в корпусе P2 уже монтируется оборудование. Корпус P3 находится на этапе возведения фундамента, а по площадкам P4 и AP1 ведутся согласования с американскими регуляторами. В целом, приобретённый TSMC участок по соседству с уже существующими в Аризоне предприятиями позволяет серьёзно расширять локальное производство. Официально TSMC взяла на себя обязательства вложить в экономику США до $165 млрд, но эта сумма может вырасти до $250 млрд, если всё пойдёт по плану. В идеале TSMC хотела бы возвести в Аризоне технопарк, сопоставимый с находящимся в тайваньском Синьчжу. Как отмечает в своём материале The Wall Street Journal, конъюнктура мирового рынка услуг по контрактному производству чипов пока благоволит TSMC. Американские техногиганты в этом году намерены направить на расширение своих вычислительных мощностей до $725 млрд, немалая часть этих средств достанется TSMC. Одна только Nvidia располагает обязательствами по выкупу продукции на сумму $95 млрд, это заметно больше тех $16 млрд, которые наблюдались два года назад. Капитальные затраты TSMC в этом году поднимет до $56 млрд, но её выручка при этом увеличивается опережающими темпами — в 2026 году она должна увеличиться на 30 % как минимум, по прогнозам руководства компании. Норма прибыли TSMC увеличилась в первом квартале с 59 до 66 % в годовом сравнении. Выпуск 3-нм чипов, которые на данном этапе жизненного цикла уже могут считаться относительно зрелыми, будет налажен в США и Японии, что позволит не только лучше удовлетворять спрос со стороны местных заказчиков, но и наращивать выручку на волне бума ИИ. При этом конкурентная угроза со стороны Samsung, Intel и Rapidus в сфере выпуска 2-нм чипов пока не так осязаема, чтобы руководство TSMC всерьёз озаботилось перспективами снижения спроса на свои услуги. SK hynix может привлечь Intel вместо TSMC к выпуску памяти HBM4

11.05.2026 [13:48],

Алексей Разин

Если Samsung Electronics располагает вертикально интегрированным бизнесом, в составе которого есть подразделение по контрактному производству чипов, то SK hynix приходится при производстве передовой памяти класса HBM сильно полагаться на партнёров. Одним из них может стать Intel со своей технологией EMIB.

Источник изображения: Samsung Electronics Как отмечает ZDNet, к этой методике упаковки чипов в исполнении Intel как раз присматривается SK hynix, планируя найти ей применение при производстве памяти поколения HBM4. Намерений одной только SK hynix в этой сфере мало — её заказчики также не должны возражать, чтобы память для них упаковывалась на предприятиях корпорации Intel. До сих пор SK hynix полагалась на TSMC и её метод упаковки CoWoS, но пределы возможностей последнего постепенно достигаются, а потому производители чипов начинают присматриваться к альтернативам, и одной из них может стать EMIB в исполнении Intel. Монолитный кристалл, который в состоянии выпустить TSMC, имеет площадь не более 830 мм2, а многокристальная упаковка типа 2.5D позволяет раздвинуть пределы компоновки. Считается, что будущие поколения HBM будут гораздо сильнее учитывать пожелания конкретных разработчиков ИИ-ускорителей по интеграции памяти, поэтому SK hynix вынуждена расширять круг своих партнёров в сфере передовых методов упаковки чипов. Исследовательская работа в направлении использования EMIB со стороны SK hynix уже ведётся, как сообщают источники. Китайские производители чипов могут заработать на буме ИИ даже без передовых техпроцессов, уверен глава SMIC

11.05.2026 [13:13],

Алексей Разин

Не секрет, что крупнейший контрактный производитель чипов в Китае — компания SMIC, давно находится под прицелом американских санкций, а потому лишена доступа к передовому оборудованию, позволяющему выпускать чипы по технологии тоньше 7 нм. Основатель SMIC уверен, что такое положение дел не мешает китайским производителям успешно развиваться в условиях бума ИИ.

Источник изображения: SMIC Комментарии Ричарда Чана (Richard Chang) приводит издание STAR Market Daily. По его мнению, китайская полупроводниковая отрасль в целом сильна своими специализированными техпроцессами и масштабами производства. Прежде всего, бум ИИ так или иначе подогревать спрос на широкий ассортимент полупроводниковых компонентов, а не только передовые техпроцессы. Для строительства ЦОД нужны компоненты для материнских плат и блоков питания, все они выпускаются и китайскими производителями тоже. В натуральном выражении, по словам основателя SMIC, на передовые техпроцессы сейчас приходится менее 20 % объёмов мировой полупроводниковой продукции. Более 80 % формируют чипы, выпускаемые по зрелым и специализированным техпроцессам. Здесь-то как раз и закрепились китайские производители полупроводниковых компонентов. Тем более, что тайваньские конкуренты поднимают цены и мигрируют на более совершенные техпроцессы, освобождая нишу для китайских производителей чипов. Со второй половины прошлого года в Китае активизировалась обработка 300-мм кремниевых пластин с использованием 90-нм и более грубых техпроцессов. Кроме того, проявление ИИ-бума заключается и в росте спроса на периферийные вычисления: умные устройства, промышленное оборудование, автомобильные системы автопилота и роботы требуют огромного количества чипов, и основную их часть можно выпускать по зрелым техпроцессам. Китайским производителям это позволит неплохо заработать даже в условиях ограниченности доступа к передовому зарубежному оборудованию. Apple сохранит высокую зависимость от TSMC, поскольку та будет выпускать по 2-нм технологии модемы 5G

11.05.2026 [07:07],

Алексей Разин

Новость о вероятном сотрудничестве Intel и Apple в сфере контрактного производства процессоров для второй из них взбудоражила рынок и способствовала росту курса акций первой, но осведомлённые источники считают нужным подчеркнуть, что сотрудничество Apple и TSMC сохранится. По крайней мере, эта компания будет выпускать по 2-нм технологии модемы 5G разработки Apple.

Источник изображения: Apple Об этом сообщает тайваньское издание Economic Daily News, на которое ссылается TrendForce. По данным источника, 5G-модемы Apple собственной разработки будут лежать в основе будущих моделей iPhone, iPad и Watch, они заменят собой решения Qualcomm. Поскольку целевые категории устройств будут достаточно многочисленными, выпускаться данные модемы будут сотнями миллионов штук в год. Выпускать эти модемы для Apple компания TSMC будет по передовому 2-нм техпроцессу. Утверждается, что линейка iPhone 17 останется последним поколением смартфонов Apple, использующим 5G-модемы Qualcomm. В семействе iPhone 18 уже будет поголовно применяться модем серии C2, который Apple разработала собственными силами. Первым модемом Apple собственной разработки в 2025 году стал C1, который применялся в составе iPhone 16e. Данный модем сочетал 4-нм и 7-нм чипы. Его преемник по имени C2 должен добавить поддержку полного миллиметрового диапазона и спутниковых сетей. Выпуском модема C2 в массовых количествах TSMC должна будет заняться со следующего года. Если вернуться к теме сотрудничества между Apple и Intel, то наиболее вероятным его вариантом на первых порах станет выпуск некоторой части процессоров семейства M по технологии Intel 18AP. Такие процессоры, предназначенные для начальных моделей Mac и iPad, появятся к середине 2027 года. Под руководством Лип-Бу Тана компания Intel так и не избавилась от основных проблем

10.05.2026 [01:31],

Алексей Разин

Впечатляющая динамика курса акций Intel в этом году может создать впечатление, что инвесторы поверили в её ближайшие перспективы, и заслугу эту можно присудить генеральному директору Лип-Бу Тану (Lip-Bu Tan, на фото слева). Изнутри ситуация выглядит далеко не так благополучно, как утверждают опрошенные Bloomberg источники.  Напомним, Лип-Бу Тан заступил в должность генерального директора в марте прошлого года. Внешний фон с тех пор начала благоприятствовать росту курса акций Intel. Во-первых, Лип-Бу Тану удалось завоевать личное расположение президента Дональда Трампа (Donald Trump), хотя сперва тот упрекал Тана в обилии деловых связей с китайскими компаниями. Правда, ценой такой благосклонности стал переход под контроль американского правительства почти 10 % акций Intel, но переданы они были на условиях, которые пусть и с оговорками, но можно назвать рыночными. Благотворно на акции Intel влияет и интерес крупных американских компаний к производственным возможностям этого процессорного гиганта. Tesla и SpaceX устами своего руководителя Илона Маска (Elon Musk) наличие такого интереса уже раскрыли, а потенциальное сотрудничество с Apple пока обсуждается довольно авторитетными СМИ лишь в качестве слухов. Впрочем, в последнее время оптимизм инвесторам больше внушает высокий спрос на серверные процессоры, которые Intel выпускает под собственной маркой. Они на данном этапе бума ИИ стали востребованы, спрос заметно превышает предложение, выручка и прибыль компании в серверном сегменте растут уверенными темпами. Bloomberg признаётся, что внутри Intel не все довольны проделанной Таном работой. С момента своего перехода на пост генерального директора он больше времени провёл за пределами офиса и предприятий, а до подчинённых не был доведён подробный план по решению проблем компании. Ей приходится по-прежнему иметь дело с трудностями: Intel не располагает продуктами, которые позволят ей вернуть утраченные рыночные позиции, а конкуренты пока не спешат доверить Intel производство своих чипов. В одном из своих первых интервью в статусе генерального директора Тан признался, что перед Intel лежит долгий путь к лидирующим рыночным позициям. Считается, что до конца июня Лип-Бу Тан должен завершить комплектование команды управленцев, которые будут понимать всю важность проводимых им реформ. Тану удаётся лоббировать интересы Intel благодаря своим обширным деловым связям. Сообщается, что даже в ситуации с претензиями Дональда Трампа он заручился поддержкой влиятельных представителей отрасли, чтобы расположить американского президента к себе. В их числе упоминался, например, Майкл Делл (Michael Dell), основавший одного из крупнейших производителей ПК в мире. Симпатии Илона Маска нынешний глава Intel тоже завоевал не сразу, причём готовность первого использовать техпроцесс Intel 14A для выпуска разработанных Tesla чипов стала неожиданностью даже для многих соратников Тана.  Конъюнктура рынка компонентов для инфраструктуры ИИ сейчас разворачивается в благоприятное для Intel русло, но это не отменяет отсутствия у компании достойных специализированных ускорителей типа GPU. С техпроцессами у Intel тоже не всё так хорошо, как в былые годы, заметную часть кристаллов для собственной продукции она получает от тайваньской TSMC. Кроме того, в серверном и клиентском сегментах Intel утратила часть своих рыночных позиций. Капитальные затраты на освоение новых технологий настолько выросли, что Intel даже при безусловном успехе собственной продукции не сможет их оправдать без привлечения на свои производственные мощности сторонних клиентов. Тан пытается выстроить работу с потенциальными заказчиками, внушая им мысль, что Intel будет обслуживать их едва ли не лучше, чем саму себя. Источники отмечают, что при общении с сотрудниками нынешний глава Intel не доносит лично подробных планов по развитию компании на ближайшие годы, а пытается поручить эту миссию другим руководителям. Нанимая требуемые кадры, Тан больше полагается на беседы с кандидатами о состоянии дел в отрасли, используя свой многолетний опыт работы в венчурном бизнесе. Стратегии и конкретные планы таких кандидатов Тан при этом не изучает. Проблемой для Intel остаётся высокий уровень затрат на выпуск чипов — они получаются почти в три раза выше, чем у конкурирующей TSMC, если верить экспертам. При этом Intel много денег теряет из-за высокого уровня брака. Годная продукция формирует не более 65 % выхода с одной кремниевой пластины, тогда как у TSMC он превышает 80 %. По сути, лишь 8 % разницы в затратах на производство чипов у Intel и TSMC определяются более высокой стоимостью рабочей силы в США. Привлекать новых заказчиков для Intel трудно ещё и потому, что никто из них не желает рисковать и быть первопроходцем. Если бы кто-то сделал это, процесс пошёл бы быстрее. От идеи выделения контрактного производства в обособленную структурную единицу глава Intel не в восторге, поскольку видит в сохранении целостности бизнеса немало преимуществ. Сейчас именно от способности Тана быстро увеличить объёмы выпуска серверных процессоров будет зависеть положение Intel на рынке, поскольку если компания замешкается, то конкуренты смогут её потеснить. Помимо AMD, свои процессоры для серверной инфраструктуры предлагают Nvidia и Arm, не говоря уже о крупных облачных провайдерах. TSMC отправит устаревшее оборудование для выпуска 28-нм чипов с Тайваня в Германию

09.05.2026 [07:57],

Алексей Разин

Тайваньская компания TSMC развивает свои производственные площадки не только в США и Японии, но и Германии. Совместное предприятие ESMC на строящемся заводе Fab 24 к концу следующего года должно начать выпуск компонентов по зрелым техпроцессам. Высвобождаемое в ходе модернизации тайваньских фабрик оборудование как раз будет направлено TSMC в Германию.

Источник изображения: TSMC Об этом сообщает ресурс ComputerBase.de со ссылкой на тайваньское издание Economic Daily. Сейчас TSMC модернизирует на Тайване две части своего предприятия Fab 15, которые имеют разную специализацию. Fab 15A использует так называемую DUV-литографию, выпуская 28-нм и 22-нм чипы, но в обозримом будущем собирается перейти на выпуск 4-нм продукции. Высвобождающееся оборудование для выпуска 22-нм и 28-нм чипов будет направлено в Германию. По соседству Fab 15B выпускает чипы по более современной технологии N7+, но скоро оно перейдёт на выпуск чипов по технологиям N5 и N3. Здесь уже давно применяется EUV-оборудование, поэтому совершить такую миграцию будет реально. В общей сложности, TSMC собирается потратить на модернизацию комплекса Fab 15 около $3,2 млрд. Тайваньская компания сталкивается с растущим спросом на передовую литографию, она обеспечивает около 75 % ей выручки, поэтому от зрелых техпроцессов она будет избавляться. При этом по меркам немецкой промышленности 28-нм и 22-нм технологии вполне востребованы, поскольку с их помощью будут выпускаться чипы для автомобильных электронных систем. Это открывает для TSMC возможность отправить ставшее ненужным на Тайване оборудование для их производства в Германию. Акции Intel подскочили в цене на 14 % после появления информации о сделке с Apple

09.05.2026 [05:03],

Алексей Разин

По итогам публикации квартальной отчётности акции Intel хорошо подросли в цене, апрель в целом стал для компании лучшим месяцем за 55 лет присутствия на бирже. Вчера вечером появился новый информационный повод, который позволил акциям Intel в течение одной сессии подорожать на 14 % — речь идёт о предполагаемой сделке с Apple.

Источник изображения: Intel По её условиям, которые представители обеих компаний пока комментировать не готовы, Intel якобы будет производить для Apple определённые процессоры, используемые в неких устройствах этой марки. Переговоры на эту тему, якобы, велись на протяжении более года. Заметим, что указанный период характеризовался укреплением Nvidia в статусе крупнейшего клиента TSMC, тогда как ранее именно Apple была крупнейшим заказчиком тайваньского производителя чипов и могла рассчитывать на определённые привилегии. По всей видимости, именно смена приоритетов TSMC создала условия для сотрудничества Apple и Intel в сфере производства чипов. Акции Apple также подросли на 2 % после публикации соответствующих новостей. В интервью CNBC аналитики Creative Strategies выразили уверенность в неизбежности сотрудничества Apple и Intel, они лишь не могли предугадать конкретное время. Акции Intel с начала года подорожали на 200 %, и тезис о необходимости найти якорных клиентов на выпуск сторонних процессоров в этой сфере обыгрывался неоднократно. По мнению экспертов, для Apple контрактные мощности Intel являются единственной альтернативой сотрудничеству с TSMC, поскольку они могут масштабироваться в достойных диапазонах. Скорее всего, как рассуждают представители Creative Strategies, компания Apple дождётся перехода Intel на технологию 18A-P в следующем году для размещения заказов на выпуск своих процессоров, поскольку с предшествующим 18A у этой компании возникает ряд трудностей. Как известно, Илон Маск (Elon Musk) также обратил внимание на способность Intel выпускать чипы по контракту, но сотрудничество с его компаниями SpaceX и Tesla вряд ли проявится на практике ранее 2029 года, когда будет освоен техпроцесс 14A в адекватных объёмах. TSMC от сделки Apple с Intel не особо пострадает, поскольку всё равно работает на пределе возможностей. Intel снова будет производить чипы для Apple, но не как раньше — WSJ узнала о предварительном соглашении

08.05.2026 [23:13],

Николай Хижняк

Apple и Intel достигли предварительного соглашения, согласно которому Intel будет производить некоторые процессоры Apple на своих полупроводниковых фабриках Intel Foundry. Информацией поделилась газета The Wall Street Journal, ссылающаяся на источники, близкие к вопросу.

Источник изображения: VideoCardz Согласно отчёту, две компании вели переговоры более года. Формальная сделка была достигнута в последние месяцы, хотя ни Apple, ни Intel пока публично её не подтверждали. «По словам источников, знакомых с ситуацией, Apple и Intel достигли предварительного соглашения о том, что Intel будет производить некоторые чипы для устройств Apple», — The Wall Street Journal. В отчёте не уточняется, в каких продуктах Apple будут использоваться чипы производства Intel. Это также не означает, что Apple возвращается к процессорам Intel для компьютеров Mac. В сообщении говорится, что Intel будет производить чипы для устройств Apple, а не поставлять собственные процессоры x86. Начиная с моделей, представленных в конце 2020 года, Apple отказалась от процессоров Intel в своих компьютерах Mac. Теперь компания использует процессоры M-серии собственной разработки во всей линейке продуктов Mac. Ранее сообщалось, что Apple вела предварительные переговоры с Intel и Samsung о производстве процессоров для своих устройств в США. Тогда говорилось, что эти переговоры находятся на ранней стадии и никаких договорённостей достигнуто не было. |