На днях на конференции IEDM 2024 в Сан-Франциско компания TSMC впервые официально рассказала о преимуществах перехода на 2-нм транзисторы с круговым затвором Gate-All-Around и нанолистовыми каналами. К выпуску чипов по технологии N2 тайваньский чипмейкер приступит в наступающем году. По сути, нанолисты — это финальная архитектура транзисторов в привычном понимании и она останется актуальной надолго.

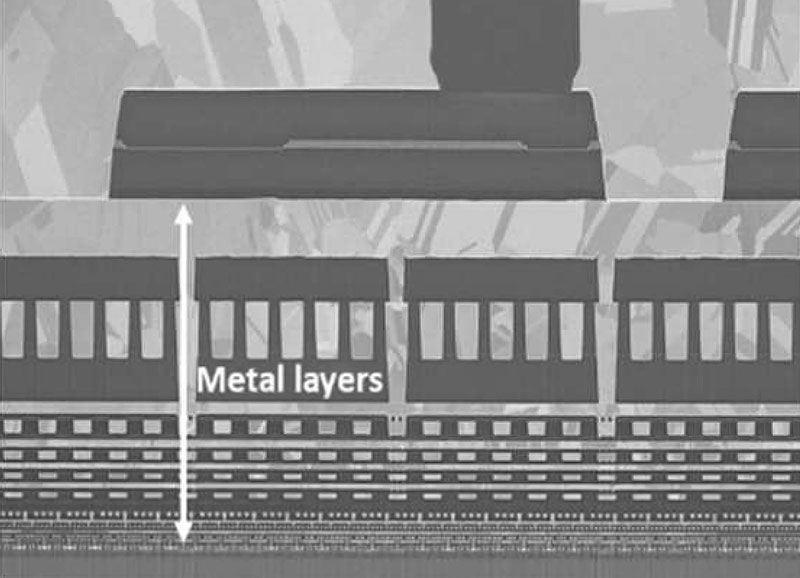

Не видите внизу 2-нм транзисторы? А они есть! Источник изображения: TSMC

В 2025 году производить чипы на основе 2-нм техпроцесса с наностраничными каналами и круговым затвором начнут также Samsung и Intel. Подобные структуры первой начала выпускать компания Samsung в рамках 3-нм техпроцесса в 2022 году. Для TSMC это станет первым опытом и плодом «более чем четырёхлетнего труда», как признался глава отдела разработчиков компании.

Современные транзисторы FinFET представляют собой набор вертикально расположенных транзисторных каналов — рёбер или плавников. Характеристики такого транзистора зависят от количества рёбер у каждого — одного, двух или трёх. Чем больше каналов, тем больше площадь, занимаемая транзистором. Это особенно остро сказывается в случае массивов памяти SRAM. Каждая ячейка такой памяти состоит из шести транзисторов и поэтому плохо поддаётся масштабированию. Между тем, без SRAM не обходятся ни простенькие контроллеры, ни мощные процессоры и ускорители.

Перевод транзисторных каналов в горизонтальную плоскость в виде тонких наностраниц сразу улучшает плотность, так как каналы располагаются друг над другом, и неважно, сколько их. От этого занимаемое транзистором место не увеличивается. В частности, переход TSMC от выпуска 3-нм FinFET транзисторов к 2-нм наностраничным увеличивает плотность размещения транзисторов на 15 %, независимо от того, используются ли производительные схемы или энергоэффективные. Выигрыш произойдёт в обоих случаях.

Между производительностью и энергоэффективностью придётся выбирать. Если делать ставку на скорость вычислений, прирост от перехода на 2-нм наностраничные транзисторы составит 15 %, а если выбрать низкое потребление, то выигрыш достигнет впечатляющих 30 %. Но это не вся польза от наностраничных каналов. Для FinFET транзисторов нельзя создать транзисторы с 1,5 рёбрами — это как полтора землекопа из известной сказки. Зато в случае наностраничных каналов можно менять их ширину, не говоря о количестве, и проектировать схемы с разнообразными и точно требуемыми параметрами.

В компании TSMC технологию изменения ширины наностраниц назвали Nanoflex. Это позволит выпускать на одном кристалле логику с узкими наностраницами, что ограничит их потребление, и вычислительное ядро с транзисторами с широкими наностраницами для пропускания больших токов, что обеспечит производительность, несмотря ни на что.

Но особенно заметно от перехода на наностраничные транзисторные каналы выиграет SRAM. При переходе с 4-нм на 3-нм техпроцесс плотность ячеек памяти SRAM выросла всего на 6 %. В случае технологии Nanoflex при переходе от 3-нм на 2-нм техпроцесс плотность ячеек SRAM вырастет на 11 %. Это даст повсеместный выигрыш, утверждают в TSMC.

Источник изображения: Intel

Интересно добавить, что на этой же конференции прозвучал доклад компании Intel, которая очертила границы будущего для классических транзисторов и, конкретно, в наностраничном исполнении.

«Архитектура наностраниц на самом деле является последним рубежом транзисторной архитектуры, — сказал Ашиш Агравал (Ashish Agrawal), специалист по кремниевым технологиям в исследовательской группе Intel по компонентам схем. — Даже будущие комплементарные FET (CFET) устройства, которые, возможно, появятся в середине 2030-х годов, будут построены из нанолистов. Поэтому важно, чтобы исследователи понимали свои ограничения».

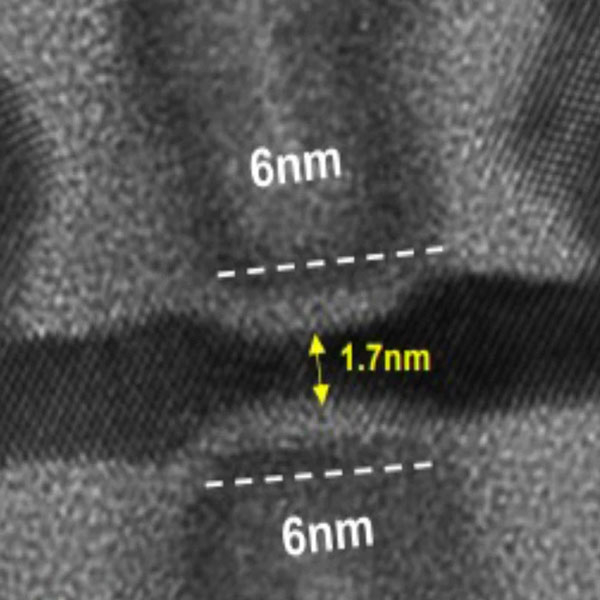

Чтобы изучить границы возможного, в Intel создали экспериментальную транзисторную структуру с каналом длиной 6 нм. Чем короче канал, тем выше вероятность утечек через него и тем менее управляемым становится транзистор. Эксперимент показал, что транзисторы с каналами длиной 6 нм и шириной наностраницы 2 нм полностью работоспособны. Это позволит наностраничной транзисторной архитектуре существовать ещё долго, отодвинув переход на двумерные материалы и транзисторы на принципиально иной архитектуре далеко в будущее.

Возвращаясь к 2-нм техпроцессу TSMC (а также Samsung и Intel), напомним, что цифра в его названии ничего не говорит о физических размерах транзисторов. В рамках 2-нм техпроцесса транзисторы и транзисторные каналы измеряются десятками нанометров. Поэтому до выставленных Intel границ в эксперименте индустрия будет идти не одну пятилетку.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018