|

Опрос

|

реклама

Быстрый переход

Samsung ускоряет строительство фабрик в США и ищет заказчиков на 2-нм чипы

30.04.2026 [14:01],

Алексей Разин

Южнокорейская компания Samsung Electronics не отказывается от амбиций в сфере контрактного производства, несмотря на всю неоднозначность своего «послужного списка» в данной сфере. Она не только начала согласовывать строительство второго контрактного предприятия в США, но и надеется вскоре обзавестись новыми клиентами, которые будут заказывать у неё передовые 2-нм чипы.

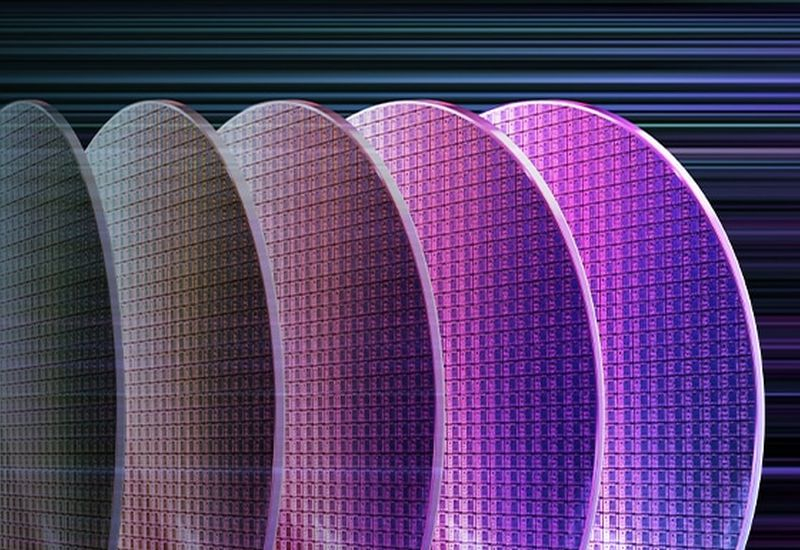

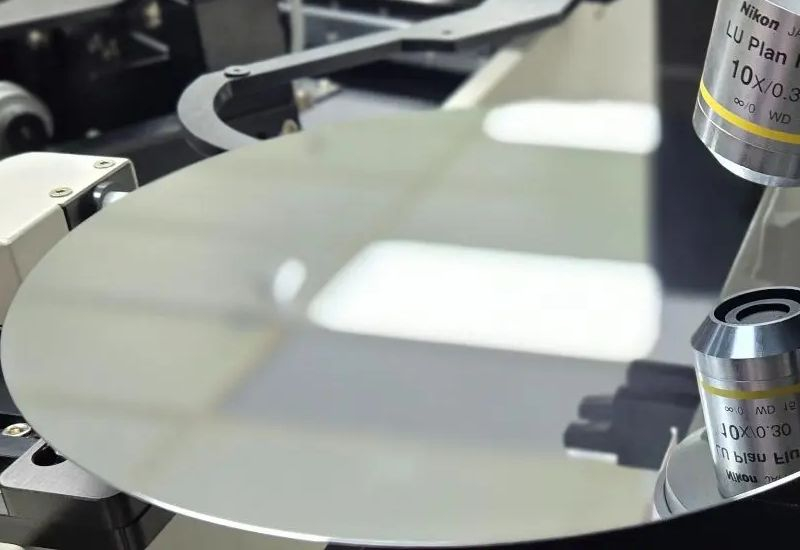

Источник изображения: Samsung Electronics Как отмечает Reuters со ссылкой на комментарии представителей Samsung Electronics, массовое производство чипов на первом из предприятий в техасском Тейлоре начнётся в 2027 году, а свою работу оно номинально начнёт уже в этом году. В прошлом году Samsung удалось заключить многолетний контракт с Tesla на производство чипов, разработанных этой компанией. Именно этот контракт дал серьёзный толчок к дальнейшему развитию новой площадки Samsung в Техасе, поскольку на протяжении нескольких лет проект был почти заморожен из-за неопределённости с субсидиями и заказами на продукцию. В январе с подачи южнокорейских СМИ стало известно, что Samsung ведёт переговоры с Qualcomm и прочими клиентами о возможности производства 2-нм чипов для них. На этой неделе Samsung не стала конкретизировать, с какими «крупными представителями технологической отрасли» она ведёт переговоры, но подчеркнула, что в скором времени она получит новых заказчиков на свой 2-нм техпроцесс в контрактной сфере. Qualcomm не уверена в способности Samsung выпускать для неё 2-нм чипы с нужным качеством

11.04.2026 [06:08],

Алексей Разин

Американская Qualcomm отличается определённой «всеядностью» с точки выбора подрядчиков для выпуска процессоров собственной разработки, поэтому в этом качестве в разное время выступали не только TSMC и Samsung, но и китайская SMIC. По данным корейских СМИ, возможность сотрудничества Qualcomm с Samsung в сфере выпуска 2-нм процессоров оказалась под вопросом из-за проблем с качеством продукции.

Источник изображения: Samsung Electronics По информации Business Korea, в тактике Qualcomm на производственном направлении наметился очевидный перевес в сторону TSMC, поскольку Samsung Electronics не может обеспечить заданные параметры качества выпускаемой продукции. Следующее поколение процессоров Qualcomm, как ожидается, будет производиться преимущественно TSMC. Не исключено даже, что последняя окажется единственным подрядчиком Qualcomm. Возможность выпуска 2-нм процессоров Qualcomm компанией Samsung обсуждалась с начала этого года. На сотрудничество с южнокорейским подрядчиком возлагались большие надежды, об этом даже публично обмолвилось руководство Qualcomm. В этой сфере компании не сотрудничали с 2022 года, но до 2021 года включительно Samsung принимала участие в выпуске чипов Qualcomm с использованием передовых на тот момент литографических технологий. Причиной нового охлаждения интереса Qualcomm к услугам Samsung по контрактному производству чипов стал низкий уровень выхода годной продукции при использовании 2-нм техпроцесса. По слухам, в прошлом полугодии лишь 20 % чипов, выпускаемых Samsung по 2-нм технологии, были годными для дальнейшего использования. Принято считать, что для массового производства чипов показатель должен превышать 60 %, но в случае с Samsung он сейчас хоть и близок к этому уровню, но не может похвастать стабильностью. При этом TSMC достигла уровня выхода годной 2-нм продукции в диапазоне от 60 до 70 % на стабильной основе. Qualcomm требует от подрядчиков, чтобы уровень выхода годной продукции был не ниже 70 %, поскольку более низкие значения отрицательно сказываются на прибыльности производства. TSMC уже смогла привлечь к своему 2-нм техпроцессу не только Qualcomm, но и AMD, Apple и Nvidia, как отмечают источники. Для Samsung в этом отношении не всё потеряно, по словам экспертов, поскольку если уровень выхода годной продукции в рамках её 2-нм техпроцесса достигнет приемлемых для Qualcomm величин, компании смогут возобновить сотрудничество. В конце концов, Qualcomm всегда старается полагаться на максимальное количество подрядчиков с целью снижения рисков, связанных с перебоями в поставках продукции. Samsung в дальнейшем также предстоит доказать свою технологическую состоятельность и в рамках освоения 1-нм технологий. Samsung догоняет TSMC: выход годных 2-нм чипов подскочил втрое и превысил 60 %

24.03.2026 [18:24],

Сергей Сурабекянц

Сегодня стало известно, что Samsung Electronics повысила выход годных изделий по своему 2-нанометровому техпроцессу контрактного производства полупроводников до более чем 60 %. Ещё во второй половине прошлого года выход годных изделий не превышал 20 %. Такое существенное повышение позволит компании резко снизить производственные затраты и открывает больше возможностей для новых заказов. Источник изображения: Samsung Подразделение Samsung Electronics Foundry изготавливает чипы по 2-нм техпроцессу по заказам от подразделения Samsung Electronics System LSI Division и китайских компаний Canaan и MicroBT, которые производят оборудования для майнинга криптовалют. Сообщается, что в течение последних двух кварталов выход годных изделий для Canaan и MicroBT увеличился более чем в три раза и превысил 60 %. Средний выход годных чипов Exynos 2600 для System LSI пока остаётся ниже 50 %, но ситуация также улучшается с каждым днём. Для сравнения — ведущий мировой производитель микросхем компания TSMC в настоящее время добилась для своего 2-нм техпроцесса выхода годных изделий на уровне 60–70 %. Дальнейшее повышение выхода годных изделий для современных техпроцессов затруднено из-за их высокой сложности. Увеличение выхода годной продукции также открывает возможности для привлечения большего числа клиентов. «В последнее время наблюдается тенденция к применению передовых чипов размером менее 5 нм в информационных технологиях, — отметил представитель отрасли. — Если станет известно, что выход годной продукции в 2-нм техпроцессе Samsung Electronics улучшился, весьма вероятно, что другие клиенты заинтересуются». В прошлом году Samsung Electronics заключила контракт на производство 2-нанометрового чипа автономного вождения AI6 для крупнейшего мирового автопроизводителя Tesla. Этот контракт оценивается в $16,5 млрд. Samsung задержит запуск техасского завода полупроводников до 2027 года, а пострадает Tesla

03.03.2026 [15:09],

Алексей Разин

Судьба нового предприятия Samsung Electronics в техасском Тейлоре начала определяться ещё при президенте Джозефе Байдене (Joseph Biden), поскольку подписанный им «Закон о чипах» был призван стимулировать южнокорейского гиганта организовать в США производство более передовых чипов, чем выпускаются в окрестностях Остина. Всё идёт к тому, что новое предприятие Samsung в Техасе, которое должно было заработать в начале этого года, не сможет начать полномасштабный выпуск продукции ранее начала следующего года.

Источник изображения: Samsung Electronics Об этом сообщает южнокорейское издание JoongAng Daily, отмечая, что опытное производство чипов на новом предприятии Samsung в Тейлоре уже запущено. При этом данный факт вовсе не гарантирует, что массовый выпуск чипов здесь будет развёрнут ранее начала 2027 года. Точного графика экспансии производства на данной площадке пока нет, и он появится ближе к июню текущего года. Samsung официально пока заявляет, что подготовка к запуску массового производства будет завершена к концу текущего года. К тому времени предприятие в Тейлоре будет считаться полностью работоспособным. С момента начала строительства этой фабрике в Техасе Samsung успела поднять планку, не очень давно предложив освоить там выпуск 2-нм чипов вместо изначальных 4-нм. Считается, что подготовка к освоению производства 2-нм чипов ведётся компанией параллельно как в США, так и в Южной Корее. В целом, Samsung рассчитывает перейти к выпуску чипов по 2-нм техпроцессу второго поколения (SF2P) в этом году. В какие сроки он будет освоен в Техасе, пока судить сложно. Тем более, что в Южной Корее часть мощностей в Пхёнтхэке была переоборудована под выпуск памяти, которая в условиях ИИ-бума весьма востребована рынком. По итогам текущего года Samsung Electronics хотела бы вывести свой бизнес по контрактному производству чипов на безубыточность. С этой точки зрения сроки освоения 2-нм технологии важны для компании, которая уже долгое время страдает от недостаточной эффективности бизнес-процессов в данной сфере. В 2027 году Samsung рассчитывает занять не менее 20 % мирового рынка услуг по контрактному выпуску чипов. От сроков запуска предприятия в Тейлоре будут зависеть и взаимоотношения Samsung с крупными клиентами, среди которых недавно появилась Tesla, заключившая с корейским подрядчиком долгосрочный контракт на выпуск чипов AI5 и AI6 для собственных роботов, систем автопилота и инфраструктуры искусственного интеллекта. По крайней мере, 2-нм техпроцесс будет использоваться при выпуске чипов AI6, которые выйдут позже своих предшественников — ориентировочно, в середине 2028 года. В отличие от Тайваня, законодательство Южной Кореи не вынуждает местных производителей ограничивать себя в экспорте передовых литографических технологий. Формально, это создаёт условия для Samsung, позволяющие опередить TSMC по срокам освоения выпуска 2-нм чипов на территории США. Canon хочет использовать 2-нм техпроцесс от Rapidus для датчиков изображений, но непонятно, зачем

03.03.2026 [13:30],

Алексей Разин

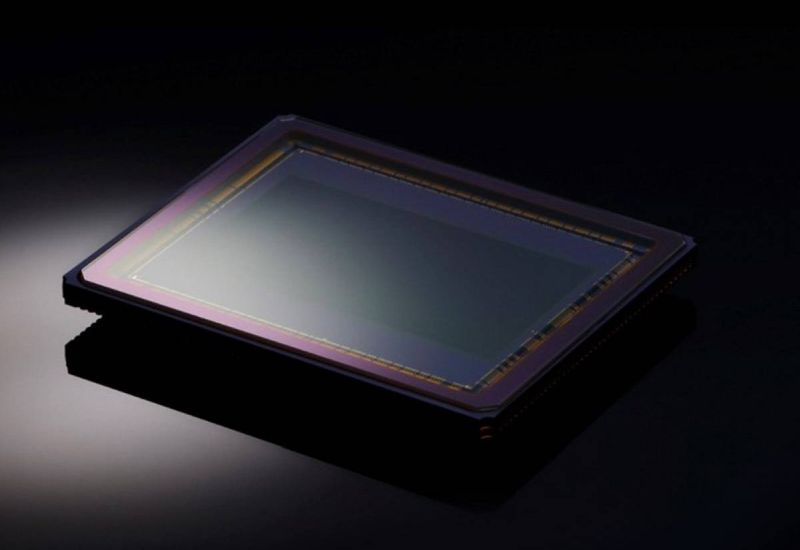

Исторически датчики изображений, применяемые в цифровых камерах, не требовали передовой литографии для своего изготовления, Sony была готова довольствоваться 28-нм техпроцессом, участвуя в финансировании строительства первого предприятия TSMC в Японии. Теперь выясняется, что в числе первых клиентов конкурирующей Rapidus окажется Canon, которая будет получать от неё 2-нм чипы локального производства.

Источник изображения: Canon По крайней мере, издание Nikkei Asian Review утверждает, что Canon закажет Rapidus выпуск прототипов датчиков изображений с использованием передового 2-нм техпроцесса. Данное сотрудничество будет носить символический характер, ведь молодая японская компания сможет наладить выпуск передовых чипов для другой японской компании. Разработку данных компонентов Canon будет вести при поддержке компании Synopsys. Ожидается, что данный проект потребует расходов в размере $255 млн, две трети этой суммы в форме субсидий предоставит японское правительство. По замыслу Canon, переход на 2-нм техпроцесс позволит повысить скорость и качество обработки изображений, а также снизить энергопотребление. Canon приняла участие в недавнем раунде финансирования Rapidus вместе с 31 другой компанией частного сектора, который позволил молодому японскому производителю чипов привлечь $1,7 млрд, включая правительственные средства. Вероятно, 2-нм технология могла заинтересовать Canon для производства логической части датчиков изображений, поскольку фотодиодам нужен явно больший объем кремния для захвата света. Слишком сильное уменьшение транзисторов внутри пикселя приводит к росту шумов и утечек тока, поэтому большинство современных матриц производится по зрелым техпроцессам. Как подчёркивают японские источники, помимо Canon, компания Rapidus пока не может похвастать большим количеством потенциальных клиентов. Изначально Rapidus выстраивала свою бизнес-модель таким образом, чтобы обслуживать небольшие заказы, но с использованием передовых литографических технологий. Большинству японских клиентов 2-нм техпроцесс пока попросту не интересен, и даже в случае с Canon его использование более походит на политическую акцию, а не результат трезвого экономического расчёта. Приступить к массовому производству 2-нм чипов Rapidus рассчитывает с весны следующего года, но для окупаемости гигантских инвестиций в капитал компании её производственные линии должны быть стабильно загружены. Через своё американское представительство Rapidus попытается привлечь зарубежных заказчиков, она уже сотрудничает с американским стартапом Tenstorrent в сфере разработки чипов для ИИ-ускорителей. Японский стартап Preferred Networks изучает возможность сотрудничества с Rapidus, а Fujitsu хотела бы в идеале наладить в Японии выпуск 1,4-нм процессоров. Начать их производство Rapidus сможет не ранее 2029 года. До начала следующего десятилетия компания потребует на своё развитие почти $45 млрд, чуть менее половины этой суммы должно будет предоставить японское правительство. Заказы на выпуск 2-нм чипов у компании TSMC распределены на ближайшие пару лет

01.03.2026 [07:15],

Алексей Разин

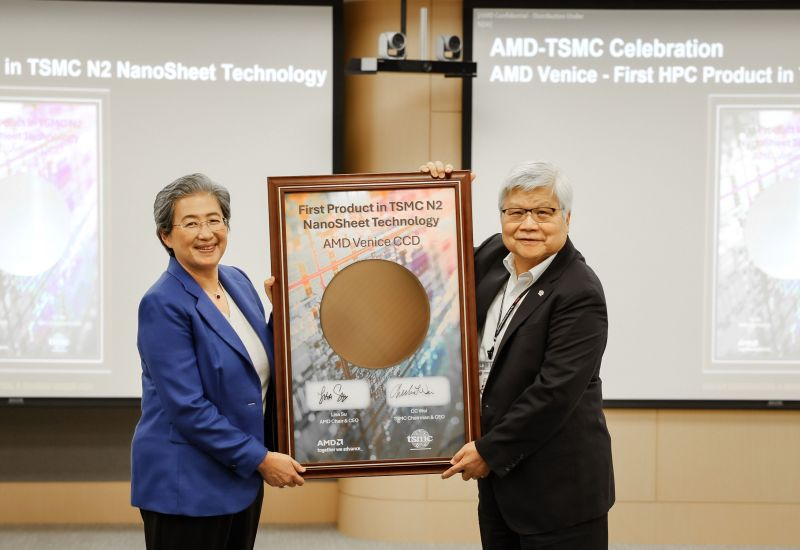

В сфере освоения передовых литографических процессов тайваньская TSMC оторвалась от конкурентов, хотя Samsung и Intel пытаются делать вид, что этого не произошло. Так или иначе, сейчас клиентов TSMC просят делать заказы на поставку 2-нм продукции со сроком исполнения не ранее второго квартала 2027 года. В целом, квоты на выпуск 2-нм чипов у TSMC уже распроданы на ближайшие два года.

Источник изображения: AMD Об этом сообщает ресурс Culpium, основанный колумнистом Тимом Калпаном (Tim Culpan), который 25 лет живёт на Тайване и имеет богатый опыт работы в Bloomberg. По его словам, заказы на поставку 2-нм чипов всё ещё можно сделать, но сроки их исполнения уже измеряются шестью кварталами. В такой ситуации разработчикам чипов сложно попасть в собственные графики выпуска новой продукции, если они зависят в данной сфере от TSMC. Прочие источники ранее уже отмечали, что и заказы на выпуск продукции по техпроцессу N3 у TSMC распределены глубоко в 2027 год. Выпуск серийной продукции по N3 компания начала в 2022 году, в прошлом она увеличила выручку от её реализации до $25 млрд. Более современная технология N2 используется в массовом производстве чипов не более шести месяцев. Сообщается, что Apple является первым клиентом TSMC, который воспользуется технологией N2, и соответствующие 2-нм процессоры найдут применение в семействе ноутбуков MacBook. По итогам прошлого года Nvidia удавалось превзойти Apple по доле выручки, обеспечиваемой TSMC. Первая из компаний практически удвоила выплаты TSMC за поставку своей продукции до $23,3 млрд, тогда как Apple довольствовалась $20,7 млрд. Со второй половины 2026 года начнётся выпуск продукции по технологии N2P, которая обеспечит прирост быстродействия на 5 % при прежнем уровне энергопотребления. Более передовой техпроцесс A16 будут применяться для выпуска высокопроизводительных чипов. TSMC обычно заранее планирует потребность в производственных мощностях, и требует с клиентов авансовые платежи, которые отчасти покрывают капитальные затраты на их строительство. Заказчикам необходимо не позднее чем за 12 месяцев до начала поставок готовой продукции определиться со своими потребностями. В исключительных случаях TSMC принимает и более срочные заказы, но обычно берёт за них повышенную оплату. Руководство Nvidia на этой неделе отметило, что располагает заказами на продукцию на значительную часть 2027 года. Клиенты, по словам представителей Nvidia, делятся с компанией своими многолетними планами, поскольку нужно резервировать будущие поставки уже сейчас. Выпуск продукции по технологии N3 компания TSMC собирается освоить и в Японии, а с конвейера будущего предприятия в Аризоне начнут сходить чипы, изготовленные по технологиям N2 и A16. В погоне за TSMC: Samsung собралась запустить производство 1,4-нм чипов к 2029 году

29.01.2026 [13:05],

Алексей Разин

Номинально Samsung Electronics несколько лет назад опередила TSMC по срокам освоения массового производства 3-нм чипов на полгода, но в большой поток заказов это преимущество так и не вылилось. С тех пор южнокорейский производитель всё время пытается устранить отставание от TSMC на деле, и к серийному производству 2-нм чипов собирается приступить во втором полугодии.

Источник изображения: Samsung Electronics Как известно, Samsung удалось привлечь Tesla в качестве заказчика, для которого она будет изготавливать 2-нм и более прогрессивные чипы. По информации ZDNet, на квартальной отчётной конференции на этой неделе представители Samsung Electronics пояснили, что в этом году количество заказов на выпуск 2-нм чипов должно вырасти более чем на 30 %. Помимо Tesla, переговоры в этой сфере ведутся с крупными компаниями из США и Китая. По быстродействию 2-нм чипов и уровню выхода годной продукции Samsung уже опережает намеченный график, как отмечают источники. Во второй половине текущего года Samsung начнёт серийный выпуск 2-нм чипов для своих клиентов. Контрактное подразделение Samsung ожидает увеличения выручки на двузначное количество процентов и улучшение показателей прибыльности в этом году, делая упор на продвижение передовых техпроцессов на рынок. Освоение 1,4-нм техпроцесса идёт по плану, в массовом производстве чипов он начнёт использоваться в 2029 году. Инструментарий для разработки соответствующих компонентов будет передан клиентам Samsung во второй половине следующего года. Южнокорейский гигант в борьбе за клиентов на контрактном направлении готов использовать и свои естественные преимущества в виде компетенций в сфере производства памяти, упаковки чипов и создания собственных логических микросхем. С учётом высокой степени интеграции современных вычислительных компонентов, такое преимущество явно не следует списывать со счетов. TSMC приступила к массовому производству 2-нм чипов без лишнего шума

30.12.2025 [04:54],

Алексей Разин

Четвёртый квартал уходящего года давно значился в планах TSMC в качестве периода запуска массового производства 2-нм изделий, и если ориентироваться на опубликованную на официальном сайте компании информацию, старт выпуска состоялся на предприятии Fab 22 на юге Тайваня в Гаосюне.

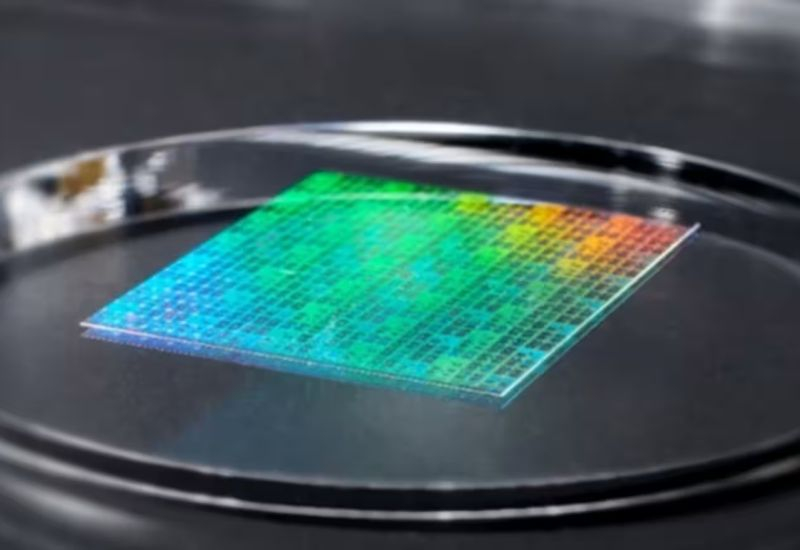

Источник изображения: TSMC Об этом сообщает ресурс Tom’s Hardware, анализирующий всю имеющуюся на данный момент информацию на эту тему. В первом поколении техпроцесс N2 в исполнении TSMC должен обеспечить прирост быстродействия в 10–15 % при неизменном энергопотреблении, либо снижение последнего на 25–30 % при неизменном уровне быстродействия транзисторов. Плотность размещения транзисторов по сравнению с техпроцессом N3E удастся увеличить на 15 % для чипов смешанного дизайна, только для логических компонентов она возрастёт на величину до 20 %. Впервые TSMC будет использовать структуру транзисторов с окружающим затвором (GAA) именно в рамках 2-нм техпроцесса и его последующих вариаций. Новая геометрия улучшает контроль за электростатическими параметрами, снижает токи утечки и обеспечивает уменьшение размеров транзисторов без ухудшения быстродействия или энергетической эффективности. Кроме того, в рамках техпроцесса N2 будут использоваться конденсаторы типа SHPMIM в подсистеме питания чипов. По сравнению с прошлыми SHDMIM, они увеличивают ёмкостную плотность более чем в два раза и снижают сопротивление, что обеспечивает более стабильное питание и повышает общую энергетическую эффективность. В октябре глава TSMC Си-Си Вэй (C.C. Wei) сообщил, что техпроцесс N2 будет внедрён в условиях массового производства до конца четвёртого квартала с хорошим уровнем выхода годной продукции. В 2026 году объёмы производства будут наращиваться, причём как благодаря чипам для смартфонов, так и высокопроизводительным решениям для искусственного интеллекта. Выпуск чипов по технологии N2 компания начала на Fab 22 — предприятии на юге Тайваня, хотя исследовательский центр по её освоению находится в Синьчжу в другой части острова. Расположенная по соседству Fab 20 освоит выпуск 2-нм продукции позднее, по всей видимости. Готовность TSMC изначально применять техпроцесс N2 для выпуска крупных и сложных чипов говорит о высоком спросе на 2-нм продукцию со стороны сегмента ИИ, а также уверенности компании в своих силах. Традиционно новый техпроцесс внедрялся сначала при производстве относительно компактных мобильных и потребительских чипов. К концу 2026 года оба указанных выше предприятия начнут выпускать чипы по технологии N2P, которая обеспечит прирост производительности, а также по технологии A16, которая добавит подвод питания с оборотной стороны кремниевой пластины (Super Power Rail). Последнее новшество позволит создавать более эффективные и сложные по своей компоновки чипы для сегмента высокоскоростных вычислений. Массовое производство таких компонентов должно начаться во второй половине 2026 года. Ставки растут: TSMC задумалась о выпуске 2-нм чипов в Японии — ещё недавно речь шла только о 6 нм

22.12.2025 [09:51],

Алексей Разин

Не так давно одно авторитетное японское издание заявило, что второе по счёту предприятие TSMC в Японии будет построено с расчётом на выпуск не 6-нм продукции, как планировалось изначально, а более передовой 4-нм. Теперь новые источники сообщают, что и этот план не является окончательным, и TSMC готова наладить здесь выпуск 2-нм изделий.

Источник изображения: TSMC По данным Mirror Media, соответствующий план уже передан на согласование генеральному директору и председателю совета директоров TSMC Си-Си Вэю (C.C. Wei). Напомним, деятельность в Японии тайваньский контрактный производитель чипов осуществляет через совместное предприятие с Sony и Denso, именуемое JASM. В случае такой переориентации второго предприятия JASM в регионе оно будет главным образом снабжать не производителей автокомпонентов типа той же Denso, а разработчиков чипов для ускорителей ИИ, типа Nvidia и AMD. В первом полугодии JASM получила $197 млн убытков, тогда как американское предприятие TSMC принесло $149 млн прибыли, наладив выпуск 4-нм чипов для местных клиентов. Такая диспропорция заставила руководство TSMC задуматься о необходимости организации в Японии производства более продвинутых компонентов. Сейчас спрос на 28-нм чипы, выпускаемые на первом японском предприятии JASM, довольно низок, и даже на Тайване линии по выпуску 6-нм чипов в октябре этого года были загружены только на 70 % от силы. Ещё одна площадка по производству 6-нм чипов только усугубит убытки японского СП. В конце ноября, по данным Mirror Media, компания TSMC приняла решение развивать в Японии производство передовых чипов. Церемония закладки фундамента второго предприятия в префектуре Кумамото состоялась в конце октября этого года. Если бы оно к 2027 году наладило выпуск 4-нм продукции, то всё равно бы отстало от конъюнктуры рынка, поэтому теперь руководство считает разумным изначально нацеливаться на выпуск 2-нм изделий. Проблема заключается в том, что переход на подготовку к выпуску 2-нм чипов в Японии заметно увеличит бюджет проекта. Капитальные затраты увеличатся с $10 до $25 млрд, но не это может стать главным препятствием. Тайваньские власти хотят ограничить экспорт передовых технологий за пределы острова. Сейчас они допускают организацию выпуска за пределами Тайваня чипов, использующих технологии, отстающие от передовых на два поколения. Обсуждаемый выше 2-нм техпроцесс является самым прогрессивным по меркам Тайваня. Кроме того, увеличение капитальных затрат потребует более щедрых субсидий со стороны японских властей, а они сейчас сосредоточены на поддержке конкурирующей компании Rapidus. Представители TSMC отказались комментировать публикацию Mirror Media. 2 нм нарасхват: самые передовые линии TSMC забиты заказами до конца 2026 года

17.12.2025 [12:53],

Алексей Разин

Уходящий год для тайваньской компании TSMC характеризовался переходом к массовому производству чипов по технологическим нормам 2 нм, которые считаются передовыми по меркам мировой отрасли. Тайваньские источники утверждает, что заказами на выпуск 2-нм продукции эта компания загружена до самого конца 2026 года.

Источник изображения: TSMC Впервые в своей истории TSMC должна внедрить структуру транзисторов с окружающим затвором (GAA) именно в рамках 2-нм технологии. Именно прогресс в материаловедении, по словам тайваньских СМИ, во многом определяет сроки и масштабы внедрения новых литографических норм в масштабах полупроводниковой отрасли. TSMC в этом квартале начинает массовые поставки 2-нм чипов своим клиентам, и от перехода на новый техпроцесс должны выиграть не только разработчики компонентов для инфраструктуры ИИ, но и проектировщики мобильных чипов. Новый техпроцесс позволяет повысить энергетическую эффективность чипов и их быстродействие. По сравнению с 3-нм техпроцессом и структурой транзисторов FinFET, новый 2-нм техпроцесс в сочетании с GAA позволяет при прежнем уровне энергопотребления поднять быстродействие на величину от 10 до 15 %, либо снизить энергопотребление на 25–30 % при неизменном быстродействии. Подобные качества будут востребованы в сегменте ИИ, поскольку огромное энергопотребление профильных ЦОД уже стало серьёзной проблемой, вынуждающей задуматься о перезапуске замороженных АЭС в отдельных регионах планеты, либо о строительстве новых. TSMC выйдет на ежемесячную обработку 100 000 кремниевых пластин с 2-нм чипами лишь к концу следующего года, поэтому соответствующие услуги будут оставаться в дефиците. Сейчас в получении от TSMC своих 2-нм чипов заинтересованы Apple, Nvidia, AMD и Qualcomm. Спрос на более зрелый 3-нм техпроцесс TSMC поддерживают Apple, Nvidia, AMD, Amazon и Intel. Бум ИИ также повлиял на рост популярности 7-нм техпроцесса в исполнении TSMC. Этот контрактный производитель намерен выпускать 2-нм чипы на семи действующих и строящихся предприятиях на Тайване. Предполагается, что их возможностей будет недостаточно для удовлетворения спроса на соответствующую продукцию. Это подтолкнуло компанию начать подготовку к строительству ещё трёх профильных фабрик на юге острова. При сохранении таких темпов экспансии капитальные затраты TSMC по итогам следующего года могут вырасти до рекордных $48–50 млрд. Новые техпроцессы обходятся в освоении и производстве гораздо дороже предыдущих, хотя бы в силу необходимости использования более сложного оборудования и оснастки. Canon, Kyocera и Honda тоже дадут денег на производство 2-нм чипов в Японии

12.12.2025 [10:16],

Алексей Разин

Пытающаяся наладить в Японии выпуск 2-нм чипов к 2027 году молодая компания Rapidus использует все возможные источники привлечения капитала, за исключением разве что публичного размещения акций. Количество существующих акционеров должно вырасти примерно до 30, среди них окажутся Kyocera, Canon и Honda Motor. Собирать деньги на выпуск 2-нм чипов будут буквально «всем миром» — японским.

Источник изображения: Rapidus Издание Nikkei Asian Review поясняет, что существующие акционеры типа Sony Group также сделают дополнительные инвестиции в капитал Rapidus. До конца марта компания рассчитывает привлечь те дополнительные $834 млн, которые закладывала в планы на текущий фискальный год, который закончится к тому времени. Среди новых акционеров Rapidus упоминаются поставщики оборудования и материалов для производства чипов типа Canon, Kyocera, Fujifilm Holdings и Ushio. Затронуты и не совсем близкие к полупроводниковой отрасли инвесторы типа Honda Motor и логистической компании Nippon Express Holdings. Формальные соглашения с каждым из новых инвесторов Rapidus заключит до конца текущего месяца, чтобы к марту получить от них средства. Каждая из компаний вложит от $3,2 млн до $128 млрд. Переговоры с некоторыми из потенциальных инвесторов до сих пор ведутся, их количество и состав могут измениться до конца месяца. Представители японского финансового сектора к идее инвестировать в Rapidus по-прежнему относятся прохладно, а потому местные банки вложат в капитал производителя чипов не более $160 млрд в совокупности. Тем не менее, ближе к началу выпуска 2-нм чипов компанией Rapidus японские банки готовы будут предоставить ей в долг около $12,8 млрд. Напомним, что на начальном этапе небольшая группа из восьми акционеров Rapidus вложила в капитал молодой компании в 2022 году не более $47 млн. В их число вошли SoftBank, NTT, NEC и Toyota Motor. С инвесторами активные переговоры о новых вложениях ведутся с лета 2024 года. К началу следующего десятилетия Rapidus рассчитывает привлечь ещё около $45 млрд, примерно $6,5 млрд предоставит в виде субсидий японское государство к марту 2028 года, а в общей сложности сумма субсидий достигнет $18,6 млрд. Серийное производство 2-нм чипов компания Rapidus рассчитывает начать в 2027 году. С одной стороны, увеличение количества акционеров Rapidus повышает шансы компании на получение достаточного для реализации проектов объёма средств. С другой стороны, необходимость в дальнейшем учитывать интересы всех из них заметно усиливает бюрократию при принятии управленческих решений. Японцы нашли способ выпуска 1,4-нм чипов без дорогущей EUV-литографии

10.12.2025 [10:14],

Алексей Разин

Японская Canon ещё осенью прошлого года отправила для изучения специалистам Intel первую установку для изготовления прогрессивных чипов методом нанопечати. По замыслу производителя, такая технология позволяет сократить расходы на оборудование при производстве 5-нм чипов и заметно экономить электроэнергию. Компания DNP недавно предложила материал для производства 1,4-нм чипов таким способом.

Источник изображения: Nikkei Asian Review, Dai Nippon Printing Как поясняет Nikkei Asian Review, японская компания Dai Nippon Printing разработала материал для изготовления специализированных матриц, позволяющих делать оттиск на поверхности кремниевых пластин, формируя рисунок для дальнейшего травления и превращения крохотного куска кремния в полупроводниковый чип. В 2027 году DNP намеревается наладить массовый выпуск таких расходных материалов, которые в комбинации с профильным оборудованием Canon для нанопечати позволят создавать 1,4-нм чипы. При этом расходы электроэнергии на изготовление чипа удастся снизить на 90 % по сравнению с традиционным литографическим оборудованием, использующим мощные лазеры. Строго говоря, и сама установка для нанопечати стоит около $6,4 млн, что в десятки раз меньше стоимости передового сканера ASML для изготовления 2-нм и более совершенной продукции. Именно традиционная литография, по данным японских источников, определяет от 30 до 50 % себестоимости чипов. Не только Intel заинтересовалась технологией нанопечати чипов. Южнокорейская Samsung Electronics, тайваньская TSMC, американская Micron Technology и японская Kioxia проявляют к ней интерес в той или иной мере, но их предприятия заточены под использование классической фотолитографии, и провести масштабную перестройку можно решиться, лишь обладая полной уверенностью в перспективности технологии нанопечати чипов. Некогда японские Canon и Nikon были ведущими поставщиками литографического оборудования, но в последние пару десятилетий они уступили нидерландской ASML, которая теперь контролирует 90 % рынка профильного оборудования. Fujifilm Holdings также обещала заняться выпуском материалов для нанопечати чипов, но пошатнуть позиции фотолитографии на современном рынке будет непросто. Приемлемо: Samsung наконец довела 2-нм техпроцесс до уровня брака ниже 50 %

25.11.2025 [11:38],

Алексей Разин

Ресурс TrendForce опубликовал традиционный дайджест, посвящённый текущему положению дел с освоением 2-нм технологии южнокорейской компанией Samsung Electronics. Уровень выхода годной продукции в рамках этого техпроцесса Samsung уже довела до приемлемых 55–60 %, а ещё она активно расширяет круг потенциальных клиентов, которые будут заказывать у неё изготовление чипов.

Источник изображения: Samsung Electronics Контрактное подразделение Samsung, которое на мировом рынке сейчас контролирует не более 7,3 %, может выйти на безубыточность по итогам 2027 года, если к тому времени компания введёт в строй своё передовое предприятие в Техасе. В США Samsung намеревается выпускать по 2-нм технологии процессоры Tesla AI6, но не факт, что их производство будет начато именно в 2027 году, поскольку к тому времени Tesla рассчитывает наладить поставки только менее современных чипов AI5. Если говорить о клиентах Samsung на контрактном направлении, то помимо Tesla, одним из крупнейших должно стать собственное подразделение Samsung LSI, разработавшее процессоры Exynos 2600. Кроме того, Apple заинтересована в получении от Samsung изготавливаемых этой компанией датчиков изображений, а ещё интерес к профильным услугам проявляют китайские разработчики майнингового оборудования, различные стартапы и даже Qualcomm. В отличие от TSMC, которая использовать структуру транзисторов с окружающим затвором (GAA) впервые начнёт именно в рамках своего 2-нм техпроцесса, у Samsung было достаточно времени, чтобы потренироваться в их изготовлении ещё в рамках 3-нм технологии. Скорее всего, это снизить вероятность проблем, которые могли бы возникнуть у Samsung при освоении 2-нм техпроцесса в комбинации с GAA. По оценкам самой Samsung, данное сочетание технологий обеспечивает прирост быстродействия транзисторов на 5 %, на 8 % повышает энергетическую эффективность и обеспечивает повышение плотности размещения транзисторов на 5 % по сравнению с собственным 3-нм техпроцессом Samsung второго поколения. Компания способна привлечь к своему 2-нм техпроцессу клиентов не только за счёт избытка желающих поручить выпуск чипов конкурирующей TSMC, которая просто не в силах справиться со всеми заказами, но и благодаря более гибкой ценовой политике. Кроме того, в отличие от TSMC, которая ориентируется главным образом на крупных заказчиков, Samsung готова работать и с мелкими. Например, она будет выпускать по 2-нм технологии чипы для южнокорейского стартапа DeepX, специализирующегося на теме искусственного интеллекта. Компании Charbright и Anaplash будут заказывать Samsung выпуск 4-нм и 28-нм чипов соответственно. TSMC уже получила заказы на выпуск 2-нм чипов от AMD, Apple и более десятка других клиентов

23.09.2025 [04:48],

Алексей Разин

Тайваньская компания TSMC, занимающаяся контрактным производством полупроводниковых компонентов, не очень охотно говорит о специфике своих взаимоотношений с клиентами, но из сторонних источников стало известно, что её услугами по выпуску 2-нм чипов воспользуются почти 15 клиентов.

Источник изображения: AMD Как поясняет Tom’s Hardware со ссылкой на стенограмму со страниц Seeking Alpha, о планах TSMC невольно проболтался президент компании KLA Ахмад Хан (Ahmad Khan) на минувшей конференции Goldman Sachs. Дело в том, что TSMC сама является клиентом этого поставщика оборудования для производства чипов, поэтому она делится с ним своими запросами и потребностями. «Техпроцесс N2 уже набрал около 15 клиентов, разрабатывающих дизайн своих чипов», — пояснил глава KLA. Не менее важно то, что около 10 из них относятся к сегменту высокопроизводительных решений — чипов, которые будут применяться в широком спектре продукции, от серверных систем до игровых консолей, а также ПК. По мнению Хана, 2-нм техпроцесс будет крупнейшим с точки зрения разработки чипов за первые три года своего активного внедрения. Напомним, к выпуску 2-нм чипов в массовых количествах TSMC приступает в этом году. Сами представители TSMC ранее отмечали, что техпроцесс N2 набирает популярность быстрее, чем N3 и N5 на сопоставимых фазах жизненного цикла. Это выразилось в том, что клиенты TSMC подготовили гораздо больше цифровых проектов с 2-нм продуктами в течение двух первых лет его доступности, чем в случае с предыдущими техпроцессами. TSMC исторически опирается на количество разрабатываемых продуктов при описании популярности своих технологий, но не перечисляет клиентов, а тем более — не раскрывает их имён без их ведома. Впрочем, в случае с 2-нм техпроцессом соответствующие признания уже сделали AMD и MediaTek, как минимум. Apple при выпуске своих новейших процессоров A19 сделала ставку на проверенный и при этом достаточно продвинутый N3E, но и она должна оказаться в числе крупных заказчиков 2-нм чипов у TSMC в следующем году. В семействе техпроцессов N2 будет как минимум три разновидности (N2, N2P и N2X), которые будут внедряться поэтапно. В случае с Intel ожидается, что некоторые кристаллы в составе процессоров Nova Lake будут выпускаться компанией TSMC по техпроцессам данного семейства в следующем году. Со временем получать от TSMC свои 2-нм чипы начнут компании Qualcomm и Broadcom. За выпуск 2-нм продукции TSMC будут отвечать как минимум три предприятия на Тайване, позже к ним присоединится и Fab 21 в американском штате Аризона. В истории с кражей 2-нм технологий TSMC подтвердился японский след: Tokyo Electron уволила подозреваемого

07.08.2025 [09:00],

Алексей Разин

На этой неделе стало известно, что тайваньские власти задержали нескольких человек, подозреваемых в неправомерном сборе информации о 2-нм технологии TSMC, которая считается критически важной для национальной безопасности. Наличие в истории японского следа подтвердилось сегодня, поскольку компания Tokyo Electron заявила об увольнении подозреваемого.

Источник изображения: Tokyo Electron Речь идёт о сотруднике тайваньского подразделения Tokyo Electron, который подозревается в неправомерном доступе к важной технологии партнёра. Компания Tokyo Electron является поставщиком литографического оборудования, поэтому её сотрудники на Тайване могли иметь формальные основания для взаимодействия с TSMC по данным вопросам. Поставщик оборудования лишь подтвердил своё сотрудничество со следствием, но отказался комментировать, какого рода информация могла быть похищена и в чьих интересах использована. Tokyo Electron ограничилась заявлением о том, что никакой конфиденциальной информации похищено не было. Компания считает соблюдение законов и этических норм одним из высших приоритетов в своей деятельности, а потому готова активно сотрудничать со следствием. Издание Nikkei Asian Review добавило, что подозреваемый теперь уже бывший сотрудник тайваньского представительства Tokyo Electron ранее успел поработать в TSMC. Представители правоохранительных органов острова посетили местное подразделение японской компании на прошлой неделе. С подачи сайта Tom's Hardware, который ссылается на тайваньские СМИ, стало известно о вероятной связи подозреваемого бывшего сотрудника Tokyo Electron с японской компанией Rapidus, которая рассчитывает к 2027 году наладить на своих мощностях выпуск 2-нм чипов на контрактной основе. Подозреваемый якобы передал Rapidus серию фотоснимков, имеющих отношение к технологическим процессам производства чипов по данным литографическим нормам. В этом ему, как предполагает следствие, содействовал сотрудник TSMC. |