⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Уйти от CISC — пойти на RISC: то ли ещё будет!

Успех процессоров с наборами сокращённых команд RISC I, II и MIPS, о которых мы рассказывали в предыдущей статье этого мини-цикла, был не коммерческим, но академическим. Свидетельством его стало объективное превосходство — рост скорости решения предлагаемых задач снижение потребного для этого числа транзисторов на чипе — в ходе лабораторных состязаний с широко распространёнными в то время CISC-компьютерами. Это были, напомним, университетские проекты; прикладная демонстрация возможностей наборов сокращённых команд, команд, прежде всего. Вместе с тем они стали грозным предупреждением для ориентированного на разработку микропроцессоров бизнеса: ведь обе эти разновидности RISC-архитектуры — пусть под руководством выдающихся исследователей, пусть при финансировании (не чрезмерно, кстати, щедром) со стороны оборонного ведомства — создали (каждую) всего-то примерно за год довольно узкие группы студентов и аспирантов. Соотношение вложенных средств и полученной отдачи впечатлило бизнес-круги настолько, что в начале 1980-х архитектура RISC пережила период натурального «Кембрийского взрыва». Один за другим были разработаны:

Photo\x86alt3-01 RISC-процессор Intel i860, изготовленный по 1-мкм техпроцессу, комбинировал 32-разрядное арифметически-логическое устройство с 64-битным блоком операций с плавающей запятой, а также включал интегрированный 64-разрядный же графический процессор, способный работать с 3D-изображениями: этот чип, так и не достигший коммерческого успеха, явно опередил своё время (источник: Wikimedia Commons) ⇡#Сузить бы!Одновременно с этим экосистема CISC, можно сказать, усыхала: отнюдь не по занимаемой ею доле ИТ-рынка (та как раз стремительно росла), но по числу конкурирующих на этом направлении проектов. Если в 1970-е между собой соперничали такие её представители, как Intel 8086, Motorola 68000, National Semiconductor 32016, то дополнительных игроков к ним в 1980-е не прибавилось, да и соперники Intel (не считая проявившей особую стойкость AMD) стали понемногу сходить со сцены. Что с экономической точки зрения вполне объяснимо: создание очередного уникального набора инструкций CISC (а повторением или прямым развитием пройденного он быть не может, ведь уже имеющиеся защищены авторскими правами) и проектирование под него специфического дизайна процессора — удовольствие дорогое, особенно с учётом закрытости уже имеющихся архитектур такого рода. И поскольку затеять новый чип на RISC — дело куда менее рискованное в плане изначальных затрат, разнообразие таких платформ оказалось куда более значительным. Другое дело, что каждая из них находила весьма ограниченный рынок сбыта, и вся экосистема RISC в результате развивалась заметно более сдержанными темпами, чем x86-направление — из-за банальной нехватки оборотных средств. Дело в том, что как раз в 1980-е массовые платёжеспособные пользователи (коммерческие и бюджетные организации прежде всего; рынок ориентированных на частного потребителя ПК был в денежном отношении куда как ýже) перестали воспринимать компьютеры как диковинные, едва ли не магические, агрегаты для произведения каких-то избыточно сложных расчётов, с которыми не справлялись штатные для первой половины XX века механические вычислители, — и начали рассматривать их в качестве рабочих инструментов для решения множества повседневных задач. Тем самым аппаратная (плюс на уровне архитектуры командных инструкций — ISA, Instruction Set Architecture) подоплёка работы ПК их конечных заказчиков, а точнее, их ИТ-отделы, интересовала уже в гораздо меньшей степени: им было важно, чтобы вычислительная система позволяла стабильно работать конкретному и уже широко доступному программному обеспечению. Эпоха локальной, в рамках самой организации, разработки потребного для решения её задач ПО если не прошла совсем, то откровенно стала клониться к закату. Большие исследовательские институты, крупные лаборатории, банки, промышленные предприятия могли позволить себе приобретать суперкомпьютеры под свои специфические задачи — располагая достаточными средствами и штатом квалифицированных ИТ-специалистов, способных переложить на доступные именно выбранным вычислителям языки высокого уровня нужные алгоритмы. Таким заказчикам пришлись по душе сравнительная дешевизна аппаратной части RISC-машин и широта возможностей программирования для этой исходно открытой спецификации (не конкретной процессорной архитектуры с набором уникальных для неё команд; разработчики той же MIPS ISA только с 2018 г. перестали требовать лицензионных отчислений). Подавляющему же большинству покупателей компьютеров — и частных, и представителей среднего/малого бизнеса, и из образовательных и иных бюджетных учреждений поскромнее — приходилось по одёжке протягивать ножки, исходно ориентируясь на подходящее для их целей ПО, а затем уже выбирая совместимую с ним аппаратную платформу. И в большинстве случаев они рано или поздно приходили к x86.

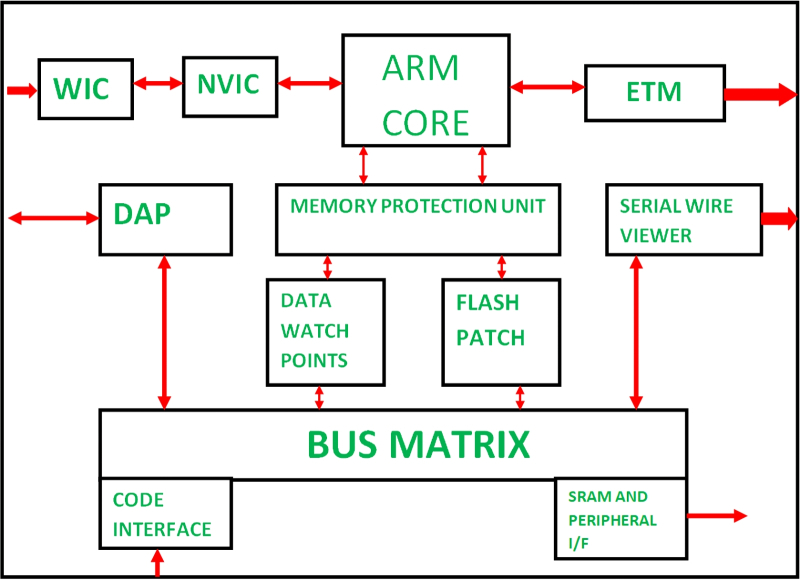

Блок-схема первого 32-разрядного процессора ARM с набором команд всего лишь из 25 инструкций, исполнение каждой из которых занимало ровно один цикл (источник: Wikimedia Commons) Широта разнообразия выходивших на рынок почти одновременно разновидностей RISC-компьютеров порождала ещё одну проблему: создаваемое для каждого из них программное обеспечение не было совместимым ни с одним другим напрямую, без хотя бы минимальной доработки. Доработка же требовалась, разумеется, ручная, — ни автоматизированных средств переложения исполняемого кода между платформами, ни достаточно мощных для налаживания виртуализации аппаратных средств тогда не имелось. ПО с открытым кодом эту проблему частично снимало: написанную на языке высокого уровня программу достаточно было скомпилировать на любой платформе, чтобы получить специфичную для той исполняемую версию кода. Впрочем, и здесь не всё проходило гладко: во-первых, исходный код востребованных рынком коммерческих программных продуктов (текстовых процессоров, редакторов электронных таблиц и т. п.) разработчикам тех не было никакого смысла обнародовать: кто бы тогда в здравом уме их приобретал? Во-вторых, ради повышения быстродействия многие программные пакеты писались тогда строго под определённую платформу, с включением фрагментов на языке специфического именно для неё ассемблера, с обращением с уникальным опять-таки в её случае регистрам, прерываниям и проч.: тут простой перекомпиляции откровенно бы не хватило. Словом, в 1980-х обширная библиотека самого разнообразного ПО, ориентированного на экосистему Wintel (процессоры Intel семейства x86 + ОС семейства Windows, на которое уже ориентировалось большинство программных разработчиков), непрерывно и едва ли не экспоненциально росла в объёме, — тогда как изначально фрагментированная архитектура RISC при всех своих бесспорных достоинствах прозябала на задворках общего прогресса глобального ИТ-рынка. Доходило до того, что ближе к концу 1980-х обозреватели, вполне сочувствовавшие архитектуре RISC, признавали, что коммерческого успеха она добьётся не раньше, чем за её серьёзное продвижение возьмутся бесспорные гранды тогдашнего направления ориентированных на ПК процессоров, — Intel, Motorola и, в меньшей степени, AMD. По оценке Computerworld, если в 1990 г. в мире было продано более 15 млн «IBM PC-совместимых» компьютеров, то суммарная реализация различных версий рабочих станций на базе RISC-процессоров — от Sun, той же IBM, HP, DEC и других — не достигли и 45 тыс. единиц. Счёт был, что называется, на табло. ⇡#Перегруппировка и наследованиеНеудивительно, что, хорошенько размежевавшись, RISC-ориентированные компьютерные вендоры стали понемногу объединяться. Sun принялась лицензировать свою архитектуру SPARC в 1989 г., формально передав права на неё некоммерческой организации SPARC International Inc., и тем самым привлекла к развитию этой ISA такие выдающиеся на тот момент ИТ-компании, как Fujitsu, Texas Instruments, Atmel, Cypress и Matsushita. В 1990-м Acorn совместно с Apple Computer и VLSI Technology образовали компанию Advanced RISC Machines Ltd. — ARM, — которая также активно принялась искать лицензиатов для дальнейшего продвижения своего варианта RISC-архитектуры. Весной 1991-го MIPS, DEC, Compaq, Microsoft и ещё около двух десятков компаний создали консорциум ACE (Advanced Computing Environment) — тот развивал спецификацию Advanced RISC Computing (ARC) на основе разработок, собственно, MIPS. Осенью того же года Apple (нимало не смущённая своим одновременным участием в ARM), IBM и Motorola сформировали альянс AIM — по первым литерам своих названий, — с амбициозной целью пошатнуть позиции экосистемы Wintel, взяв за основу RISC-процессор IBM Power: Motorola ради этого даже забросила развитие собственного проекта 88000. Детищем HP, ориентированным на поддержку её PA-RISC, стала в 1992 г. Precision RISC Organisation (туда вошли, в числе прочих, Hitachi, Mitsubishi, NEC и OKI). В том же году, кстати, Silicon Graphics попросту купила MIPS — настолько первой (для оснащения своих перспективных графических рабочих станций) оказались необходимы разрабатываемые второй процессоры: консорциум ACE вскоре после этого развалился.

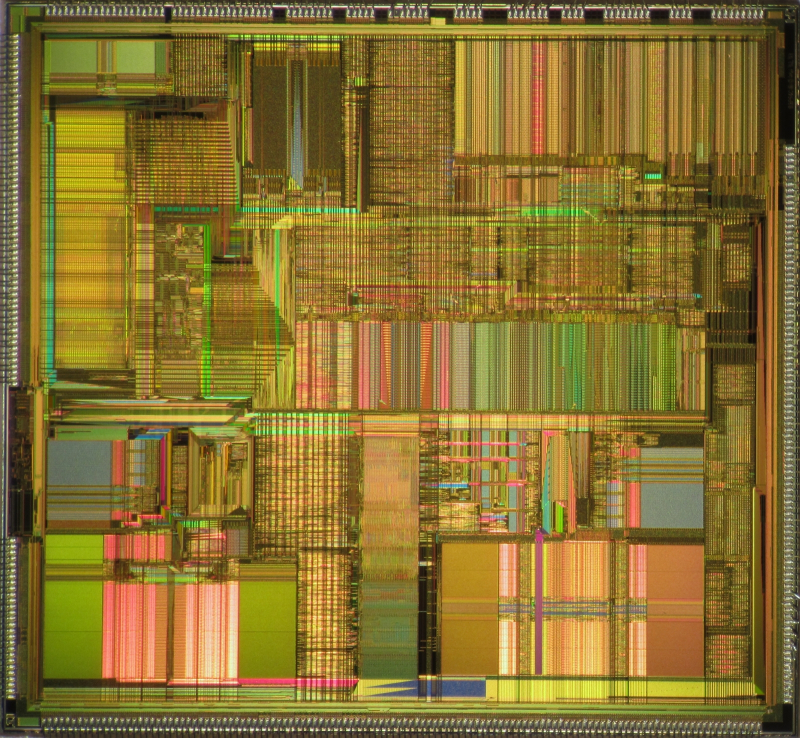

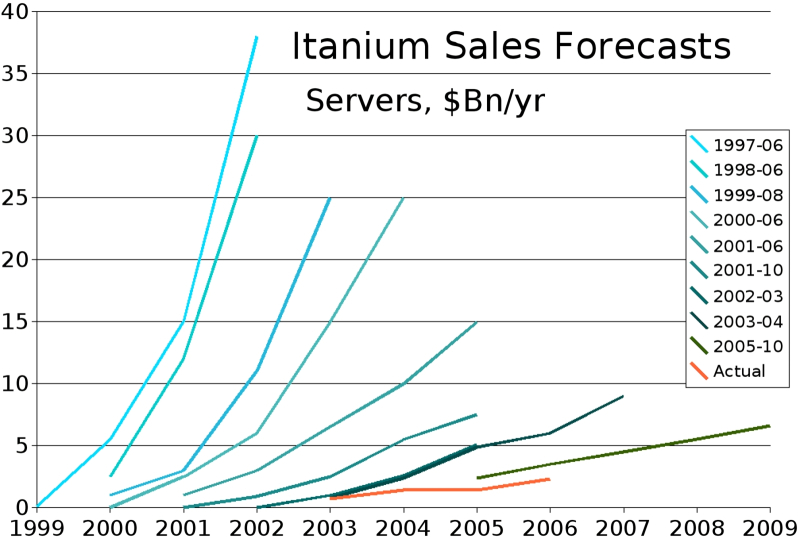

Поскреби CISC-процессор Pentium, в данном случае модель A80502-100 SX963 (P54C), — найдёшь заимствования из RISC-архитектуры (источник: HARDWARECOP) Тогда же, в 1990-х, доминирующие разработчики CISC-процессоров начали приглядываться к появлявшимся на RISC-направлении инновациям. Так, выпущенный в 1991 г. процессор MIPS R4000 оказался одним из первых коммерчески подлинно успешных 64-разрядных ЦП (а иначе с чего бы Silicon Graphics обратила на него внимание?), а в 1999-м AMD создала свой первый процессор с 64-разрядным дополнением к классическому 32-битному набору инструкций x86. Суперскалярный RISC-процессор DEC Alpha 21064, способный исполнять до двух инструкций за один цикл, появился в 1992-м, — а в 1993-м Intel вывела на рынок свой Pentium, первый x86-чип суперскалярного дизайна. В 1994 г. процессор PA-7100LC разработки HP с расширением MAX Instruction Set Extension стал первым в мире ЦП общего назначения, реализовавшим подход SIMD (Single Instruction, Multiple Data; параллелизм на уровне данных — за счёт исполнения на одном ядре инструкций для работы с несколькими короткими векторами), причём сразу в приложении к обработке мультимедиа, и уже в 1997-м набор инструкций Intel x86 пополнили команды MMX SIMD. Началось то самое проникновение RISC-принципов в CISC-экосистему, о котором мы упоминали в предыдущей статье и логическим венцом которого стала парадигма EPIC (Explicitly Parallel Instruction Computing; не путать с серией серверных ЦП AMD EPYC), призванная совместить лучшие стороны RISC и CISC, избавившись одновременно от их недостатков. Увы, первое же коммерческое семейство EPIC-процессоров, Intel Itanium (архитектура IA64), провалилось, причём с треском, — проиллюстрировав тем самым поговорку «лучшее — враг хорошего»: уж слишком стремительно прогрессировала к тому времени ветка x86. С теми задачами, которые чипы EPIC должны были реализовывать на аппаратном и ISA-уровне, непрерывно ускорявшиеся ЦП семейства x86 прекрасно справлялись на более высоком программном. Собственно, как раз бурная эволюция экосистемы x86 вплоть до начала 2010-х по большей части и препятствовала развитию альтернативных архитектур. Все оптимизации, которые те предлагали, сводились на нет возможностью исполнять неоптимизированный код на привычных CISC-системах (пусть даже с немалыми вкраплениями RISC внутри) ещё быстрее: хватало бы только мощности систем охлаждения для отвода выделяемого в этом процессе тепла!

Весьма впечатляющее сравнение маркетинговых посулов относительно того, как будут расти продажи серверов с процессорами семейства Itanium (различные оттенки сине-зелёного — в зависимости от года, когда очередной прогноз публиковался), с фактическими данными об их реализации (оранжевая линия) (источник: ExtremeTech) К середине 2010-х (после того, как компания MIPS, отделившись от Silicon Graphics, пошла по рукам, а позже и вовсе отказалась от развития одноимённой архитектуры в пользу RISC-V) едва ли не главную роль в оскудевшей разработчиками экосистеме RISC стала играть компания ARM, как раз примерно в то время сменившая типографику собственного наименования на Arm, чтобы оно не смешивалось с названием одноимённой процессорной архитектуры. Секрет успеха этих разработчиков, которые исходно не могли похвастать сопоставимыми с IBM, HP или иными тяжеловесами возможностями, — продуманный и обоснованный выбор стратегии развития. Руководство Arm, проведя классический для попавшего в затруднительное положение бизнес-проекта анализ SWOT (Strengths, Weaknesses, Opportunities, Threats — «достоинства, уязвимости, возможности, угрозы») приняла решение ориентироваться на те ниши, которые её более крупным и состоятельным соперникам были попросту не интересны: на встраиваемые и портативные устройства. Ведь, хотя x86-процессоры действительно хорошо справлялись с не оптимизированными под себя задачами, делали они это за счёт проведения избыточных вычислений — расходуя много энергии и (вспоминаем про особенности архитектуры CISC) требуя чрезмерно большого числа транзисторов для реализации своих разнообразных вычислительных контуров. Мобильная же и промышленная электроника нуждается как раз в оптимизации на уровне «железа» и командной архитектуры, ISA, — в том, что и было изначальным преимуществом архитектур с наборами сокращённых команд. Кроме того, компания решила сама не заниматься проектированием конкретных процессоров, — создавая лишь общий инженерный дизайн и лицензируя партнёрам свои разработки. Взамен же она требовала довольно скромных отчислений с каждого ARM-ядра в составе процессора в каждом проданном конечному заказчику партнёрском ИТ-устройстве. ⇡#Теперь и для ИИМетодичное, последовательное движение разработчиков из Arm по объективно выбранному курсу принесло свои плоды уже совсем скоро — когда в начале 2010-х занялась заря эры смартфонов, а затем и «умных» (в тогдашних терминах, не имевших никакого отношения к ИИ) устройств, способных выполнять определённый — пусть сильно ограниченный — круг задач без участия человека. Оконный датчик, выдающий команду автоматизированной рольшторе опуститься, как только окно на южной стороне дома заглядывает летнее солнце; система машинного зрения, при помощи которой робот-пылесос составляет карту своих перемещений по квартире; сенсор протечки, что перерывает воду в аварийной ситуации — всё это примеры встраиваемых систем, контроллерам которых попросту не требуются обеспечиваемые архитектурой CISC супервозможности. А уж про мобильные телефоны и говорить нечего: ёмкость аккумулятора никогда не бывает избыточной, и потому чем энергоэффективнее функционирует система-на-кристалле в составе смартфона, тем продолжительнее время его автономной работы — и тем выше удовлетворённость его владельца от взаимодействия с таким экономичным аппаратом.

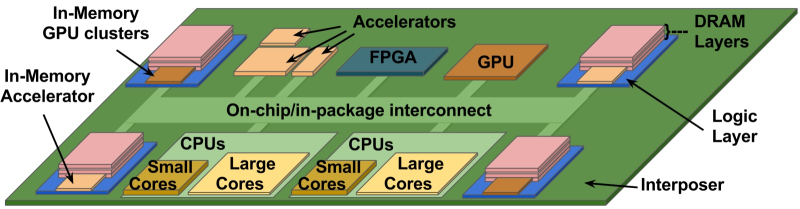

Гетерогенная процессорная архитектура подразумевает использование маломощных ядер для исполнения простых задач и более производительных — для сложных (источник: The University of Texas at Austin) Если центральный x86-процессор для ПК с лёгкостью может потреблять до 200 Вт (и это далеко не предел), то типичному смартфонному ARM-чипу исходно требовалось 2-3 Вт, не более. Дополнительно снижать энергозатраты помогает гетерогенная вычислительная архитектура big.LITTLE, в рамках которой потенциальная энергоёмкость каждой поступающей на процессор задачи в сочетании с её приоритетностью определяет, на каком именно ядре в составе кристалла та будет исполняться: на организованном совсем просто, к которому вдобавок подведено пониженное напряжение, или же на более производительном и конструктивно сложном. Под характерными для смартфонов нагрузками, как утверждают в Arm, архитектура big.LITTLE обеспечивает сбережение до 75% энергии по сравнению с аналогичной ARM-архитектурой с унифицированными ядрами. Уже в 2010 г. в мире было реализовано 6,1 млрд ARM-чипов — на них приходилось тогда 95% смартфонного рынка, 35% сегмента телеприставок и медиаплееров, 10% поставок мобильных ПК (кто-нибудь вспомнит сейчас, что были даже ARM-неттопы?) Интересно, что со временем архитектуры RISC и CISC, вроде бы разошедшиеся по разным экологическим нишам — ПК и серверы для первой, мобильные и встраиваемые системы для второй, — начали предпринимать попытки взаимного проникновения. Помимо уже упомянутых, но всё-таки воспринимавшихся как экзотика мини-ноутбуков на чипах ARM, сама Microsoft старалась продвинуть фирменный планшет Surface под ARM-ориентированную версию Windows RT — увы, не оправдавшую надежд как раз по причине отсутствия достаточного количества стороннего ПО, которое необходимо было под эту бюджетную (и потому с деловой точки зрения не слишком привлекательную) платформу перекомпилировать. В свою очередь, Intel попыталась выйти в сегмент смартфонов с «экономичным» семейством процессоров Atom — но принципиальная аппаратная расточительность архитектуры CISC не позволила по этому параметру всерьёз состязаться с чипами ARM. К началу 2020-х, тем не менее, сложился вполне устойчивый статус-кво: для решения высокопроизводительных задач выбирали системы на базе x86, для энергоэффективных — на ARM. Казалось, всё так и будет развиваться — по крайней мере, пока не окажутся доведены до ума какие-нибудь квантовые вычислители, — но вдруг разразился ИИ-бум, и главное преимущество архитектуры CISC — высочайшая гибкость при обработке сложных команд переменной длины — разом потеряло свою актуальность.

ARM-планшет Surface с Windows RT на борту — практически единственная аппаратная платформа, на которой эта ОС (и скудная коллекция ПО под неё) в принципе могла исполняться. Нет, инициативу сперва поддержали как минимум Lenovo, Asus, Samsung и Dell, но продажи оказались настолько скромными, что энтузиазм партнёров быстро угас (источник: Microsoft) Основная процедура, исполняемая в ходе эмуляции работы многослойных плотных нейросетей на фон-неймановских компьютерах, — матричное умножение. Операция эта с вычислительной точки зрения чрезвычайно проста, — вот только производить её надо над огромным количеством операторов, которое грубо определяется числом параметров модели: 671 млрд всего (из них 37 млрд активных) у DeepSeek R1 и V3; возможно, уже больше триллиона (точную величину разработчики скрывают) у GPT-5, Claude Opus 4.1 и Gemini 2.5 Pro. Неудивительно, что архитектура ARM здесь оказывается в выигрыше — благодаря ориентации как раз на ограниченное число недлинных команд, огромным объёмам регистровой памяти в непосредственной близости от логических контуров, а также дополнительным оптимизациям. Вслед за расширениями SIMD, введёнными ещё в версии Armv7, более современный вариант Armv9 предлагает, чтобы ускорить задачи машинного обучения, модифицированное масштабируемое векторное расширение (Scalable Vector Extensions 2, SVE2) и масштабируемое матричное расширение (Scalable Matrix Extension, SME), которые ещё более упрощают операции над векторами и матрицами соответственно. Специальные же инструкции BFDOT и BFMMLA для обработки чисел в формате BFloat16 (BF16), адаптированном для нейронных сетей, дополнительно ускоряют матричное умножение, одновременно кратно снижая требования к объёму памяти и пропускной способности. Разумеется, мощный x86-процессор, обладая доступом к сопоставимым объёмам ОЗУ, справится с такого рода задачами тоже вполне уверенно, — но задержки в ходе исполнения у него окажутся объективно больше (как раз по причине меньшей ёмкости регистровой памяти), а энергопотребление — кратно выше. И последний аргумент в наши дни — едва ли не решающий: к новым ИИ-ориентированным ЦОД и так уже чуть ли не ядерные реакторы собираются пристраивать, чтобы удовлетворить непомерные аппетиты нынешних специализированных вычислителей, — тут уж не приходится пренебрегать никаким способом сэкономить на электропитании не в ущерб вычислительной мощи. Плюс к тому, поскольку архитектура графических ускорителей AMD и особенно Nvidia по духу близка к RISC (в части множества ориентированных на решение простых задач ядер и значительного объёма регистровой памяти), ЦП на базе ARM эффективнее взаимодействуют с такими ускорителями, чем построенные ан CISC-принципах, — что подтверждает та же Nvidia, предлагая для ИИ-задач свои системы с центральными процессорами Grace (весьма коммерчески успешные системы, кстати). ЦП архитектуры ARM готовят и/или уже развёртывают на своих серверах Microsoft (проект Cobalt 200), Google (ориентированный специально на применение в ЦОДах процессор Axion), AWS (целая серия чипов Graviton) и т. д. С учётом же того, насколько стремительно растёт доля ИИ-вычислений в общем объёме нагрузок на дата-центры — именно под такие нагрузки, по оценке McKinsey, уже оптимизирована треть ЦОДов в мире, а к 2030 г. энергоёмкость дата-центров за счёт тренировки исполнения генеративных моделей утроится по сравнению с нынешней, — можно считать, что на глобальном уровне архитектура RISC всё-таки одерживает победу над CISC, пусть и несколько, на полвека примерно, запоздалую. До 70% вычислительной нагрузки на дата-центры гиперскейлеров к тому же 2030 г., по оценкам аналитиков, будет создавать решение ИИ-задач, — это ли не победа? Другое дело, что если пресловутый «пузырь искусственного интеллекта» всё-таки лопнет, CISC как более универсальная экосистема наверняка переживёт ренессанс, — но это будет уже совсем другая история.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|