Хотя Китай находится под санкциями в плане возможности закупок передового оборудования для производства чипов, включая оперативную память, работе исследователей это сильно не вредит. Более того, санкции заставляют активнее искать альтернативы классическим производствам, включая разработку перспективных архитектур. Одним из таких открытий стала разработка китайскими учёными архитектуры ячейки DRAM без обязательного конденсатора.

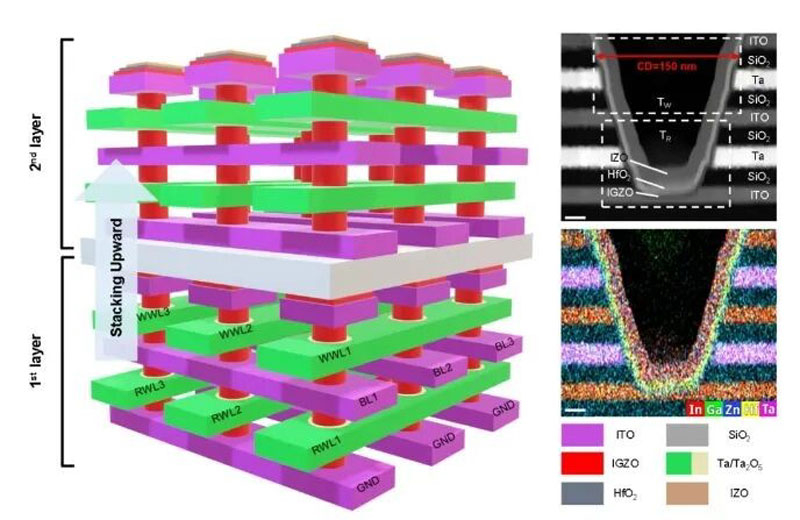

Источник изображения: IME CAS

О разработке сообщили исследователи из Института микроэлектроники при Китайской академии наук (IME CAS), создавшие техпроцесс производства новой памяти совместно с другими научными учреждениями Китая. В общем случае речь идёт о ячейке DRAM стандартного относительного размера 4F² (это минимальный размер классической ячейки памяти с одним транзистором и одним конденсатором). Тем самым ячейка новой архитектуры не больше классической, что уже намекает на хорошие перспективы разработки.

Самое важное, что «китайская» ячейка не содержит отдельного конденсатора для хранения заряда (данных), что всегда служило проблемой для снижения масштаба техпроцесса производства DRAM. Вместо этого заряд хранится в канале управляющего транзистора ячейки, иначе называемого плавающим зарядом. Более того, у ячейки два управляющих транзистора (схема 2T0C), что позволяет им хранить заряд совместно в одном общем канале. Это повышает стабильность работы ячейки во всех режимах, включая снижение токов утечек. Также эта архитектура даёт возможность записывать два бита данных в каждую ячейку, обеспечивая четырёхуровневое значение заряда.

Не менее хитро продуман техпроцесс производства новой памяти, и он предельно простой — заключается всего в одном экспонировании и одной обработке после экспонирования. Литографическая обработка производится сразу для заранее подготовленной многослойной пластины, состоящей из пяти нанометровых слоёв полупроводников, таких как материалы IGZO, тантал и другие, разделённых четырьмя слоями изолятора в лице диоксида кремния.

В пластине за один проход вытравливаются углубления до 120 нм, стенки которых затем отжигом и напылением превратят в элементы транзисторов. Каждое углубление представляет собой два транзистора и, фактически, одну ячейку памяти. Транзисторы изготавливаются за один проход и поэтому не требуют совмещения по осям — процесс происходит как бы с самовыравниванием. Верхний транзистор отвечает за запись ячейки, а нижний — за чтение. Между ними физически расположен канал, одновременно являющийся местом для хранения заряда. Похоже, что проще техпроцесса для выпуска DRAM не придумать, что может стать основой для массового производства относительно недорогой оперативной памяти.

Согласно проведённым исследованиям образцов новой памяти, ячейка может хранить данные 470–500 секунд без регенерации. Это не NAND-флеш, но тоже интересно с точки зрения снижения потребления новой архитектурой DRAM. Данное свойство может быть востребовано во встраиваемой архитектуре DRAM для мобильных применений. Задержка чтения составляет 50 нс, что сопоставимо с возможностью DDR5. Температурные дрейфы напряжения затвора находятся в допустимом диапазоне — менее 100 мВ для 85 °C. Одним словом, хоть сейчас в производство. Кстати, техпроцесс идеален для стекового многослойного выпуска оперативной памяти, с чем сегодня пока проблемы.

Впрочем, ещё вопрос, попадёт ли эта память в производство. Очевидно, что одних лабораторных исследований для этого недостаточно. Неясны уровень брака и повторяемость характеристик в производственных условиях. Как бы там ни было, от лабораторных экземпляров до серийных чипов могут пройти даже не годы, а десятилетия, как показывает практика внедрения ReRAM, FeRAM, MRAM и других типов перспективной памяти.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018