⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Процессор Cell: шаг в будущее

PowerPC "восстаёт из пепла" Апрель 1993 года. Сформированный двумя годами ранее альянс Apple, IBM и Motorola объявил о выпуске первого процессора на базе революционной архитектуры PowerPC - PowerPC 610 с частотами 50 и 66 МГц. Новинка была призвана составить достойную конкуренцию чипу Pentium из мира x86. Эра PowerPC началась. За PowerPC 610 последовали модели второго поколения с индексами 603/604, принёсшие с собой незначительные нововведения. В 1997 году появился PowerPC 750 (a.k.a. G3) - чип третьего поколения, отличавшийся от предшественников увеличенной частотой системной шины и встроенным L2-кэшем. Выпуск 31 августа 1999 года компанией Motorola процессора PowerPC 7400 (G4) явил миру блок векторных вычислений AltiVec, позволивший зачислить компьютеры PowerMac G4 на его основе в ранг настольных суперкомпьютеров. Будущее PowerPC казалось "безоблачным". Первые "подводные камни" появились во время мучительных попыток Motorola преодолеть гигагерцовый рубеж. Бросив идею дальнейшего развития PowerPC 74хх "под откос", компания сосредоточила все свои силы на процессоре PowerPC 8500 (первый G5). Но, из-за задержек Motorola с выпуском больших партий годных чипов зародилось мнение о том, что архитектура PowerPC отжила свой недолгий век, а сам PowerPC 8500 стал "надгробным камнем" на "могиле" отдела компании по производству настольных процессоров.  Дальнейшее развитие архитектуре PowerPC дала IBM, разработав в 2002 году 64-разрядный процессор PowerPC 970 (G5). За ним последовал улучшенный PowerPC 970FX, а на горизонте уже "маячит" двуядерный PowerPC 970MP. Не будем забывать и про чипы PowerPC 8641D (два процессора поколения G4 с 1 Mb L2-кэша на каждое ядро, встроенные контроллеры DDR2 RAM, PCI-Express, Gigabit Ethernet и RapidIO), разрабатываемые компанией Freescale. Впрочем, архитектура всех этих чипов, как и x86, практически не изменилась со времён появления на рынке PowerPC 750/7400. И вот, настал момент очередного скачка в развитии PowerPC, как качественного (в плане инноваций), так и количественного (в плане распространённости). Имя ему - архитектура Cell (от англ. "cell" - клетка, ячейка).  Когда?О своём намерении выйти на рынок графических рабочих станций с собственным процессором президент SCEI (Sony Computer Entertainment Inc.) Кен Кутараги (Ken Kutaragi) заявил в начале 2000 года. В то время компания собиралась начать массовые поставки чипа Emotion Engine, являвшегося ЦП для игровой консоли PlayStation 2 (и изначально для неё разработанного). К сожалению, трудности Sony с производством процессора, сложность его программирования, и, самое главное, отсутствие сильных партнёров не позволили осуществиться мечтам Кутараги.  Хотя кое-чего компания всё-таки смогла достичь. Вспомним про GScube, разработанный самой SCEI и представленный публике на конференции Siggraph 2000. Данная, хм, рабочая станция состояла из 16 связок чипов Emotion Engine и Graphics Synthesizer (PlayStation 2), объединённых в единую параллельную систему, оснащённую 2Gb оперативной и 512Mb видеопамяти.  GScube изначально предназначался в качестве отработки навыков в создании игр для PlayStation 3 (уже тогда будоражившей умы учёных SCEI), но, способный обрабатывать 1,15 млрд. полигонов в секунду (при HDTV-разрешении 1920x1080 пикселей), был принят на вооружение в качестве "визуализатора". Созданные студиями Square Pictures (фильм "Последняя фантазия: духи внутри нас") и Manex Visual Effects (компьютерная графика в фильме "Матрица") демки поражали своей сложностью и фотореалистичностью. Тем не менее, из-за того, что GScube не был самодостаточным и требовал для своей работы сервер SGI Origin 3400, купить его могли себе позволить немногие.  Впоследствии SCEI увеличивала количество связок чипов с 16 до 64, но рынок оставался по прежнему "холоден". GScube не прижился. Тем не менее, компания не потеряла надежду стать "Intel в лагере PowerPC", и, заручившись поддержкой корпораций Toshiba, IBM и своей "мамы" Sony (сформировавшийся альянс получил название STI), приступила к созданию архитектуры Cell. Впервые описание работы процессора стало доступно после регистрации 22 марта 2001 года патента № 6809734 и заявки на патент № 20020138637 . Автором патента значился Сузуоки Масаказу (Suzuoki Masakazu), глава процессорного подразделения SCEI и разработчик Emotion Engine. Со временем в прессу стали просачиваться всё новые подробности относительно Cell, а 7 февраля на конференции ISSCC 2005 (International Solid State Circuits Conference) IBM, Toshiba и SCEI рассказали публике об архитектуре чипа, его применении, и своих будущих планах. Благодаря этому, на сегодняшний день можно более менее чётко обрисовать картину того, что же нас ждёт в конце 2005 - начале 2006 года. Философия CellПринципы, заложенные в архитектуру нового чипа, были разработаны в начале 2000 года инженерами IBM. Идея массового параллелизма, на основе которой работает Cell, была заложена в так называемую ("cellular architecture") "клеточную архитектуру", в которой для создания суперкомпьютеров используется множество однотипных процессоров (от 10 тыс. до 1 миллиона), каждый из которых оснащён собственным контроллером RAM и определённым объёмом самой оперативной памяти. Стоит также вспомнить про Beowolf-кластеры, построенные на базе простых компьютеров-"кирпичиков" и объединённые в единую систему. В 2001 году во время обнародования первых данных Кен Кутараги сопоставил Cell с построенным по принципу кластерной системы суперкомпьютером Deep Blue. Сравнение было дано не просто так: оно отображает саму философию Cell. "Благодаря встроенной возможности объединения чипов Cell, микропроцессоры, являющиеся сегодня "индивидуальными островками", будут связаны между собой более тесно, благодаря чему сеть на основе таких процессоров превратится в одну унифицированную "суперсистему". Как простые биологические клетки в теле, объединяющиеся для создания полноценных физических систем, электронные устройства на базе Cell будут блоками для больших систем", - так описывал Кутараги концепцию Cell. Что же значат его слова? Cell может работать не только в качестве, собственно, процессора, но и в качестве элемента большой системы. Путём объединения различной техники, содержащей чипы Cell, можно построить единую сеть, которая будет функционировать, как одно "устройство". Представим следующую ситуацию: консоль PlayStation 3 подключена к HDTV-телевизору, к которому, в свою очередь, подключён Blu-Ray-рекордер. Все три устройства оснащены процессорами Cell. Пользователь, играя в какой-нибудь WipeOut Fusion 2, даёт команду рекордеру записать очередной заезд в HDTV-формате. При этом Cell в телевизоре помогает своему "напарнику" записывать игру. После записи освободившиеся Cell'ы телевизора и рекордера "спешат на помощь" процессору PlayStation 3, в результате чего количество FPS в игре многократно ускоряется. Таким образом, производительность отдельных Cell-устройств в сети может повышаться за счёт процессоров других устройств. Причём чипам безразлично, где находятся другие элементы сети: в одной комнате, доме, городе, или на другом континенте. Да и устройства, кстати, могут быть абсолютно разные: от уже упоминавшихся игровых консолей и телевизоров до персональных компьютеров, КПК и даже мобильных телефонов! Единая глобальная сеть. Разве не об этом долгие годы мечтают писатели-фантасты? С приходом Cell мечты могут стать реальностью. Но мы отложим их на потом и перейдём к теме статьи - процессору Cell. "Клетка"

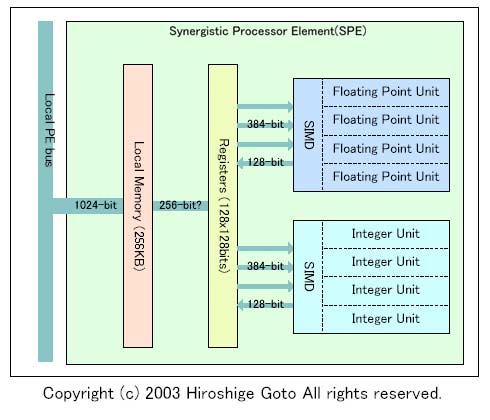

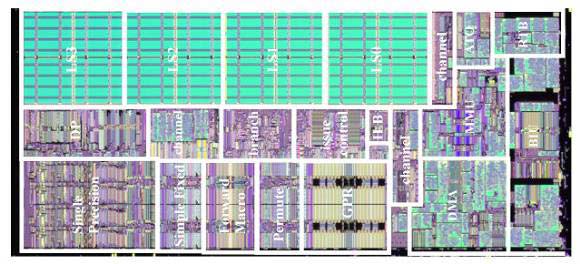

Процессорный элемент на основе POWER-архитектурыК сожалению, на ISSCC 2005 о PPE рассказывали меньше всего, поэтому такие важные характеристики процессорного ядра, как его архитектура и производительность остались "за кадром". Тем не менее, кое-какие данные нам уже известны. PPE представляет собой два 64-разрядных процессорных ядра (на основе POWER-архитектуры) с поочерёдным выполнением команд (in-order execution), в отличие от внеочередного выполнения (out-of-order execution), присущего всем современным процессорам. PPE поддерживает технологию одновременной обработки двух потоков (SMT - Simultaneous Multi-Threading), примерным аналогом которой является Hyper-Threading в Pentium 4. В PPE присутствует блок VMX (VMX - Vector Multimedia eXtensions, более известный как AltiVec). Объём кэша L1 составляет 64 Kb (по 32 Kb на кэш инструкций и данных), L2-кэша - 512 Kb. Несмотря на сравнительно небольшой 11-стадийный конвейер PPE, представители STI заверяют, что запас по наращиванию частоты у Cell очень большой. Стоит сказать пару слов об архитектуре PPE. Из-за отсутствия информации многие стали гадать, какой же процессор будет положен в её основу. Большинство "за" упрощённый POWER 5, часть отдаёт "предпочтение" PowerPC 970. Но оба варианта вызывают явные сомнения. Оспаривая их достоинства и недостатки, люди забывают, что разработка POWER 5 и PowerPC 970 велась в 2000-2004 годах, и они не были готовы к 2000 году, когда были начаты работы над Cell. Более вероятно следующее. В конце прошлого столетия IBM решила создать процессор, работающий на сверхвысоких, как для того времени, частотах. В результате исследований в 1998 году в журнале Journal of Solid State Circuits (JSSC) был описана реализация чипа, основанного на части инструкций POWER-архитектуры. В 2000 году на конференции ISSCC 2000 стал доступен пресс-релиз, описывающий процессор на основе "полной" POWER-архитектуры, работающий на частоте 1 GHz (13-стадийный конвейер, тех. процесс 0,25 мкм). В дальнейшем прототип был переделан в сторону увеличения частоты (уменьшен конвейер) и уменьшения тепловыделения (улучшенный тех. процесс и применение всех современных технологий при производстве). Кроме того, были добавлены SMT и блок VMX. В результате получился PPE. Но "гадание на кофейной гуще" - не наша задача, поэтому давайте перейдём к SPE, благо о нём известно практически всё. Синергический процессорный элемент Синергический процессорный элемент представляет собой специализированный векторный процессор, обрабатывающий SIMD-инструкции (аналог SSE в Pentium и 3Dnow! в Athlon). Архитектура SPE довольно проста и напоминает процессоры эры PowerPC 601 и первых Pentium: четыре блока для работы с целочисленными векторными операциями и четыре блока для работы с числами с плавающей запятой. Правда, при этом большинство арифметических инструкций представляют собой 128-разрядные векторы, разделённые на четыре 32-битных элемента. Каждый SPE оснащён 128 регистрами, разрядность которых - 128-бит. Вместо кэша L1 процессор содержит 256 Kb собственной "локальной памяти" (local memory, также называемой local store) разделённой на четыре отдельных сегмента по 64 Кбайт каждый, а также DMA-контроллер. Последний предназначен для обмена данными между основной памятью (RAM) и локальной (LM/LS), минуя PPE. Локальная память, по сути, выполняет роль кэша L1, но при этом полностью контролируется программистом, вследствие чего организована значительно проще. Достигается это путём переноса логики контроля за переполнением кэша из самого чипа в программный код, что способствует облегчению архитектуры локальной памяти (отсутствует поиск в RAM при каждом обращении к LM, упреждающая выборка и т.д.). Благодаря наличию динамического механизма защиты памяти доступ к каждому SPE в Cell может быть закрыт, вследствие чего данные, обрабатывающиеся этим процессором, будут недоступны другим (например, в Cell другого устройства). Несмотря на то, что SPE представляет собой векторный процессор, он не является аналогом VMX/AltiVec. Как уже говорилось, SPE - отдельный микропроцессор, выполняющий собственные команды, а VMX являются блоком (подмножеством команд), выполняемых PowerPC (G4/G5).  В результате всего вышеперечисленного можно сделать вывод, что SPE довольно похож на векторные блоки Emotion Engine: локальная память, четыре 32-битных векторных регистра, команды инициализации DMA и т.д. В принципе, в этом нет ничего особенного: Sony и Toshiba (которой, кстати, принадлежит большое количество патентов на векторные вычисления, полученные во время создания "медиапроцессоров" для цифровой техники в середине 90-х) работали над созданием Emotion Engine (равно как и Graphics Synthesizer), и часть архитектуры старого процессора легла в основу нового. Для каких целей могут быть использованы SPE? Ответ на этот вопрос тянет на отдельную статью, так что ограничимся самым важным. Одной из областей применения Cell аналитики считают рынок цифровых сигнальных процессоров (DSP - Digital Signal Processor), высокая скорость которых обусловлена многопоточным просчётом векторных инструкций. Восемь параллельно работающих SPE позволяют составить достойную конкуренцию специализированным DSP-процессорам. Установка PCI-E-платы с Cell в простой компьютер будет невероятной находкой для музыкантов и учёных. Если использовать Cell для построения видеокарты (возможен и такой вариант), то SPE могут служить пиксельными шейдерами и будут использоваться для конвейера просчёта. Не смейтесь. Сама IBM во время ISSCC 2005 заявила, что считает Cell комбинацией процессора и графического чипа. Благодаря прямой связи между всеми SPE с помощью шины EIB (о которой мы поговорим чуть ниже), а также локальной памяти в их составе, существует возможность динамически переключать различные процессорные элементы на выполнение той или иной части конвейера просчёта. Чтобы не быть многословными, перечислим возможности использования SPE через запятую: просчёт физических моделей, тесселяция поверхностей высшего порядка в полигональные модели, инверсная кинематика, скелетная анимация, обработка воксельных данных, анимация частиц, компрессия/декомпрессия видеоданных в формате MPEG4 "на лету", просчёт алгоритма ray-tracing "на лету", преобразование аудиоданных из одного формата в другой "на лету", обработка алгоритмов шифрования, искусственного интеллекта… это предложение можно продолжать очень долго, но мы остановимся и перейдём к следующему элементу архитектуры Cell. Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|