⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Микроархитектура Intel Sandy Bridge, часть I

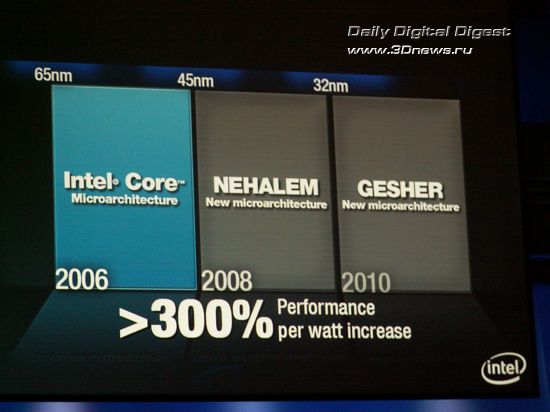

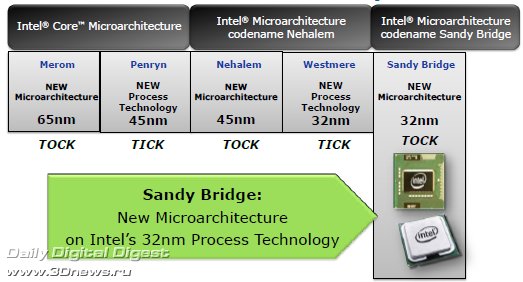

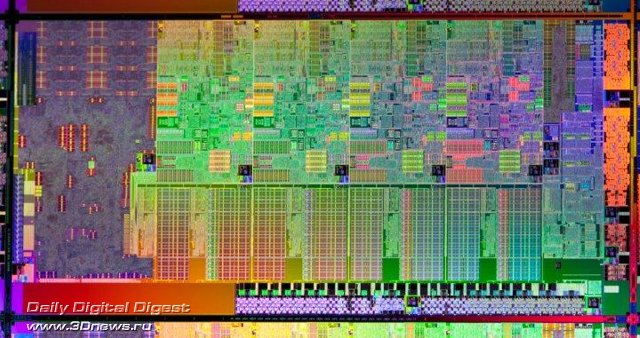

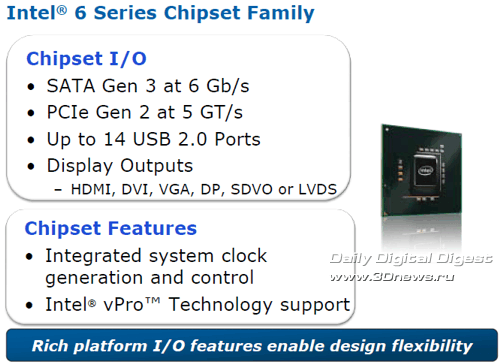

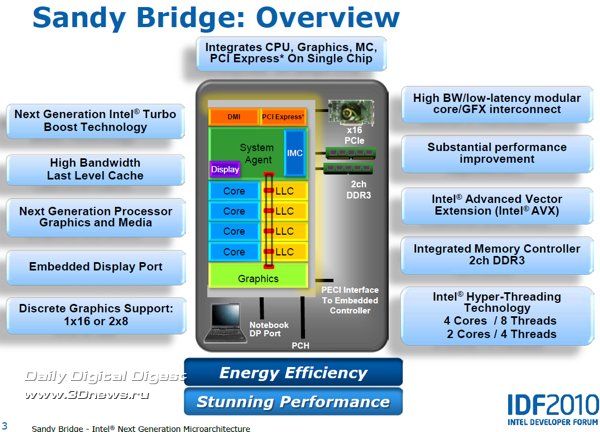

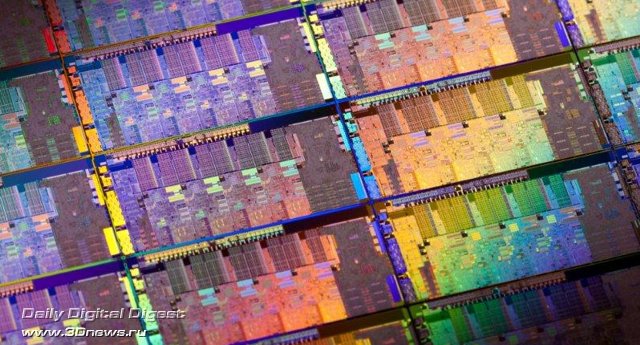

Несколько лет назад, во времена господства бренда Pentium, первого появления торговой марки Intel Core и одноимённой микроархитектуры (Architecture 101), на слайдах о будущих процессорах впервые было упомянуто следующее поколение микроархитектуры Intel с рабочим названием Gesher ("мост" на иврите), что чуть позже трансформировалось в Sandy Bridge.  В ту давнюю пору господства процессоров NetBurst, когда только-только начали проступать контуры грядущих ядер Nehalem, а мы знакомились с особенностями внутреннего строения первых представителей микроархитектуры Core - Conroe для настольных систем, Merom - для мобильных и Woodcrest - для серверных… Словом, когда трава была зелёная, а до Sandy Bridge было ещё как до Луны, уже тогда представители Intel говорили, что это будет совершенно новая процессорная микроархитектура. Именно так, cкажем, сегодня можно представить таинственную микроархитектуру Haswell, которая появится после поколения Ivy Bridge, которое, в свою очередь, придёт на смену Sandy Bridge в следующем году.  Однако чем ближе дата выпуска новой микроархитектуры, чем больше мы узнаём об её особенностях, тем больше становятся заметны сходства соседних поколений, и тем более очевиден эволюционный путь изменений в схемотехнике процессоров. И действительно, если между начальными реинкарнациями первой архитектуры Core - Merom/Conroe, и первенцем второго поколения Core – Sandy Bridge - на самом деле пролегает пропасть различий, то нынешняя последняя версия поколения Core - ядро Westmere - и грядущая, рассматриваемая сегодня первая версия поколения Core II - ядро Sandy Bridge, могут показаться схожими. И всё же различия существенны. Настолько существенны, что теперь окончательно можно говорить о конце 15-летней эпохи микроархитектуры P6 (Pentium Pro) и о появлении нового поколения микроархитектуры Intel. ⇡#Микроархитектура Sandy Bridge: с высоты птичьего полётаЧип Sandy Bridge – это четырёхъядерный 64-битный процессор с изменяемой (out-of-order) последовательностью исполнения команд, поддержкой двух потоков данных на ядро (HT), исполнением четырёх команд за такт; с интегрированным графическим ядром и интегрированным контроллером памяти DDR3; с новой кольцевой шиной, поддержкой 3- и 4-операндных (128/256-битных) векторных команд расширенного набора AVX (Advanced Vector Extensions); производство которого налажено на линиях с соблюдением норм современного 32-нм технологического процесса Intel.  Так, вкратце, одним предложением можно попробовать охарактеризовать новое поколение процессоров Intel Core II для мобильных и настольных систем, массовые поставки которых начнутся в самое ближайшее время.   Процессоры Intel Core II на базе микроархитектуры Sandy Bridge будут поставляться в новом 1155-контактном конструктиве LGA1155 под новые системные платы на чипсетах Intel 6 Series.

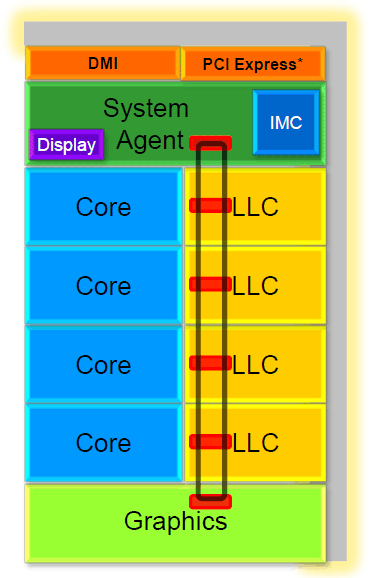

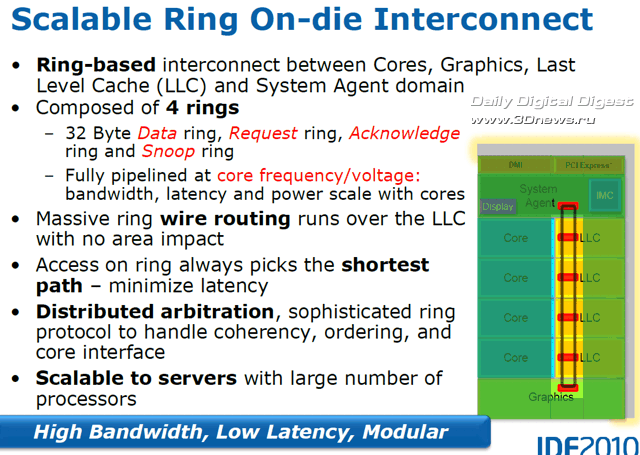

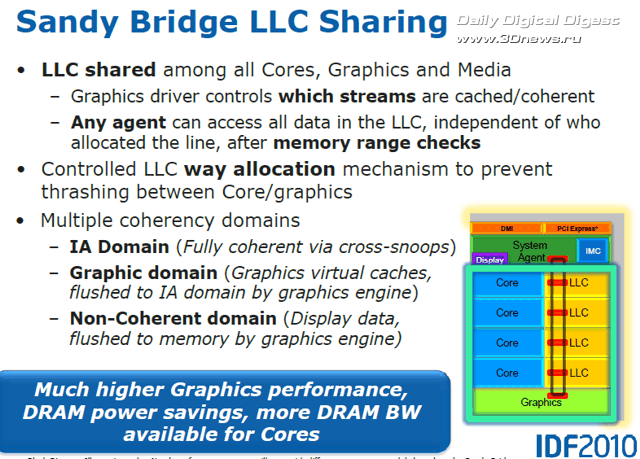

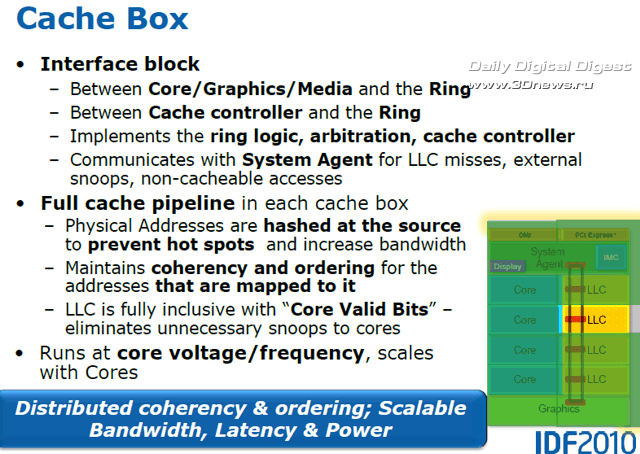

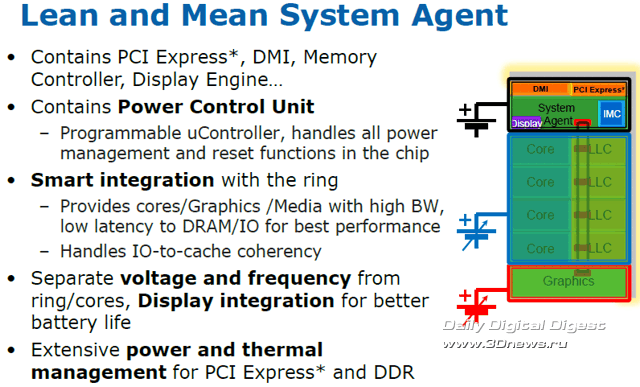

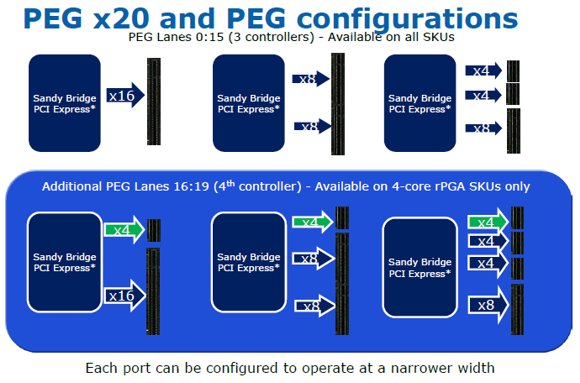

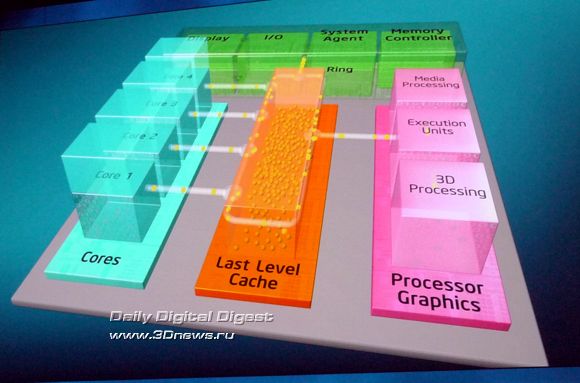

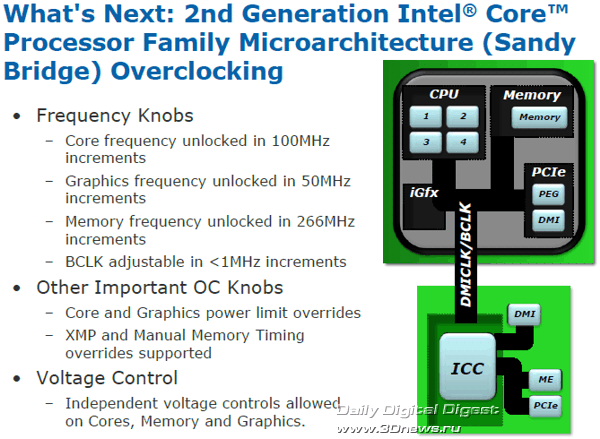

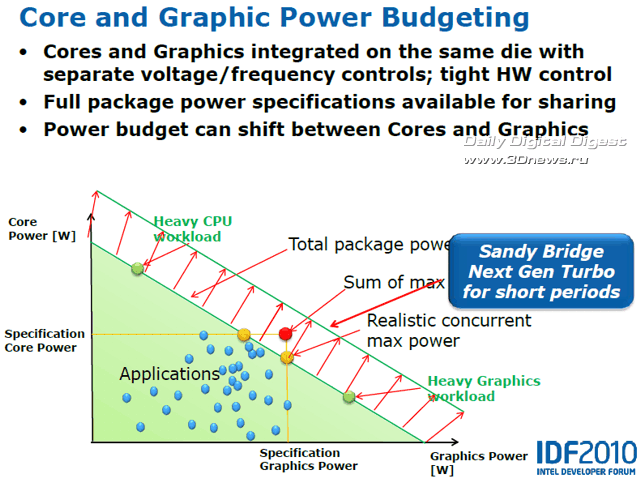

Примерно такая же микроархитектура будет актуальна и для серверных решений Intel Sandy Bridge-EP, разве что с актуальными отличиями в виде большего количества процессорных ядер (до восьми), соответствующего процессорного разъёма LGA2011, большего объёма кеша L3, увеличенного количества контроллеров памяти DDR3 и поддержкой PCI-Express 3.0.  Предыдущее поколение, микроархитектура Westmere в исполнении Arrandale и Clarkdale для мобильных и настольных систем, представляет собой конструкцию из двух кристаллов - 32-нм процессорного ядра и дополнительного 45-нм «сопроцессора» с графическим ядром и контроллером памяти на борту, размещённых на единой подложке и производящих обмен данными посредством шины QPI. По сути, на этом этапе инженеры Intel, используя преимущественно предыдущие наработки, создали этакую интегрированную гибридную микросхему. При создании архитектуры Sandy Bridge разработчики закончили начатый на этапе создания Arrandale/Clarkdale процесс интеграции и разместили все элементы на едином 32-нм кристалле, отказавшись при этом от классического вида шины QPI в пользу новой кольцевой шины. Суть микроархитектуры Sandy Bridge при этом осталась в рамках прежней идеологии Intel, которая делает ставку на увеличение суммарной производительности процессора за счёт улучшения «индивидуальной» эффективности каждого ядра.  Структуру чипа Sandy Bridge можно условно разделить на следующие основные элементы: процессорные ядра, графическое ядро, кеш-память L3 и так называемый «Системный агент» (System Agent). В общем и целом структура микроархитектуры Sandy Bridge понятна. Наша сегодняшняя задача – выяснить назначение и особенности реализации каждого из элементов этой структуры. ⇡#Кольцевая шина (Ring Interconnect)Вся история модернизации процессорных микроархитектур Intel последних лет неразрывно связана с последовательной интеграцией в единый кристалл всё большего количества модулей и функций, ранее располагавшихся вне процессора: в чипсете, на материнской плате и т.д. Соответственно, по мере увеличения производительности процессора и степени интеграции чипа, требования к пропускной способности внутренних межкомпонентных шин росли опережающими темпами. До поры до времени, даже после внедрения графического чипа в архитектуру чипов Arrandale/Clarkdale, удавалось обходиться межкомпонентными шинами с привычной перекрёстной топологией - этого было достаточно.  Однако эффективность такой топологии высока лишь при небольшом количестве компонентов, принимающих участие в обмене данными. В микроархитектуре Sandy Bridge для повышения общей производительности системы разработчики решили обратиться к кольцевой топологии 256-битной межкомпонентной шины, выполненной на основе новой версии технологии QPI (QuickPath Interconnect), расширенной, доработанной и впервые реализованной в архитектуре серверного чипа Nehalem-EX (Xeon 7500), а также планировавшейся к применению совместно с архитектурой чипов Larrabee. Кольцевая шина в версии архитектуры Sandy Bridge для настольных и мобильных систем (Core II) служит для обмена данными между шестью ключевыми компонентами чипа: четырьмя процессорными ядрами x86, графическим ядром, кешем L3 и системным агентом. Шина состоит из четырёх 32-байтных колец: шины данных (Data Ring), шины запросов (Request Ring), шины мониторинга состояния (Snoop Ring) и шины подтверждения (Acknowledge Ring), на практике это фактически позволяет делить доступ к 64-байтному интерфейсу кеша последнего уровня на два различных пакета. Управление шинами осуществляется с помощью коммуникационного протокола распределённого арбитража, при этом конвейерная обработка запросов происходит на тактовой частоте процессорных ядер, что придаёт архитектуре дополнительную гибкость при разгоне. Производительность кольцевой шины оценивается на уровне 96 Гбайт в секунду на соединение при тактовой частоте 3 ГГц, что фактически в четыре раза превышает показатели процессоров Intel предыдущего поколения. Кольцевая топология и организация шин обеспечивает минимальную латентность при обработке запросов, максимальную производительность и отличную масштабируемость технологии для версий чипов с различным количеством ядер и других компонентов. По словам представителей компании, в перспективе к кольцевой шине может быть "подключено" до 20 процессорных ядер на кристалл, и подобный редизайн, как вы понимаете, может производиться очень быстро, в виде гибкой и оперативной реакции на текущие потребности рынка. Кроме того, физически кольцевая шина располагается непосредственно над блоками кеш-памяти L3 в верхнем уровне металлизации, что упрощает разводку дизайна и позволяет сделать чип более компактным. L3 - кеш-память последнего уровня, LLC Как вы уже успели заметить, на слайдах Intel кеш-память L3 обозначается как «кеш последнего уровня», то есть, LLC - Last Level Cache. В микроархитектуре Sandy Bridge кеш L3 распределён не только между четырьмя процессорными ядрами, но, благодаря кольцевой шине, также между графическим ядром и системным агентом, в который, среди прочего, входит модуль аппаратного ускорения графики и блок видеовыхода. При этом специальный трассировочный механизм упреждает возникновение конфликтов доступа между процессорными ядрами и графикой.  Каждое из четырёх процессорных ядер имеет прямой доступ к «своему» сегменту кеша L3, при этом каждый сегмент кеша L3 предоставляет половину ширины своей шины для доступа кольцевой шины данных, при этом физическая адресация всех четырёх сегментов кеша обеспечивается единой хэш-функцией. Каждый сегмент кеша L3 обладает собственным независимым контроллером доступа к кольцевой шине, он отвечает за обработку запросов по размещению физических адресов. Кроме того, контроллер кеша постоянно взаимодействует с системным агентом на предмет неудачных обращений к L3, контроля межкомпонентного обмена данными и некешируемых обращений.  Дополнительные подробности о строении и особенностях функционирования кеш-памяти L3 процессоров Sandy Bridge будут появляться далее по тексту, в процессе знакомства с микроархитектурой, по мере возникновения необходимости. ⇡#Системный агент: контроллер памяти DDR3, PCU и другиеРанее вместо определения System Agent в терминологии Intel фигурировало так называемое «Неядро» - Uncore, то есть, «всё, что не входит в Core», а именно кеш L3, графика, контроллер памяти, другие контроллеры вроде PCI Express и т.д. Мы же по привычке частенько называли большую часть этого элементами северного моста, перенесённого из чипсета в процессор.  Системный агент микроархитектуры Sandy Bridge включает в себя контроллер памяти DDR3, модуль управления питанием (Power Control Unit, PCU), контроллеры PCI-Express 2.0, DMI, блок видеовыхода и пр. Как и все остальные элементы архитектуры, системный агент подключен в общую систему посредством высокопроизводительной кольцевой шины. Архитектура стандартной версии системного агента Sandy Bridge подразумевает наличие 16 линий шины PCI-E 2.0, которые также могут быть распределены на две шины шины PCI-E 2.0 по 8 линий, или на одну шину PCI-E 2.0 на 8 линий и две шины PCI-E 2.0 по четыре линии. Двухканальный контроллер памяти DDR3 отныне «вернулся» на кристалл (в чипах Clarkdale он располагался вне процессорного кристалла) и, скорее всего, теперь будет обеспечивать значительно меньшую латентность.  Тот факт, что контроллер памяти в Sandy Bridge стал двухканальным, вряд ли обрадует тех, кто уже успел вывалить немалые суммы за оверклокерские комплекты трёхканальной памяти DDR3. Что ж, бывает, теперь будут актуальны наборы лишь из одного, двух или четырёх модулей. По поводу возвращения к двухканальной схеме контроллера памяти у нас имеются кое-какие соображения. Возможно, в Intel начали подготовку микроархитектур к работе с памятью DDR4? Которая, из-за ухода от топологии «звезды» на топологию «точка-точка» в версиях для настольных и мобильных систем будут по определению только двухканальной (для серверов будут применяться специальные модули-мультиплексоры). Впрочем, это всего лишь догадки, для уверенных предположений пока что недостаточно информации о самом стандарте DDR4. Расположенный в системном агенте контроллер управления питанием отвечает за своевременное динамичное масштабирование напряжений питания и тактовых частот процессорных ядер, графического ядра, кешей, контроллера памяти и интерфейсов. Что особенно важно подчеркнуть, управление питанием и тактовой частотой производится независимо для процессорных ядер и графического ядра.  Совершенно новая версия технологии Turbo Boost реализована не в последнюю очередь благодаря этому контроллеру управления питанием. Дело в том, что, в зависимости от текущего состояния системы и сложности решаемой задачи, микроархитектура Sandy Bridge позволяет технологии Turbo Boost «разогнать» ядра процессора и встроенную графику до уровня, значительно превышающего TDP на достаточно долгое время. И действительно, почему бы не воспользоваться такой возможностью штатно, пока система охлаждения ещё холодная и может обеспечить больший теплоотвод, чем уже разогретая? Кроме того, что технология Turbo Boost позволяет теперь штатно «разгонять» все четыре ядра за пределы TDP, также стоит отметить, что управление производительностью и тепловым режимом графических ядер в чипах Arrandale/Clarkdale, по сути, только встроенных, но не до конца интегрированных в процессор, производилось с помощью драйвера. Теперь, в архитектуре Sandy Bridge, этот процесс также возложен на контроллер PCU. Такая плотная интеграция системы управления напряжением питания и частотами позволила реализовать на практике гораздо более агрессивные сценарии работы технологии Turbo Boost, когда и графика, и все четыре ядра процессора при необходимости и соблюдении определённых условий могут разом работать на повышенных тактовых частотах со значительным превышением TDP, но без каких-либо побочных последствий.  Принцип работы новой версии технологии Turbo Boost, реализованной в процессорах Sandy Bridge, отлично описывается в мультимедийной презентации, показанной в сентябре на Форуме Intel для разработчиков в Сан-Франциско. Представленный ниже видеоролик с записью этого момента презентации расскажет вам о Turbo Boost быстрее и лучше, чем любой пересказ.

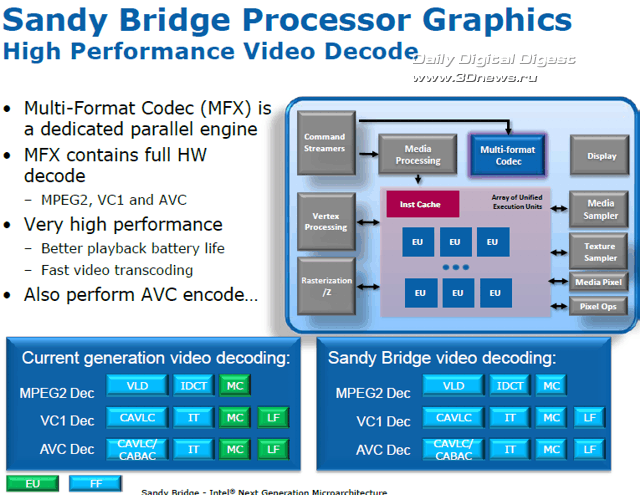

Насколько эффективно эта технология будет работать в серийных процессорах, нам ещё предстоит узнать, но то, что показывали специалисты Intel во время закрытой демонстрации возможностей Sandy Bridge в дни IDF в Сан Франциско, просто поражает: и прирост тактовой частоты, и, соответственно, производительность процессора и графики, одномоментно могут достичь просто фантастических уровней. Есть информация, что для штатных систем охлаждения режим такого «разгона» с помощью Turbo Boost и превышением TDP будет ограничен в BIOS периодом в 25 секунд. Но что если производители системных плат смогут гарантировать более качественный отвод тепла с помощью какой-нибудь экзотической системы охлаждения? Тут и открывается раздолье для оверклокеров…  Каждое из четырёх ядер Sandy Bridge может быть при необходимости независимо переведено в режим минимального энергопотребления, графическое ядро также можно перевести в очень экономичный режим. Кольцевая шина и кеш L3, в силу их распределения между другими ресурсами, не могут быть отключены, однако для кольцевой шины предусмотрен специальный экономичный ждущий режим, когда она не нагружена, а для кеш-памяти L3 применяется традиционная технология отключения неиспользуемых транзисторов, уже известная нам по предыдущим микроархитектурам. Таким образом, процессоры Sandy Bridge в составе мобильных ПК обеспечивают длительную автономную работу при питании от аккумулятора. Модули видеовыхода и мультимедийного аппаратного декодирования также входят в число элементов системного агента. В отличие от предшественников, где аппаратное декодирование было возложено на графическое ядро (о его возможностях мы поговорим в следующий раз), в новой архитектуре для декодирования мультимедийных потоков используется отдельный, гораздо более производительный и экономичный модуль, и лишь в процессе кодирования (сжатия) мультимедийных данных используются возможности шейдерных блоков графического ядра и кеш L3.  В соответствии с современными веяниями, предусмотрены инструменты воспроизведения 3D-контента: аппаратный модуль декодирования Sandy Bridge способен без труда обрабатывать сразу два независимых потока MPEG2, VC1 или AVC в разрешении Full HD. Сегодня мы познакомились со структурой нового поколения микроархитектуры Intel Core II с рабочим названием Sandy Bridge, разобрались со строением и принципом работы ряда ключевых элементов этой системы: кольцевой шины, кеш-памяти L3 и системного агента, в состав которого входит контроллер памяти DDR3, модуль управления питанием и другие компоненты. Однако это лишь малая часть новых технологий и идей, реализованных в микроархитектуре Sandy Bridge, не менее впечатляющие и масштабные изменения коснулись архитектуры процессорных ядер и интегрированной графической системы. Так что на этом наш рассказ о Sandy Bridge не заканчивается - продолжение следует.  ⇡#Ссылки по теме:

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|