|

Опрос

|

реклама

Быстрый переход

Microsoft заказала у Intel Foundry производство процессоров по техпроцессу Intel 18A

22.02.2024 [00:12],

Андрей Созинов

Компания Intel Foundry, подразделение Intel по контрактному производству чипов, сообщила о получении крупного заказа от Microsoft. В рамках мероприятия IFS Direct, посвящённого бизнесу Intel по контрактному производству чипов, было объявлено о том, что Microsoft выбрала технологический процесс Intel 18A (класс 1,8 нм) для производства своих кастомных процессоров следующего поколения.  «Мы находимся в самом разгаре захватывающей смены платформы, которая коренным образом изменит производительность каждой отдельной организации и всей отрасли, — сказал генеральный директор Microsoft Сатья Наделла (Satya Nadella). — Для достижения этой цели нам необходимы надежные поставки самых современных, высокопроизводительных и высококачественных полупроводников. Вот почему мы так рады сотрудничеству с Intel Foundry и почему мы выбрали дизайн чипа, который планируем производить по техпроцессу Intel 18A». Вероятно, речь идет либо о одном процессоре, который будет выпускаться огромной серией и внедряться в течение нескольких лет, либо о серии продуктов, основанных на технологическом процессе Intel 18A. Напомним, что данный техпроцесс подразумевает использование GAA-транзисторов RibbonFET и технологии подачи питания на обратную сторону кристалла Intel PowerVia. К настоящему времени Intel Foundry заключила контракты на выпуск чипов с несколькими известными компаниями, включая Amazon Web Services. Компания Intel получила несколько заказов на процессоры для центров обработки данных, включая чип для облачного ЦОД на базе Intel 3, кастомный серверный чип для Ericsson и различные чипы на базе Intel 18A для Министерства обороны США. Ни Intel, ни Microsoft не сообщили, когда Intel начнет производство процессоров на базе 18A для Microsoft и когда эти чипы начнут применяться. По прогнозам, Intel 18A будет готов к массовому производству во второй половине 2024 года, так что теоретически мы можем увидеть чипы Microsoft на базе 18A уже совсем скоро. Intel будет сдавать в аренду оборудование и производственные площадки другим производителям чипов

21.02.2024 [12:19],

Алексей Разин

Завтра в Калифорнии пройдёт мероприятие IFS Direct Connect 2024, с трибуны которого Intel расскажет о своих успехах и планах в сфере контрактного производства чипов. Старший вице-президент и руководитель Intel Foundry Service Стюарт Панн (Stuart Pann) в обширном интервью ресурсу Tom’s Hardware рассказал о текущих приоритетах компании в этой сфере.

Источник изображения: Intel Прежде всего, он дал понять, что концентрация контрактных клиентов для техпроцесса Intel 18A была заложена изначально и оправдывается экономически. Средства разработки компонентов в сотрудничестве с Cadence и Synopsys компания Intel оптимизировала таким образом, чтобы клиентам было проще разрабатывать свои чипы, которые она будет для них выпускать по так называемому ангстремному техпроцессу Intel 18A. В рамках этой технологии, помимо прочего, компания собирается реализовать подводку питания с обратной стороны кремниевой пластины, рассчитывая опередить конкурирующих TSMC и Samsung. Концентрация на передовых и более дорогих техпроцессах позволит Intel быстрее окупить свои вложения на расширение производственных мощностей и ускоренное освоение передовой литографии, хотя в ассортименте предложений этого производителя останутся и услуги, связанные с более зрелыми технологиями. К 2030 году, как напомнил Стюарт Панн, компания Intel рассчитывает стать вторым по величине контрактным производителем чипов в мире. Возможность эффективно использовать уже окупившие себя оборудование и помещения является одним из условий развития контрактного бизнеса. Например, сотрудничество с компаниями Tower Semiconductor и UMC как раз подразумевает, что Intel передаст в использование партнёрам предприятия и оборудование, которые себя уже окупили, но могут приносить дополнительный доход вне сферы прямых интересов Intel. Компании Tower и UMC получат производственные площадки в США, они будут платить Intel за их использование. Та же UMC, например, получит от Intel оборудование, на котором можно выпускать чипы по 14-нм и 10-нм технологиям, но располагаться оно будет в помещениях, которые не подходят для установки современного оборудования для работы с EUV-литографией. Здания в итоге не будут простаивать и начнут приносить Intel доход, хотя напрямую ей самой и не понадобятся. Услуги по упаковке чипов Intel будет оказывать сторонним клиентам и в Малайзии, и на будущем предприятии в Польше, но некоторым из них приглянутся именно предприятия в Нью-Мексико, Орегоне и Аризоне. В последнем случае клиенты смогут использовать компоненты, выпускаемые Intel по технологии 18A, и при этом не отправлять их для тестирования и упаковки за пределы США, а получать полностью обработанное на территории страны изделие. Для кого-то такая самодостаточность будет очень важна. Intel не скрывает заинтересованности оборонных заказчиков из США в её передовых техпроцессах, но в силу специфики подобной продукции распространяться о ней не будет. Для клиентов из оборонной сферы компания на этой неделе проведёт закрытое отдельное мероприятие. Будет ли Intel упаковывать чипы по заказу NVIDIA, представитель первой из компаний пояснять не стал. Клиенты просят сохранять конфиденциальность, и даже если бы речь шла об NVIDIA, никаких исключений из правил не возникло бы. Стюарт Панн лишь дал понять, что до него дошли распространяемые прессой слухи о возможности тесного сотрудничества NVIDIA и Intel. Зато старший вице-президент компании пояснил, что если кому-то из клиентов потребуется адаптировать техпроцесс под свои конкретные нужды, Intel ему в этом не откажет. Возрастающей конкуренции со стороны китайских производителей чипов по зрелым технологиям Intel тоже не боится, по словам Панна — просто по той причине, что они находятся в Китае, а Intel сможет предложить американским клиентам чипы местного производства на вполне привлекательных условиях. При этом Панн подчеркнул, что конкурировать с китайцами на китайском рынке у Intel вряд ли бы вышло. Samsung поможет Arm оптимизировать ядра Cortex под 2-нм техпроцесс

21.02.2024 [08:12],

Алексей Разин

Южнокорейская компания Samsung Electronics не оставляет попыток опередить конкурирующую TSMC на рынке услуг по контрактному производству чипов если не по количеству клиентов, то хотя бы по срокам внедрения новых литографических норм. Сотрудничество с Arm призвано облегчить клиентам последней разработку процессоров, которые Samsung сможет выпускать по 2-нм техпроцессу.

Источник изображения: Samsung Electronics Инициатива Arm и Samsung, как поясняет TechPowerUp, направлена на широкий ассортимент рыночных решений, от серверных процессоров и ускорителей искусственного интеллекта до мобильных компонентов, включая и компоновочные варианты с чиплетами. В результате плодотворного взаимодействия Arm и Samsung клиентам обеих компаний будет проще поставить на конвейер последней процессоры с архитектурами Cortex-X и Cortex-A, которые создавались с расчётом на выпуск по 2-нм технологии корейского подрядчика. Напомним, что структуру транзисторов MBCFET компания Samsung использовала уже в рамках 3-нм технологии, поэтому внедрение транзисторов с окружающим затвором (GAA) в рамках 2-нм техпроцесса будет для неё не столь рискованным. Arm сотрудничает в этой сфере и с другими контрактными производителями. Не так давно, например, стало известно о вовлечении компании в подготовку к производству 64-ядерных процессоров Faraday Technology с архитектурой Arm Neoverse по техпроцессу Intel 18A одноимённой компании. В целом, Arm уже сотрудничала с Intel в рамках данной технологии и при создании необходимой разработчикам экосистемы ранее, соответствующее заявление было сделано компаниями в апреле прошлого года. Появление подобного альянса с Samsung является закономерным шагом Arm по созданию условий для разработчиков процессоров, желающих выпускать свою продукцию по передовым технологиям в исполнении ведущих контрактных производителей. Intel претендует на получение более чем $10 млрд правительственных субсидий в США

17.02.2024 [06:22],

Алексей Разин

До конца марта министр торговли США Джина Раймондо (Gina Raimondo) рассчитывает назвать нескольких крупных получателей субсидий на строительство предприятий по выпуску чипов, согласно принятому в 2022 году «Закону о чипах». По данным агентства Bloomberg, корпорация Intel претендует на получение более чем $10 млрд из этих средств.

Источник изображения: Applied Materials По информации осведомлённых источников, правительственная поддержка Intel будет в какой-то пропорции поделена между прямыми субсидиями и ссудами. Совокупный объём первых, напомним, достигнет $39 млрд, а в форме возвратных средств власти США готовы выделить до $75 млрд. До сих пор столь крупных субсидий, как в случае с Intel, американские власти ещё не согласовывали. Проекты в Нью-Гемпшире, Орегоне и Колорадо с участием компаний BAE Systems и Microchip Technology оперировали куда меньшими бюджетами. Надо сказать, что и $10 млрд для Intel не кажутся столь существенной поддержкой, с учётом готовности компании вложить $20 млрд в строительство двух предприятий в Орегоне, ещё $20 млрд в модернизацию и расширение предприятий в Аризоне, а также $3,5 млрд на проект в Нью-Мексико. В прессе уже появлялись слухи о намерениях Intel задержать запуск предприятий в Огайо до 2026 года из-за отсрочки выделения субсидий, но источники из числа местных чиновников пояснили, что график реализации проекта зависит от рыночных условий, а не сроков выделения субсидий. По их словам, всё пока остаётся в пределах первоначальных рамок, предложенных Intel. За время нахождения президента Байдена у власти в США производители чипов вложили в местную экономику более $230 млрд. По замыслу администрации президента, в стране до 2030 года должны появиться как минимум два кластера по производству чипов с использованием передовых технологий. Руководство Intel в своих рассуждениях не раз поясняло, что при реализации новых проектов оно рассчитывает до 20–30 % затрат на строительство предприятий покрывать за счёт субсидий. Судя по имеющемуся бюджету, компания попытается выдержать эту пропорцию. Автоматический разгон до 6,2 ГГц и энергопотребление 410 Вт — Intel готовит отборный чип Core i9-14900KS

15.02.2024 [16:17],

Николай Хижняк

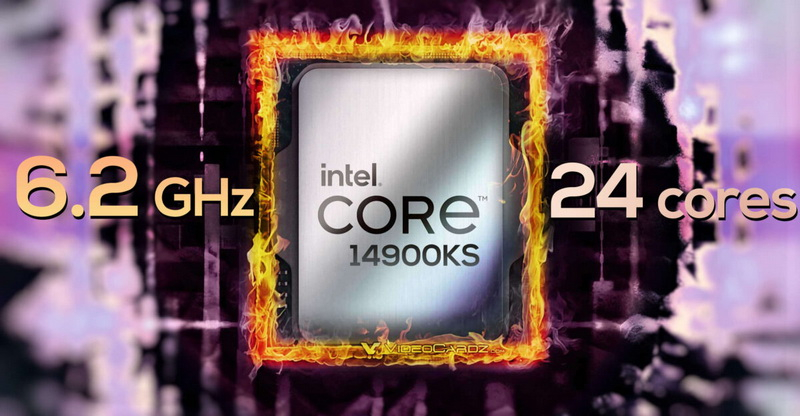

Компания Intel готовит к выпуску отборный флагманский процессор Core i9-14900KS, способный автоматически разгоняться до частоты 6,2 ГГц. Согласно утечкам, чип может потреблять более 400 Вт мощности при пиковой нагрузке. В продаже новинка ожидается в марте.

Источник изображения: VideoCardz Если верить имеющимся данным, Intel Core i9-14900KS станет первым потребительским процессором, способным в автоматическом режиме работать на частоте выше 6 ГГц. Актуальный флагманский процессор Core i9-14900K из серии Raptor Lake Refresh работает на частоте до 6 ГГц включительно. Такой же возможностью обладает выпущенный до него отборный Core i9-13900KS серии Raptor Lake. Предполагается, что Core i9-14900KS станет последним процессором платформы LGA 1700. Будущие настольные процессоры серии Arrow Lake-S будут предназначены для новой платформы LGA 1851. Пару дней назад в Сети появились спецификации Core i9-14900KS. Информация была обнаружена в базе данных стресс-теста OCCT. В ней говорится, что Core i9-14900KS имеет 24 ядра с поддержкой 32 виртуальных потоков (8 P-ядер и 16 E-ядер). Чип получил 36 Мбайт кеш-памяти L3 и 32 Мбайт кеш-памяти L2. Базовая частота процессора составляет 3,2 ГГц, а Boost-частота установлена на 6,2 ГГц, что делает его самым быстрым процессором в мире, по крайней мере по показателю тактовой частоты, «из коробки». Номинальный показатель TDP новинки составляет 150 Вт, что на 25 Вт выше, чем у Core i9-14900K. Core i9-14900KS разработан специально для энтузиастов и в продажу поступит в ограниченном количестве. Данные о тестах процессора в бенчмарке OCCT показывают, что в моменты пиковой нагрузки его энергопотребление составляет почти 410 Вт, а температура превышает 100 градусов Цельсия. Следует учитывать, что речь идёт об очень серьёзном стресс-тесте, который максимально нагружает CPU. Тем не менее, для Core i9-14900KS в любом случае потребуется очень мощная система охлаждения — лучше смотреть в сторону СЖО с радиатором типоразмера 420 мм или кастомных решений. Также с учётом высокой мощности процессору потребуется соответствующий блок питания. Для дополнительного разгона Core i9-14900KS, весьма вероятно, потребуется более экстремальный подход к охлаждению, например, с использованием жидкого азота. Поскольку чип будет проходить строгий бининг (отбор), новинка, скорее всего, привлечёт внимание энтузиастов, которые попытаются с его помощью установить новые рекорды разгона, побив результаты Core i9-14900K. От последнего оверклокеры добились работы на частоте 9,1 ГГц, от Core i9-14900KS можно ожидать чуть более высоких показателей. Возможно, процессор можно будет разогнать до 9,5 или даже 10 ГГц. Согласно информации инсайдера Benchlife, Core i9-14900KS появится в продаже где-то в середине марта. Стоимость Core i9-14900KS неизвестна. Однако предполагается, что она будет примерно такой же, как у Core i9-13900KS, чья рекомендованная стоимость составляет $700. Intel Lunar Lake получат технологию повышения резкости для своей встроенной графики Xe2

15.02.2024 [04:39],

Николай Хижняк

Intel ведёт разработку технологии улучшения графики в играх, которая будет использоваться встроенным графическим ядром будущих процессоров Lunar Lake, а также видеокартами на основе будущих архитектур Xe. Речь идёт об адаптивном фильтре изменения резкости изображения.

Источник изображения: VideoCardz Адаптивный фильтр резкости изображения в целом работает как обычный, использующийся сегодня в играх для повышения чёткости изображения. Однако он будет более интеллектуальным. Технология сможет повышать чёткость не для всего кадра игры в целом, а лишь в отдельных его областях (например, персонажи в кадре), избегая повышения резкости в областях изображения, где не требуется применение этого фильтра (например, задний фон). Как отметила инженер Intel Немеса Гарг (Nemesa Garg), новую технологию адаптивного фильтра резкости можно будет использовать не только в играх, но и в программах, а также для видео внутри операционной системы.

Источник изображения: Intel За работу адаптивного фильтра резкости будет отвечать аппаратный блок Display Engine. Технология предназначена для работы на архитектуре графического ядра процессоров Lunar Lake и любых будущих версий графической архитектуры Xe. Фильтр имеет минимальные требования к энергопотреблению и практически не оказывает никакого влияния на производительность, что важно для Lunar Lake, поскольку речь идёт об энергоэффективных мобильных чипах. Intel не сообщила точной информации о том, когда представит процессоры Lunar Lake. Но это практически наверняка случится во второй половине этого года. Указанные чипы появятся одновременно с настольными и мобильными процессорами Arrow Lake. И если в последних будет использоваться графическая архитектура Xe-LPG, то в Lunar Lake будет реализована более передовая графика Xe2-LPG. TSMC стала крупнейшим производителем чипов в мире, оставив позади Intel и Samsung

07.02.2024 [18:41],

Павел Котов

Имеющиеся в распоряжении TSMC производственные мощности и передовые технологии сделали компанию крупнейшим в мире производителем чипов по объёму выручки. Благодаря своему опыту в области передовых технологий производства чипов, которых нет у конкурентов, тайваньская компания, вероятно, сумеет удержать первое место на рынке.

Источник изображения: TSMC TSMC по итогам 2023 года впервые в истории стала крупнейшим в мире производителем полупроводников по объёму выручки — компания заработала $69,3 млрд, что выше показателей полупроводниковых подразделений Intel ($54,23 млрд) и Samsung ($50,99 млрд). Этот результат отражает сдвиг в отрасли, где традиционно доминировала Intel — «синие» удерживали первое место по доходам от выпуска чипов несколько десятилетий, начиная с 1992 года, за исключением 2017 года, когда лидером ненадолго стала Samsung. Тайваньский контрактный производитель не выпускает процессоров под собственной маркой, но его производственные услуги незаменимы для других чипмейкеров. Рост TSMC оказался устойчивым, поскольку компания обслуживает таких клиентов как Apple, AMD, NVIDIA и Qualcomm. В эпоху пандемии, когда мировая потребность в электронике резко возросла, TSMC установила надбавку за свои услуги. Компания доминирует в области технологических процессов, что даёт ей крепкие позиции на переговорах. Следом за TSMC на рынке полупроводников по объёму выручки окажется NVIDIA, которая имеет все шансы превзойти Samsung и Intel по итогам 2023 года. Компания представит отчёт 21 февраля, но, по предварительным оценкам, речь идёт о сумме в $58,8 млрд за календарный год. Обычно TSMC не упоминалась среди крупнейших полупроводниковых компаний, поскольку это исключительно контрактный производитель, но сейчас её выручка оказалась выше дохода Intel и Samsung. По итогам IV квартала 2023 года тайваньский гигант также обошёл ближайших конкурентов, показав $19,55 млрд против $16,42 млрд у Samsung и $15,41 млрд у Intel. TSMC также объявила о намерении открыть в Японии второй завод по производству чипов совместно с Sony и Toyota — он начнёт работать в конце 2027 года в рамках совместного предприятия Japan Advanced Semiconductor Manufacturing, контрольный пакет акций которого принадлежит тайваньской стороне. Суммарный объём инвестиций TSMC в Японии превысит $20 млрд, если учесть завод, который начнёт работать в этом году. Новые заводы в стране будут производить не передовые логические чипы, а займутся выпуском продукции для автомобилей, промышленности и высокопроизводительных вычислений. Протестирована СЖО для скальпированных процессоров Intel — нагрев снизился более чем на 20 °С

05.02.2024 [23:03],

Андрей Созинов

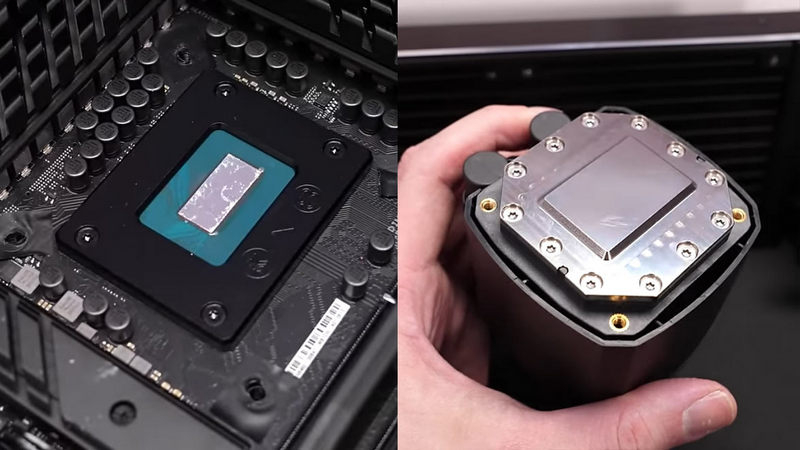

Известный энтузиаст разгона Роман «Der8auer» Хартуг (Roman Hartung) протестировал прототип системы жидкостного охлаждения EK-Nucleus AIO CR360 Direct Die D-RGB, которая предназначена для охлаждения скальпированных процессоров Intel в исполнении LGA 1700. И хотя это всего лишь прототип, полученные результаты оказались весьма впечатляющими.

Источник изображений: der8auer Как известно, если снять с процессора металлическую крышку, то можно не только лишиться гарантии (и какого-то количества нервных клеток), но и обеспечить гораздо более эффективное охлаждение. Специально для энтузиастов, предпочитающих скальпированные чипы, компания EKWB готовит СЖО, которая без доработки сможет использоваться с такими чипами. Пока она доступна для предварительного заказа. Der8auer поясняет, что EK-Nucleus AIO CR360 Direct Die D-RGB AiO — это необычный продукт, поскольку он предназначен исключительно для систем со скальпированными настольными процессорами Intel Core 12-го, 13-го и 14-го поколений. EK разработала специальное основание водоблока с выступающей частью в центре, чтобы оно наилучшим образом контактировало с кристаллом скальпированного процессора. Также в комплект поставки СЖО будет включена специальная монтажная пластина, которая в сочетании с комплектной тыльной усиливающей пластиной заменит стандартную прижимную рамку сокета.  Энтузиаст отметил, что в будущем он сравнит кулер EK-Nucleus AIO CR360 Direct Die D-RGB AiO с лучшими кастомными системами жидкостного охлаждения, но сейчас он хочет установить базовый уровень, чтобы дать зрителям представление о предлагаемом потенциале новинки. На диаграмме ниже сравниваются температуры процессора с воздушным кулером Corsair A115 и с прототипом СЖО от EK. Оба охладителя были установлены на скальпированный Core i9 -13900KS, на котором запускался тест Cinebench R23 для создания нагрузки. Для установки Corsair A115 дополнительно применялся прототип медной процессорной крышки Thermal Grizzly вместо стандартной. По словам Der8auer, данная крышка даёт выигрыш в 6-8 °С по сравнению со стандартной. График показывает значительное преимущество кулера EK-Nucleus AIO CR360 Direct Die D-RGB AiO. СЖО обеспечил до 15 °С более низкую температуру. Если верить заявлениям энтузиаста о свойствах кастомной крышки, со стандартным процессором разница в температуре достигла бы 20 °С или даже выше. Что касается производительности, то процессор с воздушным охлаждением показал около 38 300 баллов в Cinebench R23, а чип с жидкостных охлаждением — чуть более 39 100 баллов. Частота процессора была более стабильной и составляла 5,6 ГГц при использовании AiO, тогда как при использовании воздушного кулера она часто падала до 5,4 ГГц. Пожалуй, минусом для системы охлаждения EK-Nucleus AIO CR360 Direct Die D-RGB AiO является то, что выходит она к закату эры LGA 1700. Der8auer признался, что не знает, что нужно будет сделать, чтобы обеспечить совместимость новинки с процессорами Intel Core 15-го поколения. EK-Nucleus AIO CR360 Direct Die D-RGB доступна для предварительного заказа в Европе по цене 200 евро. Продажи должны начаться к концу марта. Intel будет производить серверные процессоры на ядрах Arm Neoverse по 18-ангстремному техпроцессу

05.02.2024 [21:29],

Андрей Созинов

Контрактный разработчик микросхем Faraday Technology в понедельник объявил о планах по созданию одного из первых в мире 64-ядерных процессоров на базе Arm Neoverse. Выпуском новинки займётся подразделение контрактного производства компании Intel по передовому технологическому процессу 18A (1,8 нм).  Новая однокристальная платформа (system-on-chip — SoC) с 64 ядрами Arm Neoverse будет предназначена для широкого спектра приложений, включая крупные центры обработки данных, периферийные системы и передовые сети 5G, утверждает Faraday. Разработчик чипов сообщил, что в новинке также будут использоваться различные интерфейсные IP из экосистемы Arm Total Design, но не раскрыл, какие именно. Логично ожидать, что процессор будет оснащен интерфейсами PCIe, CXL и DDR5. Стоит отметить, что Faraday не будет продавать сам процессор, а предложит дизайн чипа своим клиентам, которые смогут адаптировать его под свои нужды. Пока неясно, есть ли у Faraday потенциальный заказчик, но, похоже, компания уверена в ядрах Arm Neoverse. Эти процессоры будут производиться Intel Foundry Services (IFS) по техпроцессу Intel 18A и, вероятно, станут одними из первых серверных Arm-процессоров, выпущенных IFS. На данный момент Intel Foundry Services собрала несколько заказов на чипы для центров обработки данных. Это чип для облачных систем для техпроцесса Intel 3, кастомный серверный чип для Ericsson и чипы на базе Intel 18A для Министерства обороны США. Кроме того, Intel собирает «системы в корпусе» (system-in-package) для центров обработки данных Amazon Web Services. «Как партнер по проектированию в рамках Arm Total Design, Faraday стратегически нацелена на самые передовые технологические узлы, чтобы удовлетворить растущие потребности будущих приложений, — сказал Стив Ванг (Steve Wang), генеральный директор Faraday. — Мы рады объявить о разработке нашей новой SoC-платформы на базе Arm Neoverse с использованием технологии Intel 18A. Это решение принесет пользу нашим заказчикам ASIC и DIS (Design Implementation Service), позволяя им ускорить время выхода на рынок передовых приложений для центров обработки данных и высокопроизводительных вычислений». «Мы рады сотрудничать с Faraday в разработке SoC на базе Arm Neoverse с использованием нашего самого конкурентоспособного технологического процесса Intel 18A, — сказал Стюарт Панн (Stuart Pann), старший вице-президент Intel и генеральный менеджер подразделения Intel Foundry Services (IFS). — Наше стратегическое сотрудничество с Faraday демонстрирует наше стремление к внедрению технологических и производственных инноваций в глобальную цепочку поставок полупроводников, помогая клиентам Faraday без труда соответствовать мировым стандартам мощности и производительности для SoC». Примечательно, что Intel Foundry Services и Arm объявили о сотрудничестве в области мобильных однокристальных платформ, которые будут производиться по технологии Intel 18A, ещё в апреле 2023 года. Пока это соглашение не принесло плодов, но, как выяснилось, по крайней мере один контрактный разработчик чипов заинтересован в том, чтобы выйти на рынок центров обработки данных с Arm Neoverse и Intel 18A. AMD сделала ставку на ПК с ИИ в гонке с Intel и NVIDIA за рынок компьютеров

02.02.2024 [19:00],

Сергей Сурабекянц

Американский полупроводниковый гигант Advanced Micro Devices делает ставку на компьютеры с искусственным интеллектом, которые смогут конкурировать с NVIDIA и Intel. «Рынок компьютеров с искусственным интеллектом будет продолжать расширяться», — заявил президент AMD Виктор Пэн (Victor Peng). Он ожидает бурного внедрения персональных компьютеров с ИИ во второй половине года.

Источник изображения: AMD «Мы видим, что компьютеры с искусственным интеллектом становятся все более важным фактором, и благодаря недавним анонсам мы имеем хорошее преимущество в области ПК с искусственным интеллектом… Я думаю, что мы занимаем чрезвычайно хорошие позиции как в области ИИ, так и в других традиционных сферах бизнеса», — считает Пэн. В прошлом месяце AMD анонсировала гибридные процессоры (APU) для настольных ПК серии Ryzen 8000G от которых пользователи могут «ожидать огромную мощность и превосходную производительность для интенсивных рабочих нагрузок, включая игры и создание контента». Чипы предназначаются для материнских плат с Socket AM5 и это первые APU для данной платформы. Новинки оснащены вычислительными ядрами с архитектурой Zen 4, графическими ядрами на архитектуре RDNA 3 и улучшенным ИИ-движком Ryzen AI (XDNA1).

Источник изображения: AMD AMD конкурирует с NVIDIA и Intel в области графических процессоров, которые важны для ИИ и высокопроизводительных вычислений. В декабре 2023 года AMD выпустила новые ускорители Instinct MI300X на базе графических процессоров, предназначенные для обучения больших языковых моделей, которые должны конкурировать с чипами NVIDIA H100. «ИИ — это не только графические процессоры для центров обработки данных, но и серверы, и в прошлом году мы получили значительную долю рынка. Что касается серверов, мы ожидаем, что с MI300 мы продолжим завоёвывать долю рынка», — сказал Пэн.

Источник изображения: AMD Во время финансового отчёта за четвёртый квартал исполнительный вице-президент AMD Жан Ху (Jean Hu) сообщил: «Мы добились роста выручки в годовом исчислении в сегментах наших центров обработки данных и встраиваемых систем, а также успешно запустили ускорители AMD Instinct MI300, что позволяет нам уверенно наращивать продажи продукции в этом сегменте в 2024 году». NVIDIA в настоящее время доминирует на рынке графических процессоров для ускорителей, используемых в приложениях ИИ. Большинство моделей генеративного ИИ сейчас используют графические процессоры NVIDIA, такие как H100. В начале января компания анонсировала новые видеокарты GeForce RTX 4000 Super, которые помимо прочего предназначены для запуска приложений генеративного ИИ на ПК.

Источник изображения: NVIDIA В декабре Intel выпустила мобильные процессоры Core Ultra c поддержкой ИИ. По словам компании, эти процессоры будут использованы в «более чем 230 первых в мире ПК с искусственным интеллектом от таких компаний, как Acer, ASUS, Dell, HP и Lenovo».

Источник изображения: Intel Президент и главный исполнительный директор HP Энрике Лорес (Enrique Lores) заявил в ноябре, что компания «действительно воодушевлена тем влиянием, которое компьютеры с искусственным интеллектом окажут на общую категорию ПК», но «потребуется некоторое время», прежде чем они станут достаточно широко распространены. Исследовательская компания Canalys в декабрьском отчёте отметила, что бум генеративного ИИ приведёт к увеличению продаж ПК, поскольку потребители активно интересуются такими устройствами. Взрыв интереса к ИИ был вызван запуском чат-бота ChatGPT в ноябре 2022 года, мгновенно ставшего вирусным. По прогнозу Canalys, 60 % компьютеров, проданных в 2027 году, будут поддерживать ускорение ИИ-алгоритмов. По данным исследовательской компании International Data Corporation, первоначально устройства на базе ИИ будут нацелены на некоторые сегменты рынка корпоративных ПК, но большее количество вариантов использования и снижение затрат могут со временем распространить их внедрение на более широкий пользовательский рынок. IDC ожидает, что интеграция возможностей искусственного интеллекта в ПК послужит катализатором обновлений, которые появятся на прилавках в этом году. Intel запустит производство ангстремных чипов в Огайо на два года позже из-за задержки субсидий

02.02.2024 [11:45],

Алексей Разин

Создание предприятий по выпуску передовых чипов в США затягивается. Не так давно TSMC признала, что не укладывается в первоначальный график строительства двух предприятий в штате Аризона. Теперь слухи приписывают проекту Intel по строительству двух предприятий в Огайо аналогичные проблемы. Сообщается, что данная площадка сможет начать выдавать продукцию только в 2027 году, поскольку вопрос с выделением субсидий до сих пор не решён.

Источник изображения: Intel Корпорация Intel на квартальной конференции не без гордости отмечала, что по итогам прошлого года смогла добиться сокращения расходов на $3 млрд, но ближайшие годы для неё в любом случае будут не самым простым периодом, поскольку производителю приходится не только вкладываться в новые предприятия, но и навёрстывать упущенное в сфере техпроцессов. В данном вопросе Intel изначально полагалась на субсидии государства, которые при строительстве новых предприятий призваны были покрывать до 30 % затрат компании. Проект по строительству двух предприятий Intel в штате Огайо изначально предусматривал расходы в размере $20 млрд, поэтому и сумма субсидий в идеальном для компании варианте должна была бы измеряться миллиардами долларов США. Два предприятия в Огайо, по замыслу Intel, должны были начать выпуск чипов уже в 2025 году, но издание The Wall Street Journal со ссылкой на осведомлённые источники сообщает, что сроки смещаются до конца 2026 года, и это только применительно к завершению строительства. Ещё какое-то время уйдёт на монтаж оборудования, и это гарантированно сместит дату начала выпуска чипов на 2027 год как минимум. Представители Intel данную ситуацию прокомментировали лишь скупой формулировкой о том, что «управление большими проектами часто подразумевает адаптацию под изменяющиеся сроки», но подчеркнули, что отказываться от своих намерений производитель не собирается. Компания изначально сильно зависела от государственных субсидий в своих планах по строительству предприятий в Огайо. Сейчас на площадке в этом штате задействовано около 800 специалистов в области строительства, в перспективе их штат может быть увеличен до 7000 человек. В дальнейшем компания рассчитывала развивать данную площадку и вложить в это до $100 млрд. Власти штата Огайо в отдельности рассчитывали выделить Intel до $600 млн, в расчёте на появление около 3000 рабочих мест на будущих предприятиях компании. Стоит отметить, что реализация проектов Intel на территории Орегона, Аризоны и Нью-Мексико продвигалась хоть и не без проблем, но однозначно в сторону выполнения намеченных планов. Другой проблемой для Intel может стать зависимость от проекта в Огайо с точки зрения сроков освоения передового техпроцесса Intel 18A, который должен быть внедрён именно на этих предприятиях. Сейчас профильное оборудование эксплуатируется в Орегоне и там же осуществляется выпуск тестовых чипов и прототипов. Возможно, в случае задержки с проектом в Огайо именно Орегон станет местом серийного производства самых передовых изделий Intel. Это должно случиться уже в следующем году. Япония профинансирует разработки Intel, SK hynix и NTT в сфере кремниевой фотоники

30.01.2024 [15:46],

Алексей Разин

Корпорация Intel давно занимается проблемой сращивания полупроводниковых решений для передачи информации с оптоволоконными каналами, эта сфера получила обозначение «кремниевой фотоники». Японское правительство готово субсидировать совместные изыскания оператора связи NTT, компаний Intel и SK hynix в данной сфере, выделяя на это $305 млн бюджетных средств.

Источник изображения: Intel Агентство Nikkei сообщило о принятом властями Японии решении сегодня. Кремниевая фотоника обещает не только повысить скорость передачи информации, но снизить энергозатраты на обеспечение этого процесса. Министерство экономики, торговли и промышленности Японии выражает надежду, что за счёт прорыва на этом направлении страна сможет получить преимущество на международном рынке и возродить свою полупроводниковую промышленность. В свете бурного развития систем искусственного интеллекта спрос на технологии скоростной передачи информации будет только расти. Кремниевая фотоника позволяет уйти от лишних преобразований оптических сигналов в электрические, тем самым повышая скорость обмена данными и снижая энергопотребление. Участие SK hynix в этих разработках определяется её специализацией на разработке микросхем памяти, сейчас эта южнокорейская компания до сих пор остаётся главным поставщиком памяти типа HBM для ускорителей вычислений NVIDIA, которые доминируют на рынке. К 2027 году перечисленные компании надеются вывести на рынок технологию, которая позволяет обрабатывать оптические сигналы на уровне кремниевых компонентов, а также технологию производства памяти, способной работать на терабитных скоростях. Intel, уже имеющая определённый опыт в этой сфере, будет специализироваться на приближении данных решений к условиям массового производства, хотя от своего профильного бизнеса она не так давно избавилась. В части энергопотребления стоит задача снизить его на 30–40 % по сравнению с традиционными полупроводниковыми компонентами. Японская NTT свои эксперименты в области кремниевой фотоники проводит с 2019 года и уже добилась определённых успехов на этапе изысканий, а также располагает экспериментальной площадкой для работы с прототипами соответствующих устройств. Продажи мобильных процессоров Intel упали на 5 % в прошлом году, а настольных — на 9 %

30.01.2024 [12:01],

Алексей Разин

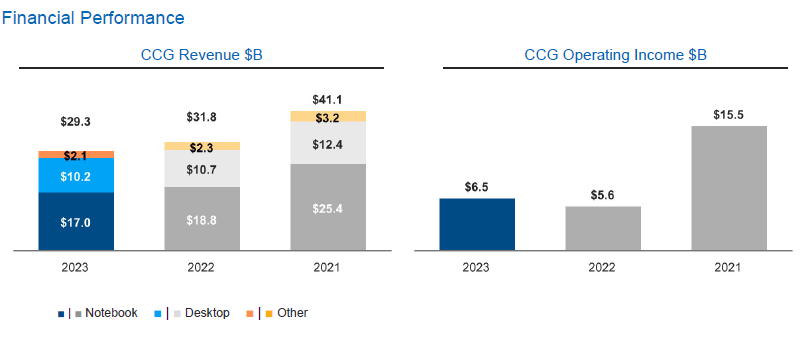

Обнародовав общую статистику по рынку клиентских систем на прошлой неделе, корпорация Intel лишь недавно опубликовала годовой отчёт по форме 10-K, который позволяет более подробно отследить динамику выручки в отдельных сегментах рынка. Компонентов для ноутбуков компания в прошлом году поставила на 5 % меньше, чем в 2022 году, а в настольном сегменте поставки сократились на все 9 %.

Источник изображения: Intel Что характерно, речь идёт именно о динамике поставок в натуральном выражении, а не в денежных показателях. Выручка Intel в сегменте ноутбуков по итогам прошлого года сократилась с $18,8 млрд до $17 млрд, на 9,6 %. Спрос на компоненты для ноутбуков был особенно слаб в первой половине года, по данным Intel, и только во втором падение было чуть компенсировано оживлением спроса по мере истощения накопленных ранее запасов продукции. Средняя цена реализации компонента Intel для ноутбуков по итогам всего 2023 года снизилась на 5 %, поскольку соответствующие устройства пользовались более уверенным спросом в сфере образования, а специфика этого рынка такова, что на нём преобладают более дешёвые процессоры с небольшим количеством ядер или модели прошлых поколений.

Источник изображения: Intel В настольном сегменте выручка Intel по итогам прошлого года сократилась на 4,7 % до $10,2 млрд, тогда как в натуральном выражении поставки уменьшились на 9 % по сравнению с 2022 годом. Второе полугодие для рынка настольных ПК в восприятии Intel тоже оказалось более благополучным, но только за счёт истощения некоторой части складских запасов продукции. Примечательно, что Intel в лучших своих традициях продолжила увеличивать среднюю цену реализации на падающих объёмах продаж — она выросла на приличные 5 %, поскольку в коммерческом и игровых сегментах рынка повышенным спросом пользовались более дорогие модели процессоров этой марки. Если сравнивать минувший год с 2022, то для клиентского бизнеса Intel он хоть и оказался чуть менее доходным ($29,3 млрд против $31,8 млрд выручки), позволил нарастить операционную прибыль с $5,6 до $6,5 млрд, а по критерию снижения объёмов поставок продукции демонстрировал более сдержанную динамику. Например, поставки компонентов для ноутбуков Intel в 2022 году сократила на 36 %, а в настольном сегменте снижение составило 19 %. Прошлогодние 5 и 9 % падения соответственно на этом фоне выглядят весьма пристойным результатом. Расширенный Mini-ITX: MaxSun выпустит плату H770YTX Terminator формата YTX с поддержкой DDR5 и PCIe 5.0

29.01.2024 [14:47],

Николай Хижняк

Китайская компания MaxSun выпустит материнскую плату H770YTX Terminator в необычном формфакторе YTX. Размеры новинки составляют 245 × 175 мм. Она похожа на увеличенную в ширине плату формата ITX. Нестандартный размер платы позволил производителю добавить ей больше портов и внутренних разъёмов, включая дополнительные слоты M.2.

Источник изображений: MaxSun MaxSun H770YTX Terminator относится к решению среднего ценового сегмента. Новинку оценили в 899 юаней ($126). В основе платы используется 10-фазная подсистема питания VRM со схемой фаз 8+1+1. Она поддерживает процессоры с максимальным TDP до 253 Вт и предназначена для использования с чипами Intel Alder Lake (Core 12-го поколения), Raptor Lake (Core 13-го поколения) или Raptor Lake Refresh (Core 14-го поколения). Одной из интересных особенностей H770YTX Terminator является то, что некоторые её коннекторы расположены на задней стороне. В частности, производитель перенёс на тыльную сторону 24-контактный разъём питания самой платы, 8+4-контактный коннектор питания процессора, разъёмы для подключения дополнительных вентиляторов, два порта SATA, а также коннекторы фронтальной панели. При покупке указанной платы следует учитывать, что она будет совместима не со всеми компьютерными корпусами. Новинка также получила четыре слота M.2 PCIe 4.0 x4, два из которых расположены по соседству с двумя DIMM-разъёмами для ОЗУ. Последние поддерживают модули памяти со скоростью до 8000 МГц через профили разгона XMP. Один из M.2 PCIe 4.0 x4 расположен на тыльной стороне платы, а ещё один — традиционно, ниже от процессорного разъёма. Дополнительно H770YTX Terminator предлагает четыре SATA-порта и один SlimNAS SFF-8654 (4 линии) для NAS-накопителей. В наличие у платы также имеется один полноценный PCIe 5.0 x16, 2,5-гигабитный сетевой адаптер и модуль Intel AX101 NIC с поддержкой Wi-Fi 6. Intel удвоит ИИ-производительность процессоров Panther Lake относительно Lunar Lake

26.01.2024 [18:09],

Николай Хижняк

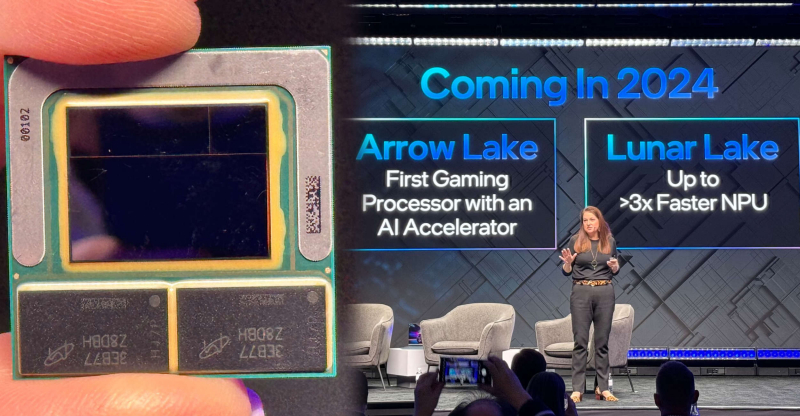

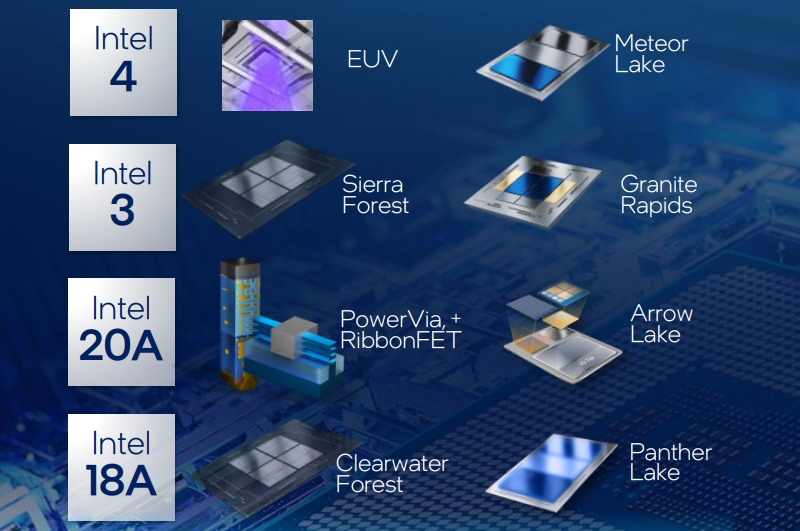

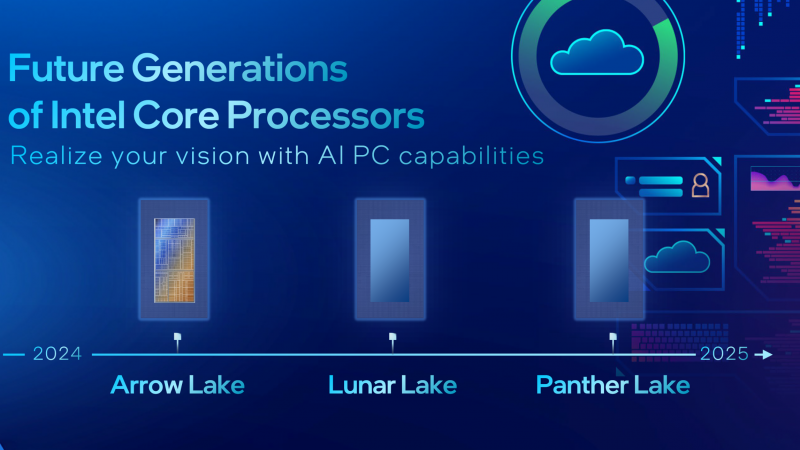

В рамках последнего финансового отчёта глава Intel Пэт Гелсингер (Pat Gelsinger) рассказал, что в этом году компания расширит платформу Core Ultra процессорами Arrow Lake и Lunar Lake. Их ИИ-производительность вырастет до трёх раз по сравнению с нынешними Meteor Lake. В следующем году компания в сегментах настольных ПК и ноутбуков представит серию процессоров Panther Lake, которые будут обладать ещё вдвое большей ИИ-производительностью по сравнению с предшественниками.

Источник изображений: Intel «Платформа Core Ultra обеспечивает нам лидерство в задачах, связанных с ИИ [в потребительском сегменте]. С запуском платформ нового поколения Lunar Lake и Arrow Lake в этом году мы удвоим отрыв от конкурентов. В 2025 году новые процессоры Panther Lake обеспечат дополнительное двукратное увеличение ИИ-производительности», — заявил Гелсингер. В рамках встречи с инвесторами глава Intel также затронул вопрос подготовки фирменного технологического процесса 18A для производства чипов. Он придёт на смену техпроцессу 20A, который будет использоваться в потребительских процессорах Arrow Lake. Гелсингер также напомнил, что серверные процессоры Xeon Granite Rapids и Sierra Forest появятся на рынке во второй половине этого года.  Новый техпроцесс 18A будет использоваться в будущих процессорах Clearwater Forest. По словам Гелсингера, разработка этих чипов уже завершена и скоро начнётся их производство. Указанные процессоры будут предназначены для ЦОД и предложат до 288 вычислительных ядер. В них будут применяться только энергоэффективные ядра нового поколения с кодовым названием Darkmont. «Мы первые в индустрии объединили в одном техпроцессе технологии GAA-транзисторов и подачи питания с обратной стороны кристалла. Вторая технология появится у наших ближайших конкурентов не ранее чем через два года. Чипы Arrow Lake станут ключевым продуктом на нашем технологическом процессе Intel 20A в этом году. Готовность техпроцесса Intel 18A к использованию в производстве ожидается во второй половине 2024 года. Я рад сообщить, что чипы Clearwater Forest, наши первые процессоры на базе Intel 18A для серверов, также готовы для производства. Скоро завершится разработка потребительских чипов Panther Lake», — добавил Гелсингер. Тут же добавим, что Intel связывает большие надежды с техпроцессом 18A не только в личных целях, но также и в качестве передового техпроцесса, который сможет предложить в качестве контрактного производителя сторонним разработчикам чипов. Компания отметила, что в 2023 году добилась успехов в создании экосистемы контрактного производства, заключив более 40 соглашений о сфере услуг по разработке и производству чипов, в том числе с военными США и аэрокосмической отраслью. «В четвёртом квартале мы выпустили набор инструментов для разработки чипов под Intel 18A версии 0.9, и расширили его доступность. Мы значительно расширили программу RAMP-C и только в этом квартале подписали крупный контракт на контрактное производство с правительством США и Министерством обороны», — отметила компания. Компания собирается провести 21 февраля мероприятие IFS Direct Connect 2024, на котором более подробно расскажет о своей дорожной карте будущих продуктов. В рамках финансового отчёта также была затронута тема будущих специализированных ИИ-ускорителей Gaudi 3. Они ожидаются в этом году и обещают четырёхкратный прирост производительности и вдвое более высокую пропускную способность по сравнению с предшественниками. Компания также продолжает разработку специализированных ускорителей Falcon Shores. «Мы продолжим освоение рынка ИИ с новыми ускорителями Gaudi 3, которые планируем выпустить в этом году. Мы ожидаем от них четырёхкратный прирост производительности и вдвое более высокую пропускную способность по сравнению с предшественниками. Сейчас мы тестируем их в лабораториях. Они действительно показывают отличный уровень быстродействия. Разработка Falcon Shores также продолжается», — заявил глава Intel. |