|

Опрос

|

реклама

Быстрый переход

ИИ-агент спроектировал полноценный процессор на RISC-V за 12 часов — промпт содержал всего 219 слов

23.04.2026 [16:51],

Николай Хижняк

Стартап Verkor.io, специализирующийся на разработке чипов с использованием искусственного интеллекта, в исследовательской статье, опубликованной в марте, рассказал, как его агентная система ИИ Design Conductor самостоятельно создала полноценное ядро процессора на архитектуре RISC-V. Для этого потребовалось всего 12 часов: система взяла за основу документ с запросом из 219 слов и сгенерировала проверенную, готовую к компоновке схему, что на несколько порядков быстрее стандартных сроков разработки коммерческих чипов, которые составляют от 18 до 36 месяцев.

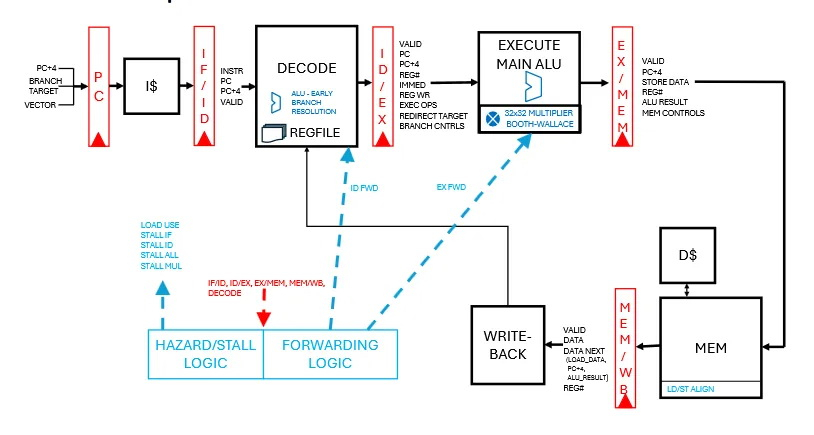

Источник изображения: Китайская академия наук По словам Verkor, это первый случай, когда автономный агент создал работающий процессор — от спецификации до файла компоновки GDSII. В результате получился процессор VerCore — пятиступенчатое конвейерное ядро с последовательным выполнением команд и однопоточной обработкой, которое при тактовой частоте 1,48 ГГц на 7-нанометровом техпроцессе ASAP7 набрало 3261 балл в тесте CoreMark. В статье Verkor подробно описана конвейерная архитектура, включающая этапы выборки, декодирования, выполнения, обращения к памяти и обратной записи команд, а также раннее разрешение ветвлений и переадресацию операндов. В ходе оптимизации система самостоятельно реализовала быстрый умножитель Бута — Уоллеса с тактовой частотой 2,57 ГГц и схему с однотактным штрафом за ветвление, которую агент выбрал после реализации и тестирования одно- и двухтактных вариантов. Verkor сравнивает производительность VerCore в тесте CoreMark с производительностью мобильного процессора Intel Celeron SU2300 2011 года на базе архитектуры Penryn. Пятиступенчатое ядро с последовательным выполнением команд, без кеша и внеочередного выполнения команд — довольно простая конструкция по отраслевым стандартам. В статье Verkor отмечается, что стоимость разработки передовых чипов превышает $400 млн, на их разработку уходит от 18 до 36 месяцев, при этом в разработке участвуют сотни инженеров. VerCore гораздо проще этих чипов. Тем не менее 12 часов, затраченные на полностью автономный процесс от спецификации до компоновки, — это впечатляющий результат, даже несмотря на то, что для этого потребовалось «множество десятков миллиардов токенов» при сравнительно невысоком уровне сложности.

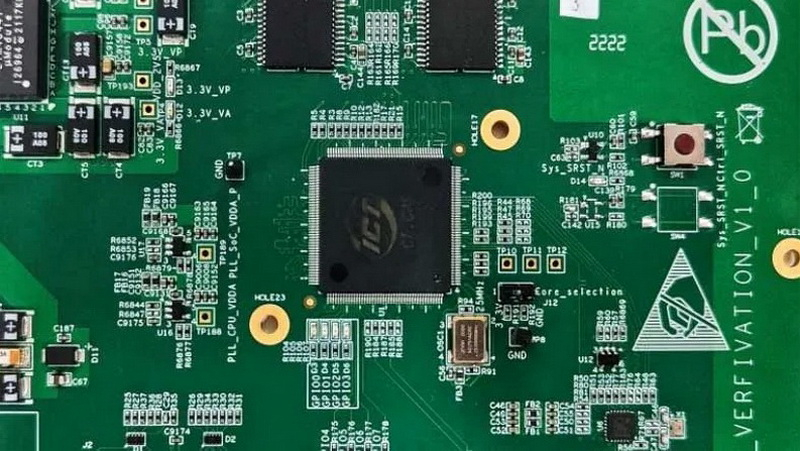

Источник изображения: Verkor.io VerCore не был изготовлен физически: вместо этого его работоспособность была проверена с помощью Spike — эталонного симулятора RISC-V ISA. ASAP7 — это комплект для разработки академических технологических процессов, а не коммерческий 7-нм техпроцесс. В Verkor утверждают, что VerCore может запускать вариант uCLinux в симуляторе. В статье Verkor честно говорится об ограничениях базовых языковых моделей и отмечается, что ИИ-агент иногда «недооценивает сложность работы, необходимой для решения тех или иных проблем». Например, в одном случае, когда не удавалось уложиться в сроки, Design Conductor пытался внести серьёзные изменения, чтобы «углубить процесс проектирования» вместо поиска более простых решений. В другом случае исследователи заметили, что модель рассуждала о Verilog — событийно-ориентированном языке — как о последовательном коде. «Хотя мы обнаружили, что это не повлияло на способность Design Conductor обеспечивать функциональную корректность, из-за этого Design Conductor стало сложнее устранять проблемы с соблюдением сроков», — пояснили исследователи. По оценкам исследователей, чтобы довести систему до состояния, готового к серийному производству, потребуется от пяти до десяти специалистов. Кроме того, с ростом сложности проекта требования к вычислительным мощностям увеличиваются нелинейно, что делает весь процесс менее практичным в коммерческом масштабе. В Verkor сообщили, что планируют опубликовать исходный код VerCore и скрипты для сборки к концу апреля, а также продемонстрировать реализацию на ПЛИС на мероприятии DAC — ежегодной конференции по автоматизации проектирования электронных устройств. В предыдущих проектах по разработке чипов с использованием искусственного интеллекта, таких как проект китайских исследователей, которые в 2023 году создали процессор на архитектуре RISC-V менее чем за пять часов, и более поздний проект QiMeng, использовались другие методологии и архитектуры. Design Conductor от Verkor самостоятельно выполняет весь процесс проектирования — от спецификации до GDSII. ИИ выполняет месяцы работы инженеров всего за ночь: Nvidia рассказала, как ускорила проектирование чипов

13.04.2026 [20:52],

Николай Хижняк

Nvidia активно использует искусственный интеллект на некоторых этапах внутреннего процесса проектирования своих чипов. Об этом в разговоре с главным научным сотрудником Google Джеффом Дином (Jeff Dean) в рамках конференции GTC рассказал главный научный сотрудник Nvidia Билл Далли (Bill Dally). По словам последнего, компания применяет ИИ для исследования проектных решений, работы со стандартной библиотекой ячеек, устранения ошибок и верификации. Далли добавил, что до полностью автоматизированного проектирования чипов ещё далеко.

Источник изображений: VideoCardz / Nvidia Одним из примеров, которыми поделился Далли, является инструмент NB-Cell от Nvidia. По его словам, раньше на перенос стандартной библиотеки ячеек компании на новый полупроводниковый техпроцесс силами команды из восьми человек уходило около 10 месяцев. ИИ-инструмент на основе обучения с подкреплением теперь выполняет эту работу за одну ночь на одном графическом процессоре, а получаемые в результате ячейки по размеру, энергопотреблению и задержке не уступают разработкам, созданным людьми, а то и превосходят их. «В процессе проектирования мы стараемся использовать ИИ везде, где только можно. Например, каждый раз, когда мы переходим на новый полупроводниковый техпроцесс, нам приходится переносить на него нашу стандартную библиотеку ячеек. В ней от 2500 до 3000 ячеек, и раньше для этого требовалась команда из восьми человек, которые работали над задачей около 10 месяцев, то есть на это уходило 80 человеко-месяцев. Затем мы разработали программу на основе обучения с подкреплением под названием NB-Cell. Думаю, сейчас у нас уже версия NB-Cell 2 или 3. Она справляется с задачей за одну ночь на одном графическом процессоре. Результаты по таким параметрам, как размер ячейки, рассеиваемая мощность и задержка, даже превосходят разработки, созданные людьми. Они соответствуют разработкам, созданным людьми, или превосходят их. Это огромный прирост производительности, и он устраняет препятствия на пути к переходу на новые техпроцессы, потому что теперь мы можем очень быстро переносить библиотеки ячеек», — Билл Далли, главный научный сотрудник Nvidia. Далли также упомянул ещё один внутренний инструмент под названием Prefix RL, предназначенный для решения давно изученной проблемы размещения упреждающих элементов в цепи упреждающего переноса. По его словам, система генерирует схемы, которые «не смог бы придумать ни один человек», при этом улучшая ключевые показатели примерно на 20–30 % по сравнению с решениями, созданными людьми. Это важная деталь, поскольку она показывает, что Nvidia использует искусственный интеллект не только для экономии времени инженеров, но и для поиска решений, выходящих за рамки обычной человеческой интуиции. В более широком смысле, по словам Далли, Nvidia использует внутренние языковые модели под названием Chip Nemo и Bug Nemo. Эти модели постоянно дорабатываются на основе собственных материалов Nvidia, в том числе RTL-кода и архитектурных документов для графических процессоров, разрабатывавшихся на протяжении многих лет. По его словам, одно из практических преимуществ заключается в том, что младшие инженеры могут обращаться к модели, а не постоянно спрашивать старших разработчиков, как работает тот или иной блок. Кроме того, система может обобщать отчёты об ошибках и помогать распределять их по нужным модулям или инженерам. К созданию спонсируемого Биллом Гейтсом нетипичного ядерного реактора подключили ИИ — процесс пойдёт живее

02.04.2026 [22:36],

Геннадий Детинич

Американская компания, которой помогает развиваться один из фондов Билла Гейтса, совместно с компанией SoftServe разработала первую в своём роде ИИ-платформу на базе Nvidia Omniverse, которая радикально ускоряет проектирование атомных реакторов. Платформа предназначена для Natrium — реактора на быстрых нейтронах с расплавом натрия — и позволяет создавать цифровые двойники объектов и готовить проектную документацию.

ИИ поможет всю эту «красоту» вписать в реальный конструкторский проект. Источник изображения: TerraPower Цифровая ИИ-платформа решает главную проблему традиционного проектирования ядерных объектов — длительную адаптацию проекта под конкретную площадку. Вместо многолетних расчётов и согласований между отделами система анализирует тысячи переменных одновременно, включая геотехнические модели, подключение к электросети и оптимизацию территории под АЭС и инфраструктуру. ППлатформа работает на основе технологии цифровых двойников, создавая трёхмерную визуализацию в реальном времени. Инженеры могут сразу видеть проблемные участки, зоны отчуждения, сочетание проекта с рельефом местности, а также возможные варианты оптимизации стоимости будущих работ — всё это ещё до начала строительства. Nvidia Omniverse обеспечивает одновременную обработку данных, что позволяет полностью заменить рутинный ручной труд. Конкретно для проекта реактора Natrium предусмотрены конфигурации от одного до четырёх блоков мощностью от 500 МВт до 2 ГВт, а первый проект на площадке Kemmerer мощностью 345 МВт в Вайоминге уже получил одобрение Комиссии по ядерному регулированию США и готовится к началу строительства со дня на день. Новая система на базе ИИ сокращает сроки проектирования объекта на площадке с 18 месяцев до 8 недель, ускоряя весь цикл проектирования с полутора лет до полутора месяцев. Это не только ускорит ввод экологически чистой энергии в строй, но и снизит риски, чреватые дорогостоящими ошибками, а также повысит точность и безопасность работ. По словам экспертов TerraPower, SoftServe и Nvidia, платформа даёт «реальное представление» обо всех ограничениях ещё до вложения первого доллара инвестиций в стройку. Таким образом, передовые ядерные технологии обещают стать конкурентоспособными по скорости развёртывания, с чем у них всегда были проблемы. Разработка TerraPower, SoftServe и Nvidia создаёт новый стандарт для инфраструктурных проектов в энергетике. Она демонстрирует, как цифровые двойники могут ускорить переход к чистой энергии и удовлетворить растущий глобальный спрос на электричество. Первый коммерческий реактор проекта Natrium в Вайоминге планируется запустить в начале 2030-х годов, что на практике подтвердит переход от теории к коммерческой эксплуатации реакторов нового поколения. Meta✴ провалила создание собственного ИИ-чипа, потому что это «слишком сложно» и кругом «технические проблемы»

28.02.2026 [10:56],

Павел Котов

Meta✴✴ столкнулась со сложностями при разработке собственных ускорителей для систем искусственного интеллекта и была вынуждена отказаться от самого передового проекта в пользу менее сложного варианта. Об этом сообщил ресурс The Information со ссылкой на осведомлённые источники.

Источник изображений: Igor Omilaev / unsplash.com На минувшей неделе Meta✴✴ отказалась продолжать работу над наиболее передовым ускорителем для обучения моделей ИИ, потому что столкнулась с трудностями при его проектировании и техническими проблемами; руководство компании проинформировало работников отдела инфраструктуры об изменении планов. Компания пересмотрела дорожную карту, имея множество запасных вариантов. Она заключила многомиллиардную сделку по аренде ИИ-ускорителей TPU у Google; инициировала партнёрский проект в области ускорителей AMD Instinct суммарной мощностью до 6 ГВт; а также объявила о намерении закупать ИИ-ускорители Nvidia текущего и перспективных поколений. Собственные чипы компания разрабатывает в рамках программы Meta✴✴ Training and Inference Accelerator (MTIA) — она призвана снизить затраты и усилить контроль над инфраструктурой центров обработки данных. «Мы по-прежнему привержены инвестициям в диверсифицированный портфель чипов для удовлетворения наших потребностей, что включает в себя развитие нашего портфеля MTIA, и в этом году мы поделимся свежей информацией», — прокомментировал происходящее представитель Meta✴✴. Компания отказалась от одной из версий своего чипа второго поколения для обучения ИИ, проходящего внутри Meta✴✴ под кодовым наименованием Iris, затем она начала работать над более совершенным чипом, которому присвоили название Olympus, но теперь отказалась и от него.  В Meta✴✴ назрело скептическое отношение к возможности создать собственные ИИ-ускорители, сопоставимые по возможностям с чипам Nvidia, признался один из разработчиков Meta✴✴ — всё дело в рисках задержек или вынужденных доработок проектов. Работа требует большой команды инженеров для проектирования, отладки чипов и обеспечения их невысокого энергопотребления, в результате чего продукты Nvidia оказываются более целесообразными. В основу предназначенного для обучения ИИ-ускорителя Iris легла технология пакетной обработки параллельных данных SIMD (Single Instruction, multiple data) — они легче в проектировании, но для них труднее писать ПО. В ускорителе Olympus использовался принятый Nvidia подход SIMT (Single Instruction, Multiple Threads), при котором множество потоков выполняет одну инструкцию, сохраняя логическую независимость. Такие чипы сложнее в проектировании, но под них проще писать ПО для обучения ИИ-моделей. Некоторые технологические компании предпочитают второй подход по образцу Nvidia, потому что он обеспечивает более высокую гибкость и лучше адаптирован для обучения современных моделей ИИ. Meta✴✴ планировала завершить разработку Olympus не раньше IV квартала 2026 года, но в действительности потребовались бы не менее девяти месяцев до передачи проекта в массовое производство. Основу архитектуры Olympus должны были составить наработки стартапа Rivos, поглощённого Meta✴✴ в минувшем году, — они совместимы с ПО Nvidia CUDA, наиболее популярным в обучении и запуске моделей ИИ. Meta✴✴ планировала разработать большие кластеры серверов на чипах Olympus, но руководство компании увидело в этом угрозу для обучения новых моделей в условиях конкуренции с OpenAI и Google. ПО для собственных ускорителей было бы менее стабильным, чем у Nvidia, а сложная архитектура Olympus могла бы затруднить его массовое производство. Поэтому пока Meta✴✴ намерена использовать в обучении ИИ ускорители партнёров, к которым прилагается более развитое и стабильное ПО. «Это большая сделка»: Nvidia вложила $2 млрд в разработчика ПО для проектирования чипов Synopsys

01.12.2025 [19:15],

Сергей Сурабекянц

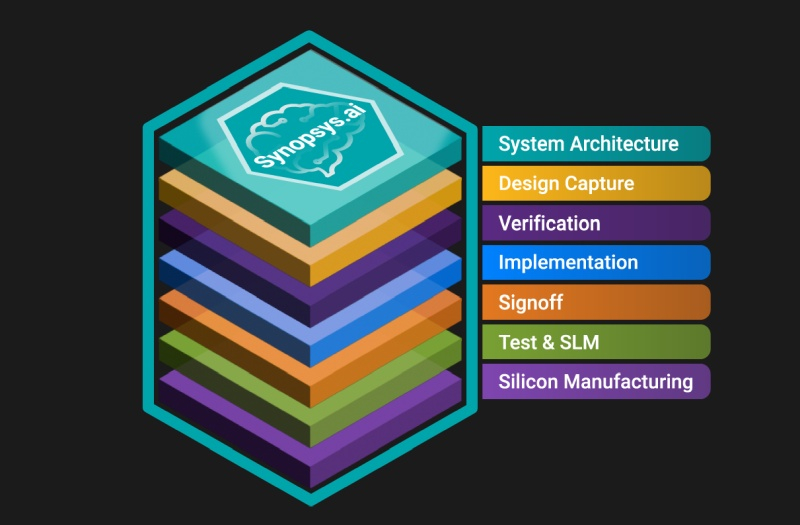

Nvidia инвестировала $2 млрд в разработчика программного обеспечения для проектирования микросхем Synopsys. Эта сделка призвана расширить многолетнее сотрудничество компаний по совместной разработке новых инструментов для проектирования полупроводников с использованием технологий искусственного интеллекта. После объявления о сделке акции Synopsys подорожали на 7 %, а акции Nvidia потеряли в цене почти 2 %.

Источник изображения: Synopsys Компания Nvidia, являющаяся клиентом Synopsys, приобрела обыкновенные акции разработчика программного обеспечения для проектирования микросхем по цене $414,79 за акцию, что на 0,8 % ниже их цены на момент закрытия торгов в пятницу. Эта крупная сделка дополнила ряд новых партнёрств Nvidia в экосистеме искусственного интеллекта на фоне опасений финансистов и инвесторов по поводу растущего числа циклических сделок между лидерами ИИ-бума. Партнёрство не будет эксклюзивным, так как одним из клиентов Synopsys является AMD, а Nvidia сотрудничает с конкурентом Synopsys — Cadence Design, специализирующейся на автоматизации электронного проектирования (Electronic Design Automation — EDA). Акции Cadence немного снизились после объявления о сделке. В рамках партнёрства Synopsys будет использовать набор инструментов разработки и библиотек кода Nvidia для работы над своими приложениями, охватывающими проектирование микросхем, физическую верификацию, молекулярное моделирование и другие процессы, связанные с EDA. «Сложность и стоимость разработки интеллектуальных систем нового поколения требуют инженерных решений с более глубокой интеграцией электроники и физики, ускоренных возможностями ИИ и вычислений», — заявил генеральный директор Synopsys Сассин Гази (Sassine Ghazi). «Это большая сделка, — заявил генеральный директор Nvidia Дженсен Хуанг (Jensen Huang). — Партнерство, о котором мы объявляем сегодня, призвано революционизировать одну из самых вычислительно-емких отраслей в мире: проектирование и инжиниринг». Nvidia последовательно вкладывает гигантские средства в компании, связанные с бурно развивающейся индустрией ИИ, начиная от сделки с OpenAI об инвестициях в размере $100 млрд, до покупки акций Intel на $5 млрд. Японская Rapidus заручилась поддержкой Siemens в сфере выпуска 2-нм чипов

05.07.2025 [07:39],

Алексей Разин

Основанная в августе 2022 года японская компания Rapidus ставит перед собой амбициозные задачи к 2027 году освоить на территории страны массовый выпуск 2-нм чипов для сторонних заказчиков. Для достижения цели ей приходится обращаться к разным партнёрам, поставщик ПО для разработки чипов Siemens стала одним из них.

Источник изображения: Siemens Самым известным партнёром Rapidus по освоению 2-нм технологии «с нуля» является американская корпорация IBM, которая первой в мире изготовила прототипы ячеек памяти на своей опытной линии в штате Нью-Йорк, используя 2-нм техпроцесс. Между тем, по мере приближения к моменту начала серийного выпуска 2-нм продукции Rapidus обрастает новыми партнёрами. Одним из них стала Siemens — крупный поставщик программного обеспечения для проектирования интегральных микросхем. Сама Rapidus разработкой чипов заниматься не будет, но профильное программное обеспечение потребуется ей для адаптации разработок клиентов к специфике своих производственных процессов. Rapidus получит доступ к платформе Calibre компании Siemens. Представители японского контрактного производителя в очередной раз заявили, что намерены существенно опередить конкурентов по сокращении времени, требуемого для постановки на конвейер вновь разработанных чипов. Профильное ПО компании Siemens будет использоваться Rapidus на всех этапах подготовки и непосредственно при производстве полупроводниковых компонентов. О конкретных клиентах Rapidus пока известно не так много, но стартап Tenstorrent может оказаться в их числе. Кроме того, японский производитель ведёт переговоры с LG и BOS Semiconductor — последняя поставляет чипы с высокой степенью интеграции в автомобильном сегменте. Сама IBM надеется со временем воспользоваться услугами Rapidus для производства своих процессоров, поскольку после «предательства» GlobalFoundries она вынуждена полагаться на Samsung. В Китае создали ИИ, который сам проектирует процессоры не хуже людей

12.06.2025 [21:04],

Николай Хижняк

Исследователи Китайской государственной лаборатории по разработке процессоров и Исследовательского центра интеллектуального программного обеспечения сообщили о создании ИИ-платформы для автоматизированной разработки микросхем. Проект с открытым исходным кодом QiMeng использует большие языковые модели (LLM) для «полностью автоматизированного проектирования аппаратного и программного обеспечения», а также может применяться для проектирования «целых CPU».

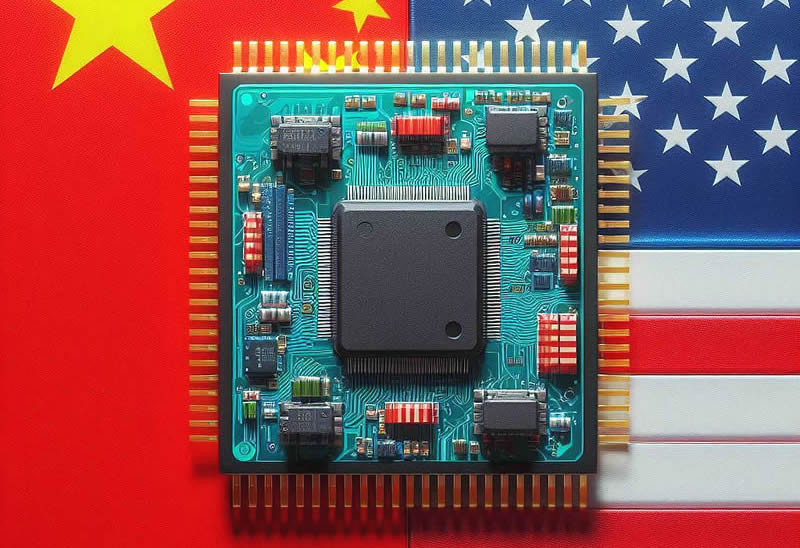

Источник изображений: Китайская академия наук По словам разработчиков, чипы, разработанные QiMeng, соответствуют производительности и эффективности тех микросхем, которые были созданы экспертами-людьми. На базе QiMeng исследователи в качестве примера уже спроектировали два процессора: QiMeng-CPU-v1, сопоставимый по возможностям с Intel 486; и QiMeng-CPU-v2, который, как утверждается, может конкурировать с чипами на Arm Cortex-A53. Стоит отметить, что разница между этими продуктами составляет 26 лет. Чип Intel 486 был представлен в 1986 году, а Arm Cortex-A53 — в 2012-м. QiMeng состоит из трёх взаимосвязанных слоёв: в основе лежит доменно-специфическая модель большого процессорного чипа; в середине — агент проектирования аппаратного и программного обеспечения; верхним слоем выступают различные приложения для проектирования процессорных чипов. Все три слоя работают в тандеме, обеспечивая такие функции, как автоматизированное front-end-проектирование микросхем, генерация языка описания оборудования, оптимизация конфигурации операционной системы и проектирование цепочки инструментов компилятора. По словам разработчиков платформы, QiMeng может за несколько дней сделать то, на что у команд, состоящих из людей-инженеров, уйдут недели работы. В опубликованной статье, описывающей особенности платформы QiMeng, её разработчики также освещают проблемы, с которыми приходится сталкиваться при текущем проектировании чипов, включая «ограниченную технологию изготовления, ограниченные ресурсы и разнообразную экосистему». QiMeng же стремится автоматизировать весь процесс проектирования и проверки чипов. По словам разработчиков, цель заключалась в повышении эффективности, снижении затрат и сокращении циклов разработки по сравнению с ручными методами проектирования микросхем, а также в содействии быстрой настройке архитектур микросхем и программных стеков, специфичных для конкретной области. Как пишет Tom’s Hardware, крупные западные технологические компании, занимающиеся проектированием микросхем, такие как Cadence и Synopsys, тоже активно внедряют ИИ в процессы создания чипов. Например, Cadence использует несколько ИИ-платформ для ключевых этапов проектирования и проверки. В свою очередь, ИИ-платформа DSO.ai от Synopsys, по последним подсчётам, помогла с разработкой более 200 проектов микросхем. Анонс платформы QiMeng произошёл на фоне давления властей США на ведущих поставщиков программного обеспечения для автоматизации проектирования электроники (EDA), чтобы те прекратили продажу инструментов для проектирования микросхем в Китай, что ещё больше усложнило задачу Пекина по укреплению своей полупроводниковой промышленности. Разработчики QiMeng отмечают, что Китай должен отреагировать, поскольку технология проектирования чипов является «стратегически важной отраслью». Издание South China Morning Post со ссылкой на данные последнего анализа Morgan Stanley сообщает, что на долю Cadence Design Systems, Synopsys и Siemens EDA в прошлом году пришлось в общей сложности 82 % выручки на китайском рынке EDA. США запретили поставки ключевого ПО для проектирования чипов в Китай

29.05.2025 [04:37],

Анжелла Марина

Администрация Дональда Трампа (Donald Trump) потребовала от американских компаний, разрабатывающих программное обеспечение для проектирования полупроводников, прекратить поставки в Китай. Под ограничения попали крупнейшие разработчики, работающие по модели EDA (Electronic Design Automation) — Cadence, Synopsys и Siemens EDA.

Источник изображения: AI Как сообщает Financial Times, это решение направлено на то, чтобы затруднить развитие китайской микроэлектроники и создание передовых ИИ-чипов. Бюро промышленности и безопасности (BIS) при министерстве торговли США уведомило компании о запрете письменно, правда, пока неясно, кто из участников EDA получил директиву. По крайней мере, глава компании Synopsys Сассин Гази (Sassine Ghazi) заявил, что пока не получил официального уведомления от BIS. Представитель Минторга США подтвердил, что ведомство «пересматривает экспорт технологий стратегического значения в Китай» и в некоторых случаях приостанавливает действующие лицензии. Решение принято на фоне переговоров двух стран о торговой сделке после временного перемирия по тарифам. Однако эксперты отмечают, что новые ограничения подрывают хрупкие договорённости, достигнутые в Женеве. Кристофер Джонсон (Christopher Johnson), экс-аналитик ЦРУ по Китаю, считает, что обе стороны стремятся сохранить рычаги давления, что увеличивает риск срыва перемирия. Отмечается, что EDA-софт составляет относительно небольшую долю в индустрии чипов, но он играет ключевую роль в проектировании новых поколений микросхем. Только три американские компании Synopsys, Cadence и Siemens EDA контролируют около 80 % китайского рынка EDA. В 2024 финансовом году Synopsys заработал на Китае почти $1 млрд, а Cadence — $550 млн. После новостей о требовании властей США прекратить поставки в Китай ПО акции Synopsys упали на 9,6 %, Cadence на 10,7 %. Ранее администрация Байдена уже ограничивала поставки ПО для чипов в КНР, но компании продолжали продавать продукты, соответствующие экспортным нормам. Также во время первого президентского срока Трампа Huawei был запрещён доступ к американским EDA-инструментам. Однако сейчас эта компания активно развивает собственные ИИ-чипы серии Ascend, конкурирующие с чипами Nvidia. Китай в целом развивает собственные аналоги. Так, местные компании Empyrean Technology, Primarius и Semitronix активно наращивают долю этого рынка, а глава Nvidia Дженсен Хуанг (Jensen Huang) заявил, что экспортные ограничения не смогли остановить развитие китайской экосистемы ИИ. OpenAI завершит разработку и запустит производство своего ИИ-чипа уже в 2025 году — это первый шаг к снижению зависимости от Nvidia

10.02.2025 [17:54],

Сергей Сурабекянц

Признанный лидер в сфере ИИ, компания OpenAI, прикладывает серьёзные усилия по снижению зависимости от ускорителей ИИ производства Nvidia. В ближайшие несколько месяцев OpenAI планирует завершить разработку собственного чипа и начать его производство на фабриках TSMC с использованием самых передовых техпроцессов. Источник изображения: Samsung По мнению аналитиков, «OpenAI находится на пути к достижению своей амбициозной цели массового производства на мощностях TSMC в 2026 году». Наиболее ответственным этапом на пути от дизайна к выпуску готовых чипов является Tape-out («тейпаут») — процесс переноса цифрового проекта чипа на фотошаблон для последующего производства. Обычно этот этап обходится в несколько десятков миллионов долларов, а до выпуска первого чипа проходит до шести месяцев. В случае сбоя требуется диагностировать проблему и повторить процесс. OpenAI рассматривает свой будущий ускоритель ИИ как стратегический инструмент для укрепления переговорных позиций с другими поставщиками чипов. Если первоначальный выпуск пройдёт удачно, OpenAI уже в этом году представит альтернативу чипам Nvidia, которые сейчас занимают более80 % рынка ИИ-ускорителей. В случае успеха первого чипа инженеры OpenAI планируют разрабатывать все более продвинутые процессоры с более широкими возможностями с каждой новой итерацией. Компания уже стала участником инфраструктурной программы Stargate стоимостью $500 млрд, объявленной президентом США Дональдом Трампом (Donald Trump) в прошлом месяце. Чип разрабатывается внутренней командой OpenAI во главе с Ричардом Хо (Richard Ho) в сотрудничестве с Broadcom. Хо более года назад перешёл в OpenAI из Google, где руководил программой по созданию специализированных чипов ИИ. Хотя команда Хо за последние месяцы выросла до 40 сотрудников, это количество по прежнему на порядок меньше, чем в масштабных проектах таких технологических гигантов, как Google или Amazon. Аналитики полагают, что на первом этапе новый ускоритель ИИ от OpenAI будет играть ограниченную роль в инфраструктуре компании. Чтобы создать столь же всеобъемлющую программу по проектированию чипов ИИ, как у Google или Amazon, OpenAI придётся нанять сотни инженеров. Согласно отраслевым источникам, новый дизайн чипа для амбициозной масштабной программы может обойтись в $500 млн. Эти расходы могут удвоиться, если учитывать необходимость создания программного обеспечения и периферийных устройств. Для сравнения: в 2025 году Meta✴✴ планирует потратить $60 млрд на ИИ-инфраструктуру, а годовые инвестиции Microsoft в этом направлении составят $80 млрд. |

|

✴ Входит в перечень общественных объединений и религиозных организаций, в отношении которых судом принято вступившее в законную силу решение о ликвидации или запрете деятельности по основаниям, предусмотренным Федеральным законом от 25.07.2002 № 114-ФЗ «О противодействии экстремистской деятельности»; |