|

Опрос

|

реклама

Быстрый переход

TSMC уже вовсю выпускает чипы по улучшенному 3-нм техпроцессу N3P — на очереди N3X

24.04.2025 [06:43],

Дмитрий Федоров

В апреле 2025 года на технологическом симпозиуме в Северной Америке компания TSMC объявила, что начала серийное производство чипов по техпроцессу N3P ещё в IV квартале 2024 года. Эта 3-нм платформа третьего поколения сохраняет полную совместимость с дизайнами чипов для прежней версии 3-нм техпроцесса и ориентирована на задачи, где критичны высокая производительность и экономичное энергопотребление — от пользовательских устройств до центров обработки данных.

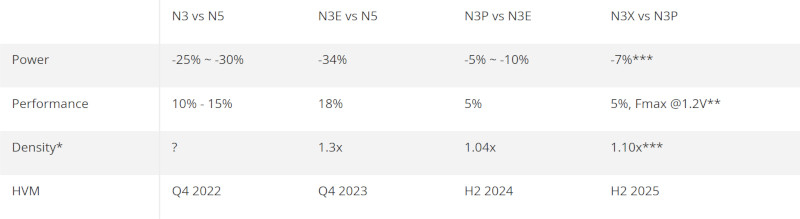

Источник изображения: TSMC Технология N3P представляет собой оптическое сжатие предыдущего техпроцесса N3E. Сохраняя прежние правила проектирования и совместимость с блоками чипов, она обеспечивает прирост производительности до 5 % при неизменном уровне утечки токов либо снижение энергопотребления на 5–10 % при тех же частотах. Кроме того, в схемах со стандартной пропорцией логических, SRAM и аналоговых элементов (50 %, 30 % и 20 % соответственно), N3P даёт прирост плотности транзисторов на 4 %. Повышение плотности интеграции в N3P достигнуто за счёт улучшения оптических параметров литографического процесса, а не изменений в проектных нормах, что способствует более эффективному масштабированию всех функциональных структур микросхемы. Это преимущество особенно проявляется в проектах с преобладанием памяти SRAM, где критична высокая плотность интеграции. В настоящее время техпроцесс применяется для выполнения производственных заказов ключевых клиентов компании. TSMC уточняет, что развитие 3-нм линейки техпроцессов не ограничивается узлом N3P. Следующим этапом станет 3-нм техпроцесс N3X, массовое производство которого запланировано на II полугодие 2025 года. Эта версия ориентирована на достижение максимальных тактовых частот и, согласно внутренним оценкам компании, обеспечивает увеличение максимальной производительности на 5 % при фиксированном энергопотреблении либо позволяет снизить энергопотребление на 7 % при неизменной частоте по сравнению с N3P.

* Плотность чипа, опубликованная TSMC, отражает «смешанную» структуру чипа, состоящую из 50 % логических элементов, 30 % памяти SRAM и 20 % аналоговых блоков. ** При одинаковой площади. *** При одинаковой тактовой частоте. Источник изображения: Tom's Hardware Ключевое отличие техпроцесса N3X — поддержка напряжения питания до 1,2 вольт, что является аномально высоким значением для 3-нм технологического узла. Это позволяет микросхемам достигать максимальной тактовой частоты (Fmax), что особенно важно для процессоров клиентского сегмента. Однако такая возможность сопряжена с серьёзными технологическими ограничениями: мощность, обусловленная токами утечки, может возрасти до 250 %. Поэтому при проектировании микросхем на базе N3X требуется инженерный компромисс между производительностью и тепловыми параметрами устройства. Старший вице-президент по развитию бизнеса и глобальным продажам, а также заместитель операционного директора TSMC Кевин Чжан (Kevin Zhang) отметил, что компания продолжает оптимизировать свои техпроцессы даже после их перехода к массовому производству. По его словам, переход на новый технологический узел требует от клиентов значительных инвестиций, включая разработку чипов в рамках экосистемы. Поэтому стратегия TSMC направлена на непрерывную оптимизацию уже внедрённых техпроцессов, чтобы клиенты могли дольше сохранять эффективность ранее сделанных вложений. TSMC традиционно выпускает несколько итераций одного технологического узла в рамках единого комплекта разработки — Process Development Kit (PDK). Примером служат серии техпроцессов N5 и N4, включающие, соответственно, N5P и версии N4P и N4C. Такой подход позволяет компании максимально эффективно использовать дорогостоящее технологическое оборудование, а клиентам — снижать затраты за счёт повторного использования IP-блоков. Узлы N3P и N3X органично продолжают эту стратегию в рамках 3-нм семейства техпроцессов. Несмотря на активное внимание к перспективным 2-нм техпроцессам, основанным на транзисторах с полным затвором (GAA), основная масса процессоров для клиентских устройств, которые выйдут на рынок в ближайшие кварталы, будет производиться с использованием техпроцессов семейства N3. К числу таких решений относятся смартфоны, планшеты и компьютеры новых поколений, запуск которых ожидается в 2025 году и позднее. Samsung будет выпускать для AMD передовые 3-нм чипы с GAA-транзисторами

01.06.2024 [09:02],

Анжелла Марина

Компания Samsung объявила о расширении стратегического партнерства с американской компанией Advanced Micro Devices (AMD) в области разработки передовой 3-нанометровой технологии производства чипов. Используя более тесные связи с AMD, Samsung стремится обогнать своего главного конкурента, контрактного производителя полупроводников TSMC.

Источник изображения: Samsung Это партнерство позволит компаниям объединить усилия в разработке инновационных решений для производства чипов следующего поколения, которые будут использоваться в высокопроизводительных вычислительных системах, центрах обработки данных, смартфонах и других электронных устройствах. Как сообщает корейское новостное издание KED Globall, в рамках соглашения Samsung, крупнейший в мире производитель микросхем памяти, получит доступ к передовым разработкам AMD в области архитектуры чипов, а AMD, который в свою очередь разрабатывает микропроцессоры и графические процессоры, сможет воспользоваться мощностями Samsung по производству чипов с использованием новейшей 3-нм технологии транзисторов Gate-All-Around (GAA). Данная технология позволяет создавать чипы с рекордной плотностью транзисторов и улучшенными характеристиками производительности. По сравнению с предыдущим поколением 5-нм чипов, 3-нм чипы GAA обеспечивают прирост производительности на 30 %, снижение энергопотребления на 50 % и уменьшение площади чипа на 45 %. В настоящее время Samsung является единственным производителем в мире, который уже запустил 3-нм техпроцесс GAA в коммерческое производство, опередив основного конкурента тайваньскую компанию TSMC. Расширение сотрудничества с AMD позволит Samsung нарастить свою долю на рынке контрактного производства чипов и сократить отставание от TSMC. Известно, что в настоящее время Samsung контролирует около 17 % этого рынка, а TSMC — более 50 %. В дальнейшем Samsung планирует начать массовый выпуск 2-нм чипов на базе технологии GAA в 2025 году, что позволит ей упрочить лидерство в области полупроводниковых технологий. |