⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Объясняем, почему Intel Alder Lake — главный процессор этой осени

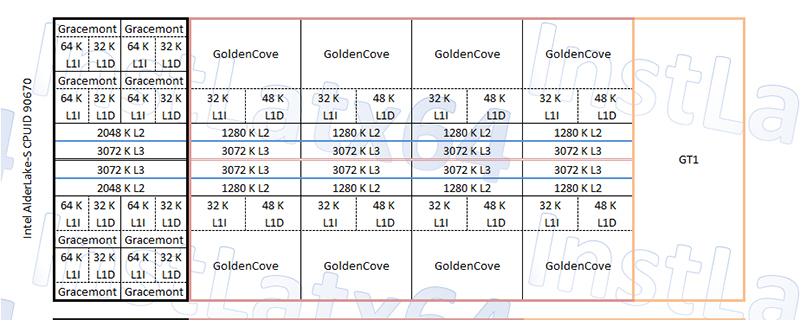

В этом году Intel® развернула небывалую активность. Кажется, до сих пор не случалось такого, чтоб нам пришлось анализировать два последовательных дизайна клиентских процессоров в течение всего нескольких месяцев. Но всё когда-то бывает в первый раз, и сегодня – вполне подходящий момент, чтобы предварительно познакомиться с процессорами Alder Lake, хотя предыдущее поколение Rocket Lake всё ещё остаётся недавней новинкой. В действительности до выхода Alder Lake пока ещё есть немного времени. Процессоры этого семейства, по всей видимости, будут анонсированы на специальном мероприятии Intel Innovation 27-28 октября, то есть через месяц. Однако предстоящий анонс представляется слишком грандиозным событием, чтобы не подготовиться к нему заранее. Ведь на этот раз выход новых процессоров будет означать и смену платформы, и смену микроархитектуры, и даже в каком-то смысле смену всей концепции многопоточных вычислений. Именно поэтому мы решили собрать и систематизировать всю имеющуюся информацию, касающуюся Alder Lake, заранее, с тем чтобы по прошествии месяца встречать эти процессоры во всеоружии, обладая всем набором необходимых теоретических знаний. К счастью, Intel уже раскрыла довольно много подробностей о строении и внутреннем устройстве Alder Lake во время презентаций Intel Accelerated и Intel Architecture Day 2021. Благодаря этому сегодня мы в рамках партнёрского проекта с компанией Intel сможем поговорить о будущих потребительских процессорах, основываясь исключительно на проверенных данных из первых рук. ⇡#Alder Lake с высоты птичьего полёта Выход процессоров Alder Lake вне зависимости от того, насколько они окажутся успешны, станет очень большим событием для всего процессорного рынка. Дело не только в том, что в них Intel серьёзно обновит микроархитектуру и добавит поддержку принципиально новых типов памяти и внешних интерфейсов, но ещё и в том, что они станут воплощением совершенно иной концепции многопоточных вычислений, прибегать к которой в массовых x86-процессорах пока ещё никто не пытался. Речь идёт о том, что Alder Lake получат гибридное строение и будут основываться на ядрах двух типов одновременно – производительных (P-ядрах) и эффективных (E-ядрах). Их объединение в одном вычислительном устройстве, по задумке разработчиков, должно позволить добиться недостижимой ранее гибкости как в смысле сферы применимости таких процессоров, так и с точки зрения соотношения производительности и энергоэффективности. Гибридный подход big.LITTLE уже давно используется в процессорах с архитектурой ARM, и идея Intel, которая будет воплощена в Alder Lake, чем-то напоминает эту схему. По задумке Intel, большие производительные ядра следует бросать на решение высокоприоритетных задач переднего плана, требующих короткого времени реакции, в то время как маленькие и энергоэффективные ядра могут заняться фоновыми процессами. Кроме того, все типы ядер можно объединить для решения одной задачи, что позволит достичь максимального уровня быстродействия, по крайней мере в теории. При этом оба типа ядер в Alder Lake получили новые микроархитектуры, с которыми мы до сих пор не сталкивались. Производительные ядра основаны на микроархитектуре Golden Cove, которая является дальнейшим развитием Cypress Cove (из Rocket Lake) и Willow Cove (из Tiger Lake). А эффективные ядра имеют микроархитектуру Gracemont, которая выросла из процессоров Atom и является дальнейшим развитием микроархитектуры Tremont, применявшейся как в экспериментальных процессорах Lakefield, так и в более понятных Pentium (Silver) и Celeron серий N и J с кодовыми именами Jasper Lake и Elkhart Lake. Важной задачей, которую Intel ставила перед собой при разработке Alder Lake, было создание не только двух типов ядер, но и более широкого набора разнообразных конструкционных блоков, которые могли бы позволить легко собирать различные по назначению потребительские процессоры для разных рыночных сегментов и с различными характеристиками: как высокопроизводительные настольные, так и мобильные и даже ультрамобильные. Несмотря на заложенную в дизайне модульность, в процессорах Alder Lake пока не применяется тайловая топология – аналог чиплетов в видении Intel. Такой способ сборки компания возьмёт на вооружение чуть позднее. Вместо этого различные варианты Alder Lake конструируются на одном монолитном полупроводниковом кристалле. Но для удобства разработчики специально подогнали размеры составных частей Alder Lake друг к другу, и, например, одно производительное P-ядро примерно соответствует по площади собранным в кластер четырём эффективным E-ядрам. Подобные пропорции выдерживаются и для других элементов процессора (для графического ядра, контроллера памяти, контроллера PCIe и проч.) – это как раз и обеспечивает многообразие и гибкость конфигураций. Неотъемлемой частью будущих процессоров Alder Lake, как и раньше, осталось графическое ядро. Intel предусмотрела два варианта графики: GT1 с 32 исполнительными устройствами для настольных процессоров и GT2 c 96 устройствами для мобильных применений. Встроенные GPU базируются на графической архитектуре 12-го поколения, то есть они относятся к классу Xe LP и примерно соответствуют по возможностям графическому ядру процессоров Tiger Lake. В варианте GT2 встроенная графика, как ожидается, сможет обеспечить приемлемую игровую производительность в разрешении 1080p (с низкими настройками качества) и будет поддерживать 12-битный конвейер воспроизведения видео. Однако в десктопные процессоры попадёт лишь более простой вариант GPU. Отсутствие кардинальных обновлений в графическом ядре должен скомпенсировать новый контроллер памяти с поддержкой сразу четырёх типов SDRAM. Он может работать как с новыми DDR5-4800 и LPDDR5-5200, так и со старой памятью DDR4-3200 и LPDDR4X-4266. Естественно, все четыре типа памяти будут поддерживаться не одновременно: выбор того или иного варианта будет происходить на этапе проектирования конкретной платформы. Логично ожидать, что поддержка DDR5 SDRAM в первую очередь появится в высокопроизводительных десктопах (условно говоря, основанных на чипсетах Z-серии), в то время как решения среднего уровня продолжат опираться на привычную DDR4- и LPDDR4X-память. И так будет продолжаться до тех пор, пока цена модулей DDR5 будет существенно превышать стоимость DDR4. Блок интерфейса PCI Express, который инженеры Intel спроектировали для Alder Lake, также содержит серьёзные инновации. Впервые в потребительском сегменте он наделён поддержкой протокола PCIe 5.0, который обеспечивает очередное удвоение пропускной способности и позволяет обеспечить графическому слоту PCIe x16 полосу 64 Гбайт/с. В то же время для подключения NVMe-накопителей процессорный контроллер предлагает лишь интерфейс PCIe 4.0 x4, которого, впрочем, достаточно для любых представленных на рынке SSD. Кроме того, поддержка PCIe 5.0 будет присутствовать исключительно в настольных версиях Alder Lake. Процессоры, отнесённые к мобильному сегменту, получат иной контроллер PCIe, в котором возможности будут каким-то образом урезаны. Но есть и обратные примеры: некоторые конструкционные блоки Alder Lake предназначаются исключительно для мобильных вариантов CPU. К их числу относятся, например, контроллер Thunderbolt 4 или сопроцессор обработки изображений IPU. Они встраиваться в настольные версии процессоров не будут. Все элементы Alder Lake, включая разные ядра, графику и фрагменты L3-кеша, контроллеры памяти и PCIe, а также все прочие блоки, как и ранее, объединены в одно целое посредством двунаправленной кольцевой шины, которая в этой реализации имеет пропускную способность до 1000 Гбайт/с. Похожий вариант кольцевой шины уже использовался в мобильных Tiger Lake, однако в новых процессорах Intel пообещала дополнительные оптимизации, направленные на снижение задержек. Ещё одно большое нововведение касается технологического процесса производства. Alder Lake станут первыми чипами Intel, которые будут выпускаться по техпроцессу Intel 7 – до недавнего переименования он фигурировал под названием 10 нм Enhanced SuperFin. Речь здесь идёт о втором этапе оптимизаций процесса с 10-нм нормами, который должен обеспечить улучшение удельной производительности на ватт на 10-15 % относительно прошлой версии техпроцесса 10 нм SuperFin. Хотя ранее техпроцесс Intel 7 считался 10-нм, по плотности размещения транзисторов на кристалле он либо сравним, либо превосходит 7-нм техпроцесс других производителей, что как раз и дало производителю моральное право переименовать технологию в Intel 7. Так, согласно данным WikiChip, бывший 10-нм техпроцесс Intel обеспечивает размещение 100,76 млн транзисторов на мм2, в то время как 7-нм процесс TSMC упаковывает на той же площади только 91,2 млн транзисторов. Пользуясь данной производственной технологией, Intel собирается упаковывать в полупроводниковые кристаллы Alder Lake до восьми производительных и восьми эффективных ядер одновременно. Это значит, что максимальное число ядер в будущих процессорах достигает 16, но такие конфигурации будут предлагаться только для настольных платформ. Довольно непривычно, что максимальный 16-ядерный процессор сможет исполнять одновременно не 32, а только 24 потока, а объём его кеш-памяти третьего уровня составит 30 Мбайт. Такое странное сочетание числа ядер и потоков обусловлено тем, что P-ядра обладают поддержкой технологии Hyper-Threading, в то время как E-ядра её лишены. Более того, они работают на разных тактовых частотах и обладают различными по объёму и организации кешами. Всё это значит, что паспортные характеристики разнообразных моделей Alder Lake могут многим показаться удивительными: в зависимости от количества тех или иных ядер конкретные CPU будут получать очень непривычные комбинации числа потоков и ядер, частот и объёма кеш-памяти. На данный момент Intel раскрыла три базовые конструкции полупроводниковых кристаллов Alder Lake, нацеленные на три различных сегмента: высокопроизводительные настольные процессоры Alder Lake-S, которые будут устанавливаться в новое поколение материнских плат с процессорным разъёмом LGA1700; мобильные процессоры Alder Lake-P с тепловым пакетом от 12 до 35 Вт в исполнении BGA Type3; ультрамобильные Alder Lake-M в корпусе BGA Type4 HDI с тепловым пакетом от 7 до 15 Вт, предназначенные для ультрабуков. Кристалл процессоров Alder Lake-S содержит восемь P-ядер, восемь E-ядер и графику GT1. В Alder Lake-P число P-ядер ограничивается шестью, но зато используется производительная графика GT2. А в Alder Lake-M предусматривается лишь два P-ядра, но всё те же восемь E-ядер и GT2 GPU. Судя по всему, первыми на рынок придут процессоры Alder Lake-S для настольных систем. Их модельный ряд будет возглавлять процессоры Core i9 с ядерной формулой 8 + 8, а также, по неподтверждённой пока информации, в него могут войти процессоры Core i7 с формулой 8 + 4, два варианта Core i5 с формулой 6 + 4 или 6 + 0, и, возможно, процессоры Core i3 со схемой ядер 4 + 0. Отдельно необходимо подчеркнуть, что такая запись числа ядер в виде суммы двух слагаемых используется непроста. Суммировать количество P- и E-ядер неправильно: Intel не собирается преподносить старшие Alder Lake в качестве 16-ядерных предложений, они скорее будут позиционироваться как продвинутые восьмиядерники с дополнительными энергоэффективными ядрами. Поэтому, например, не стоит удивляться составу серии Core i5, где одновременно будут представлены процессоры с 10 и с 6 ядрами: число E-ядер не считается определяющим фактором и может варьироваться у соседних моделей. ⇡#Как это всё работает: Intel Thread Director Строго говоря, Alder Lake – не первые x86-процессоры, объединяющие ядра двух разных типов. Ранее Intel уже выпускала гибридные энергоэффективные процессоры Lakefield, где одно ядро Sunny Cove соседствовало с четырьмя ядрами Tremont. Однако они не получили заметного признания и, хотя были представлены только во втором квартале прошлого года, уже сняты с производства. Своей печальной участью они отчасти обязаны проблемам с их функционированием в Windows 10, которая не всегда правильно распределяла нагрузку по разнородным ядрам, что приводило к снижению производительности. Изначально предполагалось, что для устройств на базе Lakefield будет предназначена специальная операционная система Windows 10X, в которой будут заложены адаптированные алгоритмы, однако, к сожалению, её выпуск Microsoft отменила. Эта история вызывает опасения, что подобное может произойти и с Alder Lake. Ведь совершенно очевидно, что для правильной работы гибридных процессоров планировщик операционной системы должен различать типы ядер и динамически отправлять требовательные нагрузки на ядра, способные предложить высокую производительность, попутно освобождая их от фоновых задач. Но на этот раз Intel всё предусмотрела. Чтобы помочь планировщику лучше разобраться в структуре процессора и добиться максимальной эффективности работы, в Alder Lake появилась аппаратная технология Intel Thread Director, которая будет отвечать за распределение нагрузки совместно с новой операционной системой Windows 11. Суть Thread Director состоит в том, чтобы передать планировщику ОС подробные телеметрические данные о текущем состоянии всех ядер, благодаря которым он сможет принимать обоснованные решения о привязке потоков к конкретным ядрам. Данная технология, как обещает Intel, должна обходить все трудности, которые могут возникать при практической эксплуатации гибридных процессоров с ядрами разных типов. И самое главное, она совершенно прозрачна для программного обеспечения и не требует внесения каких-либо изменений в программный код. Основной частью Intel Thread Director является встроенный в процессор микроконтроллер, который собирает подробные низкоуровневые данные о каждом ядре процессора, включая температуру, энергопотребление, загрузку и прочие параметры, и с минимальными задержками передаёт их планировщику операционной системы. Помимо этого, Thread Director непрерывно, с наносекундной дискретностью, отслеживает инструкции, которые исполняются каждым ядром, а также анализирует загрузку их исполнительных устройств. Базируясь на всей этой информации, планировщик получает возможность переключать потоки между ядрами полностью обоснованно и в соответствии с понятной стратегией, суть которой заключается в том, чтобы обеспечить задачам переднего плана и приложениям, чувствительным к задержкам, максимальную скорость выполнения. Например, более высокий приоритет при перемещении на производительные ядра получают потоки, которые оперируют векторными инструкциями, а потоки, работающие со скалярными инструкциями, с большей вероятностью отправляются на энергоэффективные ядра. Но в любом случае вся эта система динамична и переброс потоков с одних ядер на другие зависит от массы различных факторов, и в том числе от видов нагрузки, исполняемой на процессоре в каждый конкретный момент времени. Intel привела несколько примеров того, как работает Thread Director в некоторых частных случаях. Например, когда все ядра свободны, единичный процесс всегда будет отправлен сразу на P-ядро, однако если в момент старта процесса все такие ядра заняты, он начнёт работу на E-ядре и переместится на P-ядро только тогда, когда Thread Director сочтёт такой перенос целесообразным. В другой ситуации, когда процессор загружается всё возрастающим числом равноправных потоков, они сначала отправляются по одному на каждое свободное P-ядро, затем по одному на каждое свободное E-ядро, а потом по одному на виртуальные ядра, существующие за счёт технологии Hyper-Threading. Отдельно оговаривается и то, что привязка потоков к ядрам не постоянна, и они могут активно перемещаться с одного типа ядер на другой прямо в процессе работы. Это может происходить как из-за изменения характера нагрузки внутри вычислительного потока, так и в ситуациях, когда количество требовательных потоков начинает превышать число производительных ядер. В этой ситуации некоторые потоки будут перенесены на E-ядра с целью высвободить мощности под ту нагрузку, которая больше нуждается в вычислительных мощностях в каждый конкретный момент времени. Существовавшие до сих пор процессоры и операционные системы не обменивались информацией, чтобы оптимизировать распределение вычислительных ресурсов: планировщик опирался исключительно на данные о приоритетах потоков, назначенных им либо самой операционной системой, либо разработчиками программы. Теперь же за счёт технологии Thread Director работа планировщика должна стать более самостоятельным, тонким и динамичным процессом. Такой симбиоз аппаратных и программных средств внушает надежду, что разнородные ядра гибридных процессоров Alder Lake будут задействованы именно так, как задумано Intel, – чтобы обеспечивать максимальный уровень быстродействия. Вместе с тем внедрение Thread Director добавляет новые возможности и для разработчиков ПО. Доступные для процессоров Alder Lake расширения библиотек PowerThrottling API вводят для потоков дополнительные атрибуты качества обслуживания, благодаря которым авторы программ при желании смогут размечать создаваемые потоки. Кроме того, для потоков, которые заведомо способны работать на энергоэффективных ядрах и не нуждаются в высоких вычислительных мощностях, введена отдельная маркировка. Известно, что различные компоненты Windows 11, включая браузер Edge, будут использовать описанные расширения, что ещё раз отражает близкое сотрудничество Intel с Microsoft в вопросе создания и поддержки гибридной процессорной архитектуры. К сожалению, Intel не стала делиться подробной информацией о работе Thread Director, поэтому пока нам придётся принять на веру тот факт, что благодаря этой технологии нужная нагрузка действительно будет отправляться на нужные ядра. Впрочем, процессоры Alder Lake позволят отключить E-ядра, если у пользователя возникнут сомнения в целесообразности их привлечения к работе. Говоря о распределении потоков по ядрам гибридного процессора, Intel делает особый упор на новую операционную систему Windows 11 с оптимизированным планировщиком. Тем не менее Alder Lake должны приемлемо работать и без реализованного в этой операционной системе тесного взаимодействия между Alder Lake и планировщиком. Intel указывает, что и в старой операционной системе Windows 10 новые процессоры смогут работать вполне нормально. Хотя технология Thread Director в Windows 10 не поддерживается, эта операционная система опирается на механизм Intel Hardware Guided Scheduling, который тоже способен переключать потоки с учётом разнородности ядер, просто не настолько точно и с несколько более низкой частотой. Тем не менее, по утверждению Intel, заметить невооружённым глазом разницу в производительности Alder Lake в Windows 10 и Windows 11 будет довольно сложно. О том, что энергоэффективные ядра Gracemont не имеют 512-битных регистров и не поддерживают набор инструкций AVX-512, известно довольно давно, и это кажется вполне естественным, если вспомнить, что реализация векторных операций требует как существенного транзисторного бюджета, так и заметных затрат энергии. Но тут же возникает закономерный вопрос о том, как в этом случае будет строиться работа с этими инструкциями в процессорах Alder Lake в целом? Ответ на этот вопрос оказался очень простым – никак. Хотя в производительных ядрах Willow Cove в составе Alder Lake регистры и исполнительные устройства с 512-битной размерностью заложены в микроархитектуре, исполнение инструкций AVX-512 в них заблокировано на аппаратном уровне, чтобы не вызывать лишних коллизий при диспетчеризации потоков, работающих с такими командами. И это значит, что с появлением процессоров Alder Lake в поддерживаемых потребительскими CPU расширениях набора инструкций произошёл откат назад. Несмотря на то, что поддержка AVX-512 была реализована и в мобильных процессорах Tiger Lake, и в десктопных Rocket Lake, в новом поколении процессоров её снова не будет. В качестве некой компенсации Intel добавила в Alder Lake поддержку подмножества инструкций VNNI для решения задач, связанных с нейронными сетями. И эти инструкции, как ни странно, могут исполняться как на производительных, так и на энергоэффективных ядрах. Однако это вовсе не те инструкции VNNI, которые ранее считались частью набора AVX-512 и оперировали 512-битными регистрами. Поскольку в Alder Lake эти регистры заблокированы, инструкции VNNI в них оперируют 256-битными регистрами и как бы существуют в рамках подмножества команд AVX2. Иными словами, набор инструкций AVX2-VNNI, который реализован в Alder Lake, отличается по разрядности от введённого ранее набора AVX-512 VNNI и требует специальной поддержки со стороны ПО. По этой причине рассчитывать на то, что введённые в Alder Lake уникальные инструкции VNNI станут активно использоваться в программных продуктах, не приходится. ⇡#Производительные ядра в подробностях Наиболее важная часть процессоров Alder Lake – новые P-ядра Golden Cove. Они не только занимают на полупроводниковом кристалле самую значительную часть площади, но и несут львиную долю ответственности за производительность процессора, так как берут на себя выполнение ресурсоёмких задач переднего плана. Поэтому совершенно неудивительно, что перед разработчиками микроархитектуры Golden Cove была поставлена задача не просто создать самое быстрое из всех существующих x86-ядро, а добиться явного превосходства в удельной производительности над предшественниками. Однако речь не шла о победе любой ценой: процессоры на базе ядер Golden Cove должны иметь возможность работы в широком ассортименте устройств, начиная от ноутбуков и заканчивая серверами, а значит, помимо высокой производительности огромное значение имеет и возможность масштабирования характеристик. Например, в случае интересующих нас в первую очередь потребительских процессоров Alder Lake важную роль играет оптимизация микроархитектуры как под однопоточные нагрузки, так и под многопоточные ресурсоёмкие приложения для работы с цифровым контентом. Intel долгое время опиралась на ядро Skylake и взялась за серьёзную переделку своей самой успешной и самой долгоживущей микроархитектуры сравнительно недавно. Но, начав с вышедшей в 2019 году микроархитектуры Sunny Cove, компания принялась проводить различные улучшения непривычно бодро. Она сразу же сформулировала принцип «шире, глубже, умнее» и в соответствии с ним стала последовательно перекраивать старое ядро Skylake. Микроархитектура Golden Cove, таким образом, уже вторая итерация улучшений. И в ней мы снова видим более глубокие буферы переупорядочивания, большее количество физических регистров, более широкое окно выборки инструкций и возросшее количество исполнительных портов. К этому списку прилагается также улучшение предсказания ветвлений, что снижает простои исполнительных устройств из-за неправильного прогнозирования переходов. Сама Intel оценивает результативность внесённых в микроархитектуру изменений очень высоко. Согласно данным компании, средняя удельная производительность ядра Golden Cove (на одинаковой частоте) выше производительности ядра Cypress Cove, применяющегося в процессорах Rocket Lake, на 19 %. При этом в некоторых задачах прирост в пределах одной смены поколений может быть намного выше и достигать величины до 60 %. И всё это звучит очень многообещающе, ведь благодаря новой производственной технологии Intel 7 процессоры Alder Lake не должны отставать от предшественников и по тактовым частотам. Более того, прирост удельной производительности в каждой новой версии микроархитектуры на 19 % стал для Intel, похоже, неким стандартом. Такой же шаг вперёд был сделан при переходе от Skylake к Cypress Cove, и это значит, что показатель IPC (удельная производительность на такт) ядра Golden Cove выше, чем у Skylake, где-то на 40-45 %. В результате от Golden Cove вполне можно ожидать заметного превосходства и над конкурирующими архитектурами, в частности над Zen 3. Заметные изменения в микроархитектуре Golden Cove начинают прослеживаться уже во входной части исполнительного конвейера. В первую очередь стоит отметить увеличение числа декодеров — с 4 до 6, что даёт возможность ядру декодировать по 6 инструкций за такт. Для того чтобы декодеры не простаивали без работы, в Golden Cove с 16 до 32 байт увеличился объём выборки кода. Кроме этого, Intel поработала и в направлении повышения эффективности кеша микроопераций, где хранятся уже декодированные инструкции. Если сравнивать с Cypress Cove, то его объём увеличился с 2,25 до 4 тыс. записей, а пропускная способность выросла до 8 микроопераций за такт вместо 6. Всё это позволяет насыщать последующие после декодирования этапы исполнительного конвейера – диспетчер и планировщик – с заметно более высокой интенсивностью. Для улучшения возможности работы со сложным кодом Intel удвоила число записей, относящихся к 4K-страницам, в iTLB, а также улучшила предсказание переходов, увеличив максимальную размерность буфера целей ветвлений с 5 до 12 тысяч записей. Кроме того, этот буфер получил дополнительную интеллектуальность – основанный на машинном обучении алгоритм, способный подстраивать его вместимость под текущую нагрузку для оптимизации производительности и энергопотребления. Диспетчер, занимающийся приёмом и размещением микроопераций, а также переименованием регистров, получил возросшую ширину – в него теперь входит 6, а не 5, как раньше, равноправных блоков. Механизм внеочередного исполнения стал эффективнее за счёт увеличения соответствующего буфера с 352 до 512 записей. И в сумме всего этого оказалось вполне достаточно для загрузки работой возросшего числа исполнительных устройств, которые сгруппированы в Golden Cove в 12 портов (против 10 портов у Cypress Cove). Кроме того, Intel упомянула ещё один новый механизм, благодаря которому некоторые инструкции могут быть выполнены ещё на этапе переименования регистров, что должно дополнительно разгрузить исполнительный домен. Один из добавленных в Golden Cove исполнительных портов отдан под работу с командами ALU и LEA. Таким образом, новое ядро располагает сразу пятью целочисленными устройствами, способными исполнять по одной команде за такт. Кроме того, отдельно здесь же появились два дополнительных устройства для быстрого векторного сложения (FADD). Улучшения коснулись и L1D-кеша, который получил три порта загрузки вместо двух, имевшихся ранее, а также более вместительные буферы загрузки и выгрузки. Попутно Intel на 50 % увеличила вместимость L1 TLB. Изменения в алгоритме работы L1D затронули и предварительную выборку данных, в которой теперь используется четыре анализатора вместо двух, что должно дать эффект при работе в многопоточной среде. При этом объём L1D кеша в ядре Golden Cove останется на уровне 48 Кбайт – как и в Sunny Cove. Что касается кеш-памяти второго уровня, то в Alder Lake на каждое P-ядро будет полагаться L2-кеш объёмом 1,25 Мбайт с низкой латентностью и возможностью расширения в перспективе до 2 Мбайт. Как и в случае L1D, Intel обещает для него улучшенную предвыборку данных, основанную на выявлении шаблонов запросов к памяти. Подводя итог всему перечисленному, можно констатировать, что по сравнению с прошлым поколением микроархитектуры у ядра Golden Cove на 50 % расширился декодер, на 25 % — стадия подготовки микроопераций и на 45 % – буфер внеочередного исполнения. Плюс всё это приправлено существенными улучшениями в механизме предсказания переходов. Как перечисленные усовершенствования выглядят в численном выражении, можно посмотреть в приведённой таблице.

Остаётся лишь добавить, что в ядрах Golden Cove появился ещё один любопытный элемент – дополнительный и полностью самостоятельный микроконтроллер для управления питанием, который обеспечивает сбор телеметрии с микросекундной дискретностью, что на несколько порядков улучшает точность всего мониторинга по сравнению со старой схемой. По словам Intel, повышенная точность позволяет управлять энергопотреблением и производительностью CPU с меньшими задержками, что в конечном итоге повышает средние частоты ядра под нагрузкой без ущерба для энергопотребления и тепловыделения. Встроенный микроконтроллер для управления питанием в Golden Cove применяется впервые – подобных решений в ядрах Intel ранее не было. И он пришёлся в Alder Lake как нельзя более кстати – тот же микроконтроллер активно задействуется и в работе технологии Thread Director. ⇡#Энергоэффективные ядра в подробностяхЭнергоэффективные ядра в Alder Lake играют роль аккомпанемента для ядер Golden Cove. Они не исполняют сольных партий, но зато вместе с ними P-ядра, образно выражаясь, должны зазвучать более убедительно. E-ядра основываются на микроархитектуре Gracemont и представляют собой дальнейшее развитие процессоров Atom, хотя и ушли от них довольно далеко. Тем не менее концепция осталось той же: на первом месте в них стоит компактность и экономичность. Но при этом, по утверждению Intel, разработчикам удалось спроектировать ядра Gracemont такими, что с точки зрения удельной производительности на ватт они заметно превосходят Skylake, занимая на кристалле в четыре раза меньше места, чем P-ядра, и к тому же отличаются высокой энергоэффективностью. Согласно собственным данным Intel, полученным при однопоточной целочисленной нагрузке, в случае уравнивания энергопотребления Gracemont оказывается производительнее Skylake на 40 %, а в случае равенства производительности – потребляют на 40 % меньше. Другой показатель, который приводят разработчики, касается четырёхпоточной производительности: два ядра Skylake с поддержкой Hyper-Threading проигрывают четырём ядрам Gracemont в производительности порядка 80 % при равном потреблении, а при одинаковом быстродействии потребляют на 80 % больше энергии. Впрочем, приведённые сравнения вовсе не означают, что E-ядра процессоров Alder Lake лучше Skylake во всех отношениях. В действительности в приводимых Intel сравнениях сделано несколько допущений. Во-первых, производительность ядер сравнивается исключительно при простой целочисленной нагрузке, именно под которую, очевидно, оптимизированы ядра Gracemont. Во-вторых, в случае четырёхпоточного теста одиночным ядрам Skylake противопоставляются пары ядер Gracemont, которые Hyper-Threading не поддерживают. Но тем не менее явная сильная сторона Gracemont заключается в том, что их по производительности всё-таки можно сопоставлять с Skylake, несмотря на то, что они в разы меньше по площади. Достигнуто это за счёт глубокой переработки прошлых энергоэффективных микроархитектур Intel. В последних двух поколениях, Tremont и Gracemont, кардинально видоизменилась и стала глубже и шире входная часть исполнительного конвейера, плюс значительно выросло число исполнительных портов. Более того, в Gracemont даже добавились 256-битные регистры и исполнительные устройства для реализации наборов команд AVX2 и AVX2-VNNI. То есть E-ядра ушли от предшественников с микроархитектурой Goldmont очень далеко: не только принципиально увеличилась производительность, но и по возможностям E-ядра подтянулись к «большим» собратьям. Сдвоенный шестивходовый декодер, который способен декодировать два потока с темпом по три x86-инструкции за такт, появился ещё в ядре Tremont. Он хорошо зарекомендовал себя там, и Intel перенесла его и в Gracemont. Но в новом поколении микроархитектуры он дополнен более вместительным L1I-кешем инструкций объёмом 64 Кбайт, который даже превосходит по объёму L1I-кеш производительного ядра Golden Cove. Рост объёма кеша произошёл одновременно с увеличением до 5000 записей буфера целей ветвлений, который работает более эффективно тогда, когда цели ветвлений находятся в кеше, – это привело к повышению результативности предсказания переходов. Кроме того, на базе L1I-кеша работает ещё один механизм – «декодирование по запросу», который отчасти заменяет отсутствующий в Gracemont кеш микроопераций и частично сохраняет историю предыдущих декодирований, позволяя при ошибках в предсказании переходов избегать повторного декодирования некоторых фрагментов однажды обработанного потока инструкций. Далее, в микроархитектуре Gracemont предусмотрен пятивходовый блок размещения инструкций и восьмипортовый блок их отставки, которые работают с выросшим до 256 записей буфером переупорядочивания инструкций. А затем в конвейере находится 17 исполнительных портов – поистине гигантский по ширине исполнительный домен. И хотя все порты в данном случае заметно проще, чем в «больших» ядрах, на целочисленных инструкциях этот массив действительно может обеспечивать более высокий показатель IPC, нежели восемь портов ядра Skylake. Однако нужно понимать, что, несмотря на его ширину, одновременно в исполнительный домен Gracemont можно загружать не более пяти микроопераций за такт, и именно это ограничивает темп исполнения программного кода. В исполнительном домене Gracemont предусмотрено четыре независимых целочисленных устройства общего назначения, и два из них умеют исполнять операции умножения и деления. Кроме того, ядро имеет необходимые ресурсы, чтобы брать два перехода за такт. Для работы с векторными инструкциями и числами с плавающей точкой в Gracemont выделено три порта, два из которых способны обрабатывать операции умножения и деления. В целом конструкция исполнительного домена энергоэффективного ядра предполагает использование большого числа узкоспециализированных исполнительных портов, в то время как в производительных ядрах концепция иная. Там портов меньше, но они более универсальны и ориентированы на более разнородные операции. При работе с кеш-памятью ядро Gracemont может инициировать две операции загрузки и две операции выгрузки данных за такт, однако, в отличие от P-ядер, здесь эти операции 128-битные. Объём L1D-кеша при этом тоже меньше – всего 32 Кбайт. Отличается и организация кеш-памяти второго уровня. Её объём достигает 2 Мбайт, но он разделяется на расположенные рядом и скомпонованные в единый кластер четыре ядра. Связь L2-кеша с каждым из ядер в этой схеме осуществляется собственным 512-битным каналом. Для совместной работы ядер с L2-кешем в микроархитектуре предусмотрен специальный диспетчер, причём алгоритм его работы настроен на равномерное распределение ресурсов по ядрам, а не на обеспечение низкой латентности для каких-то отдельных потоков. И это отражает, что конструкция E-ядер в первую очередь заточена под многопоточные нагрузки. Микроархитектура Gracemont предполагает, что такие ядра компонуются в четырёхъядерные кластеры, которые занимают на полупроводниковом кристалле Alder Lake примерно столько же места, сколько одно производительное ядро Golden Cove. Это даёт возможность добавлять в современные процессоры большое количество сравнительно простых вычислителей, которые к тому же обладают очень хорошей энергоэффективностью. Для того чтобы максимально развить эту идею, Intel понизила кластерам E-ядер напряжение питания, и поэтому ядра Gracemont в составе Alder Lake будут работать на сравнительно невысокой частоте. Однако предполагается, что при необходимости их производительность можно масштабировать в широких пределах – они должны хорошо переносить повышение напряжения и отвечать на него ростом верхней границы допустимой частоты. ⇡#Настольные процессоры Alder Lake-S и платформа LGA1700 До прихода на рынок семейства процессоров Alder Lake-S, нацеленного на применение в производительных десктопах, остаётся всего несколько недель, и представить себе, как будет выглядеть соответствующий модельный ряд, можно уже сейчас. Стратегия Intel по выводу Alder Lake-S на рынок предполагает выпуск в первую очередь платформы и процессоров для энтузиастов, в то время как более массовые и доступные модификации появятся позднее. Это значит, что на рынок сначала придут настольные процессоры старших серий Core i9, Core i7 и Core i5, а также единственный флагманский чипсет Z690. Для использования в первой очереди десктопных процессоров Intel подготовила полупроводниковый кристалл с 8 ядрами Golden Cove, двумя четырёхъядерными кластерами Gracemont и графикой GT1 с 32 исполнительными устройствами. Но полностью этот арсенал будет пущен в ход исключительно в процессорах серии Core i9. Представители младших серий получат меньшее число ядер, причём разница между Core i9 и Core i7 будет определяться числом E-ядер, а в серии Core i5 будут частично отключены как P-ядра, так и E-ядра. Тактовые частоты P-ядер в Alder Lake-S, предположительно, окажутся на обычном для процессоров Intel уровне: в турборежиме они смогут брать высоту около 4,9-5,3 ГГц при однопоточной нагрузке и 4,5-5,0 ГГц – при многопоточной. Что касается E-ядер, то целевые частоты для них ожидаются в интервале 3,4-3,9 ГГц. Тепловой пакет новых процессоров также вряд ли кого-то удивит: 125 Вт – для моделей с разблокированными множителями и 65 Вт – для обычных. Зато заметно вырастет в объёме L3-кеш. В процессорах поколений Rocket Lake и Comet Lake на каждое ядро приходился блок L3-кеша объёмом 2 Мбайт. В Alder Lake объём таких блоков, примыкающих к P-ядрам, увеличился до 3 Мбайт. Также 3-Мбайт блоками оснащены и четырёхъядерные кластеры E-ядер, поэтому максимальный объём L3-кеша у старших моделей Alder Lake достигнет 30 Мбайт. Сам кеш при этом неинклюзивный, то есть в нём не дублируется содержимое вышестоящей кеш-памяти.  Отдельно следует сказать про цены. В целом Intel не планирует как-то заметно менять свою ценовую политику. И это означает, что представители серии Core i9 получат рекомендованную стоимость примерно $500-$600, процессоры Core i7 можно будет купить за $350-$450, а Core i5 будут продаваться за $200-$300. Иными словами, компания не считает, что внедрение гибридной архитектуры и добавление E-ядер заслуживает какой-то заметной наценки. Предполагаемые характеристики первых представителей серии приведены в таблице, но стоит иметь в виду, что эти данные – неофициальные и предварительные.

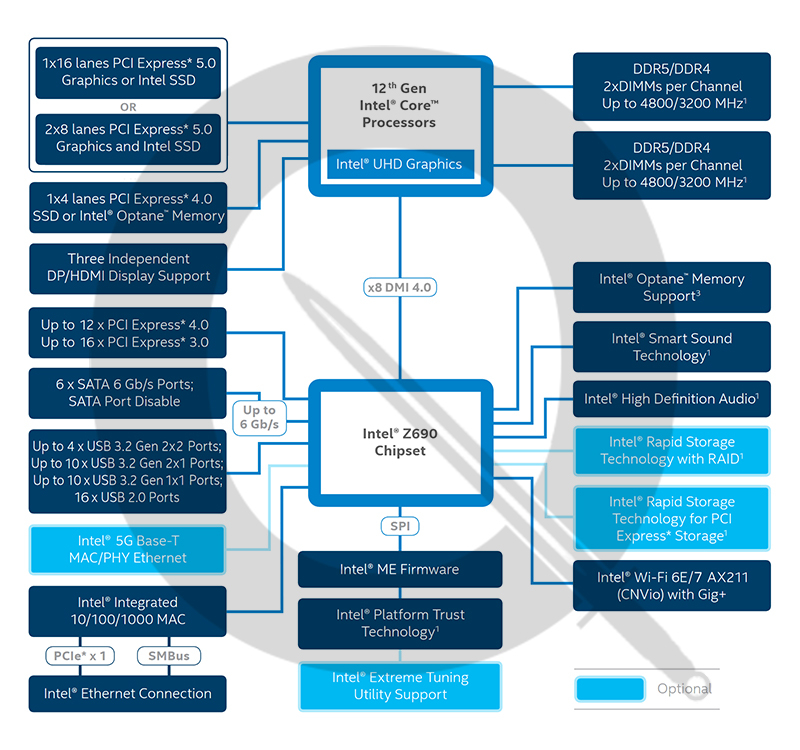

Настольные процессоры семейства Alder Lake-S рассчитаны на использование в материнских платах с новым разъёмом LGA1700, который отличается от актуального LGA1200 не только увеличенным количеством контактов, но и прямоугольной, а не квадратной формой и слегка выросшими геометрическими размерами. Изменения в первую очередь обусловлены появлением поддержки новых типов памяти и интерфейса PCIe 5.0, а во вторую – усложнившейся схемой подвода питания, поскольку P-ядра и E-ядра работают от разных напряжений. К тому же меняется и высота процессора вместе с процессорным гнездом – Alder Lake-S будет примерно на миллиметр меньше возвышаться над материнской платой, нежели предшественники. Это потребует использования для теплоотвода систем охлаждения с другими креплениями, и поэтому крепёжные отверстия в LGA1700-платах будут расположены немного иным образом – квадратом 78 × 78 мм вместо 75 × 75 мм. Таким образом, большинство кулеров от старых компьютеров для Alder Lake-S не подойдёт, по крайней мере без замены крепёжных деталей. Ввиду того, что контроллер памяти Alder Lake-S поддерживает как DDR4, так и DDR5 SDRAM, материнские платы для этих процессоров будут выпускаться со слотами DIMM либо под ту, либо под другую память. Первое время платы с поддержкой DDR5 SDRAM будут, очевидно, представлены лишь дорогими моделями, поскольку такие модули после их появления в продаже будут стоить заметно дороже, чем DDR4. Однако энтузиасты могут всё равно предпочесть платы с DDR5 DIMM, так как новая память способна обеспечить вдвое более высокую пропускную способность. Для десктопных платформ на базе Alder Lake-S компанией Intel готовится новое семейство наборов логики 600-й серии. В нём будут реализованы существенно расширенные возможности для подключения внешних устройств. Так, старший из будущих чипсетов, Z690, который придёт на рынок первым, сможет предложить даже собственные линии PCIe 4.0. В дополнение к 16 линиям PCIe 5.0 (для видеокарты) и 4 линиям PCIe 4.0 (для накопителя), за которые отвечает процессор, в системах на основе Z690 добавится 12 чипсетных линий PCIe 4.0, что в конечном итоге позволит установить в систему до четырёх самых современных NVMe-накопителей. Кроме того, в Z690 также заложена и поддержка 16 линий PCIe 3.0, то есть в общей сложности чипсет располагает 28 линиями PCIe, а платформа целиком – 48 линиями. Ещё одно важное изменение, напрямую связанное с появлением в чипсете PCIe 4.0, – перевод соединения между процессором и чипсетом на интерфейс DMI 4.0 x8 с удвоенной полосой пропускания. Это позволит обеспечить достаточную пропускную способность для работы всего набора чипсетных линий PCIe.

Набор системной логики Intel Z690. Источник: pcinq.com Среди прочих улучшений Z690 также можно отметить увеличение числа 20-гигабитных портов USB 3.2 Gen 2×2 и появление (пока только в теории) поддержки модулей Wi-Fi 7 через интерфейс CNVi.

Представить, какой уровень производительности смогут в конечном итоге предложить процессоры Alder Lake-S, сейчас довольно сложно. Никаких утечек информации на этот счёт, которым действительно можно было бы доверять, пока не было, а оценки удельной производительности микроархитектур, сделанные самим производителем, не дают конкретных ориентиров. С уверенностью можно говорить лишь об одном: Alder Lake-S будут определённо (и существенно) быстрее предшественников. Отвечают за это производительные ядра Golden Cove, и они наверняка не подведут, поскольку в них заложен целый комплекс улучшений, прямо увеличивающий производительность. Число таких ядер будет не меньше, чем в Rocket Lake, не снизятся и тактовые частоты. Однако не стоит забывать, что с ядрами Golden Cove в будущих процессорах соседствуют и энергоэффективные ядра Gracemont, которые тоже выглядят довольно неплохо, но как будет вести себя в реальности гибридная архитектура, спрогнозировать довольно сложно. Intel уверяет, что современные операционные системы в состоянии разобраться с разнотипными ядрами, но на деле всё это нуждается в доскональной проверке. Кроме того, коррективы в производительность платформы может внести и DDR5 SDRAM. Часто переход на новые типы памяти с более высокой пропускной способностью оборачивается серьёзным увеличением задержек, и переход от DDR4 к DDR5 – как раз такой случай. Поэтому пока мы воздержимся от каких-либо прогнозов и будем с нетерпением ждать конца октября, когда Intel должна раскрыть дополнительные подробности о перспективном семействе CPU. Главный же вывод, который нужно сделать сегодня, – качественный: Intel вышла из многолетней спячки и запустила процесс интенсификации инноваций. Прогресс, достигнутый в настольном сегменте, не может не впечатлить. Семейство чипов Rocket Lake, в котором нашли применение ядра Cypress Cove, пришло на рынок всего шесть месяцев тому назад, но сегодня мы уже говорим об их последователях – ядрах Golden Cove и принципиально новых процессорах Alder Lake-S. И более того, теперь компания уже не собирается останавливаться. Уже в конце следующего года она планирует представить последующее большое обновление потребительской платформы вместе с процессорами Meteor Lake, где число нововведений будет точно не меньшим, чем в Alder Lake. В нём Intel начнёт применять тайловую (многочиповую) топологию, полупроводниковые кристаллы, выпущенные по технологии Intel 4, и новые итерации процессорных микроархитектур. Так что посвящённые новым процессорным дизайнам статьи, подобные этой, будут теперь выходить на нашем сайте заметно чаще.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|