⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Объясняем, почему Intel Alder Lake — главный процессор этой осени

⇡#Производительные ядра в подробностях Наиболее важная часть процессоров Alder Lake – новые P-ядра Golden Cove. Они не только занимают на полупроводниковом кристалле самую значительную часть площади, но и несут львиную долю ответственности за производительность процессора, так как берут на себя выполнение ресурсоёмких задач переднего плана. Поэтому совершенно неудивительно, что перед разработчиками микроархитектуры Golden Cove была поставлена задача не просто создать самое быстрое из всех существующих x86-ядро, а добиться явного превосходства в удельной производительности над предшественниками. Однако речь не шла о победе любой ценой: процессоры на базе ядер Golden Cove должны иметь возможность работы в широком ассортименте устройств, начиная от ноутбуков и заканчивая серверами, а значит, помимо высокой производительности огромное значение имеет и возможность масштабирования характеристик. Например, в случае интересующих нас в первую очередь потребительских процессоров Alder Lake важную роль играет оптимизация микроархитектуры как под однопоточные нагрузки, так и под многопоточные ресурсоёмкие приложения для работы с цифровым контентом. Intel долгое время опиралась на ядро Skylake и взялась за серьёзную переделку своей самой успешной и самой долгоживущей микроархитектуры сравнительно недавно. Но, начав с вышедшей в 2019 году микроархитектуры Sunny Cove, компания принялась проводить различные улучшения непривычно бодро. Она сразу же сформулировала принцип «шире, глубже, умнее» и в соответствии с ним стала последовательно перекраивать старое ядро Skylake. Микроархитектура Golden Cove, таким образом, уже вторая итерация улучшений. И в ней мы снова видим более глубокие буферы переупорядочивания, большее количество физических регистров, более широкое окно выборки инструкций и возросшее количество исполнительных портов. К этому списку прилагается также улучшение предсказания ветвлений, что снижает простои исполнительных устройств из-за неправильного прогнозирования переходов. Сама Intel оценивает результативность внесённых в микроархитектуру изменений очень высоко. Согласно данным компании, средняя удельная производительность ядра Golden Cove (на одинаковой частоте) выше производительности ядра Cypress Cove, применяющегося в процессорах Rocket Lake, на 19 %. При этом в некоторых задачах прирост в пределах одной смены поколений может быть намного выше и достигать величины до 60 %. И всё это звучит очень многообещающе, ведь благодаря новой производственной технологии Intel 7 процессоры Alder Lake не должны отставать от предшественников и по тактовым частотам. Более того, прирост удельной производительности в каждой новой версии микроархитектуры на 19 % стал для Intel, похоже, неким стандартом. Такой же шаг вперёд был сделан при переходе от Skylake к Cypress Cove, и это значит, что показатель IPC (удельная производительность на такт) ядра Golden Cove выше, чем у Skylake, где-то на 40-45 %. В результате от Golden Cove вполне можно ожидать заметного превосходства и над конкурирующими архитектурами, в частности над Zen 3. Заметные изменения в микроархитектуре Golden Cove начинают прослеживаться уже во входной части исполнительного конвейера. В первую очередь стоит отметить увеличение числа декодеров — с 4 до 6, что даёт возможность ядру декодировать по 6 инструкций за такт. Для того чтобы декодеры не простаивали без работы, в Golden Cove с 16 до 32 байт увеличился объём выборки кода. Кроме этого, Intel поработала и в направлении повышения эффективности кеша микроопераций, где хранятся уже декодированные инструкции. Если сравнивать с Cypress Cove, то его объём увеличился с 2,25 до 4 тыс. записей, а пропускная способность выросла до 8 микроопераций за такт вместо 6. Всё это позволяет насыщать последующие после декодирования этапы исполнительного конвейера – диспетчер и планировщик – с заметно более высокой интенсивностью. Для улучшения возможности работы со сложным кодом Intel удвоила число записей, относящихся к 4K-страницам, в iTLB, а также улучшила предсказание переходов, увеличив максимальную размерность буфера целей ветвлений с 5 до 12 тысяч записей. Кроме того, этот буфер получил дополнительную интеллектуальность – основанный на машинном обучении алгоритм, способный подстраивать его вместимость под текущую нагрузку для оптимизации производительности и энергопотребления. Диспетчер, занимающийся приёмом и размещением микроопераций, а также переименованием регистров, получил возросшую ширину – в него теперь входит 6, а не 5, как раньше, равноправных блоков. Механизм внеочередного исполнения стал эффективнее за счёт увеличения соответствующего буфера с 352 до 512 записей. И в сумме всего этого оказалось вполне достаточно для загрузки работой возросшего числа исполнительных устройств, которые сгруппированы в Golden Cove в 12 портов (против 10 портов у Cypress Cove). Кроме того, Intel упомянула ещё один новый механизм, благодаря которому некоторые инструкции могут быть выполнены ещё на этапе переименования регистров, что должно дополнительно разгрузить исполнительный домен. Один из добавленных в Golden Cove исполнительных портов отдан под работу с командами ALU и LEA. Таким образом, новое ядро располагает сразу пятью целочисленными устройствами, способными исполнять по одной команде за такт. Кроме того, отдельно здесь же появились два дополнительных устройства для быстрого векторного сложения (FADD). Улучшения коснулись и L1D-кеша, который получил три порта загрузки вместо двух, имевшихся ранее, а также более вместительные буферы загрузки и выгрузки. Попутно Intel на 50 % увеличила вместимость L1 TLB. Изменения в алгоритме работы L1D затронули и предварительную выборку данных, в которой теперь используется четыре анализатора вместо двух, что должно дать эффект при работе в многопоточной среде. При этом объём L1D кеша в ядре Golden Cove останется на уровне 48 Кбайт – как и в Sunny Cove. Что касается кеш-памяти второго уровня, то в Alder Lake на каждое P-ядро будет полагаться L2-кеш объёмом 1,25 Мбайт с низкой латентностью и возможностью расширения в перспективе до 2 Мбайт. Как и в случае L1D, Intel обещает для него улучшенную предвыборку данных, основанную на выявлении шаблонов запросов к памяти. Подводя итог всему перечисленному, можно констатировать, что по сравнению с прошлым поколением микроархитектуры у ядра Golden Cove на 50 % расширился декодер, на 25 % — стадия подготовки микроопераций и на 45 % – буфер внеочередного исполнения. Плюс всё это приправлено существенными улучшениями в механизме предсказания переходов. Как перечисленные усовершенствования выглядят в численном выражении, можно посмотреть в приведённой таблице.

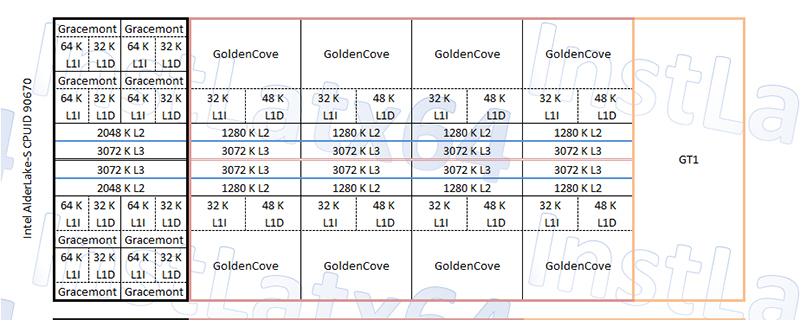

Остаётся лишь добавить, что в ядрах Golden Cove появился ещё один любопытный элемент – дополнительный и полностью самостоятельный микроконтроллер для управления питанием, который обеспечивает сбор телеметрии с микросекундной дискретностью, что на несколько порядков улучшает точность всего мониторинга по сравнению со старой схемой. По словам Intel, повышенная точность позволяет управлять энергопотреблением и производительностью CPU с меньшими задержками, что в конечном итоге повышает средние частоты ядра под нагрузкой без ущерба для энергопотребления и тепловыделения. Встроенный микроконтроллер для управления питанием в Golden Cove применяется впервые – подобных решений в ядрах Intel ранее не было. И он пришёлся в Alder Lake как нельзя более кстати – тот же микроконтроллер активно задействуется и в работе технологии Thread Director. ⇡#Энергоэффективные ядра в подробностяхЭнергоэффективные ядра в Alder Lake играют роль аккомпанемента для ядер Golden Cove. Они не исполняют сольных партий, но зато вместе с ними P-ядра, образно выражаясь, должны зазвучать более убедительно. E-ядра основываются на микроархитектуре Gracemont и представляют собой дальнейшее развитие процессоров Atom, хотя и ушли от них довольно далеко. Тем не менее концепция осталось той же: на первом месте в них стоит компактность и экономичность. Но при этом, по утверждению Intel, разработчикам удалось спроектировать ядра Gracemont такими, что с точки зрения удельной производительности на ватт они заметно превосходят Skylake, занимая на кристалле в четыре раза меньше места, чем P-ядра, и к тому же отличаются высокой энергоэффективностью. Согласно собственным данным Intel, полученным при однопоточной целочисленной нагрузке, в случае уравнивания энергопотребления Gracemont оказывается производительнее Skylake на 40 %, а в случае равенства производительности – потребляют на 40 % меньше. Другой показатель, который приводят разработчики, касается четырёхпоточной производительности: два ядра Skylake с поддержкой Hyper-Threading проигрывают четырём ядрам Gracemont в производительности порядка 80 % при равном потреблении, а при одинаковом быстродействии потребляют на 80 % больше энергии. Впрочем, приведённые сравнения вовсе не означают, что E-ядра процессоров Alder Lake лучше Skylake во всех отношениях. В действительности в приводимых Intel сравнениях сделано несколько допущений. Во-первых, производительность ядер сравнивается исключительно при простой целочисленной нагрузке, именно под которую, очевидно, оптимизированы ядра Gracemont. Во-вторых, в случае четырёхпоточного теста одиночным ядрам Skylake противопоставляются пары ядер Gracemont, которые Hyper-Threading не поддерживают. Но тем не менее явная сильная сторона Gracemont заключается в том, что их по производительности всё-таки можно сопоставлять с Skylake, несмотря на то, что они в разы меньше по площади. Достигнуто это за счёт глубокой переработки прошлых энергоэффективных микроархитектур Intel. В последних двух поколениях, Tremont и Gracemont, кардинально видоизменилась и стала глубже и шире входная часть исполнительного конвейера, плюс значительно выросло число исполнительных портов. Более того, в Gracemont даже добавились 256-битные регистры и исполнительные устройства для реализации наборов команд AVX2 и AVX2-VNNI. То есть E-ядра ушли от предшественников с микроархитектурой Goldmont очень далеко: не только принципиально увеличилась производительность, но и по возможностям E-ядра подтянулись к «большим» собратьям. Сдвоенный шестивходовый декодер, который способен декодировать два потока с темпом по три x86-инструкции за такт, появился ещё в ядре Tremont. Он хорошо зарекомендовал себя там, и Intel перенесла его и в Gracemont. Но в новом поколении микроархитектуры он дополнен более вместительным L1I-кешем инструкций объёмом 64 Кбайт, который даже превосходит по объёму L1I-кеш производительного ядра Golden Cove. Рост объёма кеша произошёл одновременно с увеличением до 5000 записей буфера целей ветвлений, который работает более эффективно тогда, когда цели ветвлений находятся в кеше, – это привело к повышению результативности предсказания переходов. Кроме того, на базе L1I-кеша работает ещё один механизм – «декодирование по запросу», который отчасти заменяет отсутствующий в Gracemont кеш микроопераций и частично сохраняет историю предыдущих декодирований, позволяя при ошибках в предсказании переходов избегать повторного декодирования некоторых фрагментов однажды обработанного потока инструкций. Далее, в микроархитектуре Gracemont предусмотрен пятивходовый блок размещения инструкций и восьмипортовый блок их отставки, которые работают с выросшим до 256 записей буфером переупорядочивания инструкций. А затем в конвейере находится 17 исполнительных портов – поистине гигантский по ширине исполнительный домен. И хотя все порты в данном случае заметно проще, чем в «больших» ядрах, на целочисленных инструкциях этот массив действительно может обеспечивать более высокий показатель IPC, нежели восемь портов ядра Skylake. Однако нужно понимать, что, несмотря на его ширину, одновременно в исполнительный домен Gracemont можно загружать не более пяти микроопераций за такт, и именно это ограничивает темп исполнения программного кода. В исполнительном домене Gracemont предусмотрено четыре независимых целочисленных устройства общего назначения, и два из них умеют исполнять операции умножения и деления. Кроме того, ядро имеет необходимые ресурсы, чтобы брать два перехода за такт. Для работы с векторными инструкциями и числами с плавающей точкой в Gracemont выделено три порта, два из которых способны обрабатывать операции умножения и деления. В целом конструкция исполнительного домена энергоэффективного ядра предполагает использование большого числа узкоспециализированных исполнительных портов, в то время как в производительных ядрах концепция иная. Там портов меньше, но они более универсальны и ориентированы на более разнородные операции. При работе с кеш-памятью ядро Gracemont может инициировать две операции загрузки и две операции выгрузки данных за такт, однако, в отличие от P-ядер, здесь эти операции 128-битные. Объём L1D-кеша при этом тоже меньше – всего 32 Кбайт. Отличается и организация кеш-памяти второго уровня. Её объём достигает 2 Мбайт, но он разделяется на расположенные рядом и скомпонованные в единый кластер четыре ядра. Связь L2-кеша с каждым из ядер в этой схеме осуществляется собственным 512-битным каналом. Для совместной работы ядер с L2-кешем в микроархитектуре предусмотрен специальный диспетчер, причём алгоритм его работы настроен на равномерное распределение ресурсов по ядрам, а не на обеспечение низкой латентности для каких-то отдельных потоков. И это отражает, что конструкция E-ядер в первую очередь заточена под многопоточные нагрузки. Микроархитектура Gracemont предполагает, что такие ядра компонуются в четырёхъядерные кластеры, которые занимают на полупроводниковом кристалле Alder Lake примерно столько же места, сколько одно производительное ядро Golden Cove. Это даёт возможность добавлять в современные процессоры большое количество сравнительно простых вычислителей, которые к тому же обладают очень хорошей энергоэффективностью. Для того чтобы максимально развить эту идею, Intel понизила кластерам E-ядер напряжение питания, и поэтому ядра Gracemont в составе Alder Lake будут работать на сравнительно невысокой частоте. Однако предполагается, что при необходимости их производительность можно масштабировать в широких пределах – они должны хорошо переносить повышение напряжения и отвечать на него ростом верхней границы допустимой частоты. ⇡#Настольные процессоры Alder Lake-S и платформа LGA1700 До прихода на рынок семейства процессоров Alder Lake-S, нацеленного на применение в производительных десктопах, остаётся всего несколько недель, и представить себе, как будет выглядеть соответствующий модельный ряд, можно уже сейчас. Стратегия Intel по выводу Alder Lake-S на рынок предполагает выпуск в первую очередь платформы и процессоров для энтузиастов, в то время как более массовые и доступные модификации появятся позднее. Это значит, что на рынок сначала придут настольные процессоры старших серий Core i9, Core i7 и Core i5, а также единственный флагманский чипсет Z690. Для использования в первой очереди десктопных процессоров Intel подготовила полупроводниковый кристалл с 8 ядрами Golden Cove, двумя четырёхъядерными кластерами Gracemont и графикой GT1 с 32 исполнительными устройствами. Но полностью этот арсенал будет пущен в ход исключительно в процессорах серии Core i9. Представители младших серий получат меньшее число ядер, причём разница между Core i9 и Core i7 будет определяться числом E-ядер, а в серии Core i5 будут частично отключены как P-ядра, так и E-ядра. Тактовые частоты P-ядер в Alder Lake-S, предположительно, окажутся на обычном для процессоров Intel уровне: в турборежиме они смогут брать высоту около 4,9-5,3 ГГц при однопоточной нагрузке и 4,5-5,0 ГГц – при многопоточной. Что касается E-ядер, то целевые частоты для них ожидаются в интервале 3,4-3,9 ГГц. Тепловой пакет новых процессоров также вряд ли кого-то удивит: 125 Вт – для моделей с разблокированными множителями и 65 Вт – для обычных. Зато заметно вырастет в объёме L3-кеш. В процессорах поколений Rocket Lake и Comet Lake на каждое ядро приходился блок L3-кеша объёмом 2 Мбайт. В Alder Lake объём таких блоков, примыкающих к P-ядрам, увеличился до 3 Мбайт. Также 3-Мбайт блоками оснащены и четырёхъядерные кластеры E-ядер, поэтому максимальный объём L3-кеша у старших моделей Alder Lake достигнет 30 Мбайт. Сам кеш при этом неинклюзивный, то есть в нём не дублируется содержимое вышестоящей кеш-памяти.  Отдельно следует сказать про цены. В целом Intel не планирует как-то заметно менять свою ценовую политику. И это означает, что представители серии Core i9 получат рекомендованную стоимость примерно $500-$600, процессоры Core i7 можно будет купить за $350-$450, а Core i5 будут продаваться за $200-$300. Иными словами, компания не считает, что внедрение гибридной архитектуры и добавление E-ядер заслуживает какой-то заметной наценки. Предполагаемые характеристики первых представителей серии приведены в таблице, но стоит иметь в виду, что эти данные – неофициальные и предварительные.

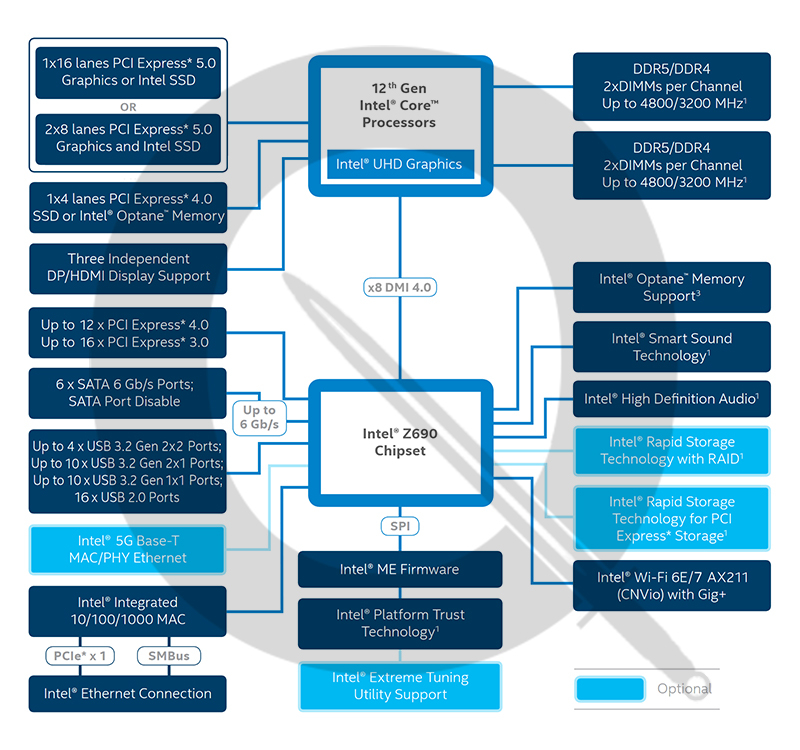

Настольные процессоры семейства Alder Lake-S рассчитаны на использование в материнских платах с новым разъёмом LGA1700, который отличается от актуального LGA1200 не только увеличенным количеством контактов, но и прямоугольной, а не квадратной формой и слегка выросшими геометрическими размерами. Изменения в первую очередь обусловлены появлением поддержки новых типов памяти и интерфейса PCIe 5.0, а во вторую – усложнившейся схемой подвода питания, поскольку P-ядра и E-ядра работают от разных напряжений. К тому же меняется и высота процессора вместе с процессорным гнездом – Alder Lake-S будет примерно на миллиметр меньше возвышаться над материнской платой, нежели предшественники. Это потребует использования для теплоотвода систем охлаждения с другими креплениями, и поэтому крепёжные отверстия в LGA1700-платах будут расположены немного иным образом – квадратом 78 × 78 мм вместо 75 × 75 мм. Таким образом, большинство кулеров от старых компьютеров для Alder Lake-S не подойдёт, по крайней мере без замены крепёжных деталей. Ввиду того, что контроллер памяти Alder Lake-S поддерживает как DDR4, так и DDR5 SDRAM, материнские платы для этих процессоров будут выпускаться со слотами DIMM либо под ту, либо под другую память. Первое время платы с поддержкой DDR5 SDRAM будут, очевидно, представлены лишь дорогими моделями, поскольку такие модули после их появления в продаже будут стоить заметно дороже, чем DDR4. Однако энтузиасты могут всё равно предпочесть платы с DDR5 DIMM, так как новая память способна обеспечить вдвое более высокую пропускную способность. Для десктопных платформ на базе Alder Lake-S компанией Intel готовится новое семейство наборов логики 600-й серии. В нём будут реализованы существенно расширенные возможности для подключения внешних устройств. Так, старший из будущих чипсетов, Z690, который придёт на рынок первым, сможет предложить даже собственные линии PCIe 4.0. В дополнение к 16 линиям PCIe 5.0 (для видеокарты) и 4 линиям PCIe 4.0 (для накопителя), за которые отвечает процессор, в системах на основе Z690 добавится 12 чипсетных линий PCIe 4.0, что в конечном итоге позволит установить в систему до четырёх самых современных NVMe-накопителей. Кроме того, в Z690 также заложена и поддержка 16 линий PCIe 3.0, то есть в общей сложности чипсет располагает 28 линиями PCIe, а платформа целиком – 48 линиями. Ещё одно важное изменение, напрямую связанное с появлением в чипсете PCIe 4.0, – перевод соединения между процессором и чипсетом на интерфейс DMI 4.0 x8 с удвоенной полосой пропускания. Это позволит обеспечить достаточную пропускную способность для работы всего набора чипсетных линий PCIe.

Набор системной логики Intel Z690. Источник: pcinq.com Среди прочих улучшений Z690 также можно отметить увеличение числа 20-гигабитных портов USB 3.2 Gen 2×2 и появление (пока только в теории) поддержки модулей Wi-Fi 7 через интерфейс CNVi.

Представить, какой уровень производительности смогут в конечном итоге предложить процессоры Alder Lake-S, сейчас довольно сложно. Никаких утечек информации на этот счёт, которым действительно можно было бы доверять, пока не было, а оценки удельной производительности микроархитектур, сделанные самим производителем, не дают конкретных ориентиров. С уверенностью можно говорить лишь об одном: Alder Lake-S будут определённо (и существенно) быстрее предшественников. Отвечают за это производительные ядра Golden Cove, и они наверняка не подведут, поскольку в них заложен целый комплекс улучшений, прямо увеличивающий производительность. Число таких ядер будет не меньше, чем в Rocket Lake, не снизятся и тактовые частоты. Однако не стоит забывать, что с ядрами Golden Cove в будущих процессорах соседствуют и энергоэффективные ядра Gracemont, которые тоже выглядят довольно неплохо, но как будет вести себя в реальности гибридная архитектура, спрогнозировать довольно сложно. Intel уверяет, что современные операционные системы в состоянии разобраться с разнотипными ядрами, но на деле всё это нуждается в доскональной проверке. Кроме того, коррективы в производительность платформы может внести и DDR5 SDRAM. Часто переход на новые типы памяти с более высокой пропускной способностью оборачивается серьёзным увеличением задержек, и переход от DDR4 к DDR5 – как раз такой случай. Поэтому пока мы воздержимся от каких-либо прогнозов и будем с нетерпением ждать конца октября, когда Intel должна раскрыть дополнительные подробности о перспективном семействе CPU. Главный же вывод, который нужно сделать сегодня, – качественный: Intel вышла из многолетней спячки и запустила процесс интенсификации инноваций. Прогресс, достигнутый в настольном сегменте, не может не впечатлить. Семейство чипов Rocket Lake, в котором нашли применение ядра Cypress Cove, пришло на рынок всего шесть месяцев тому назад, но сегодня мы уже говорим об их последователях – ядрах Golden Cove и принципиально новых процессорах Alder Lake-S. И более того, теперь компания уже не собирается останавливаться. Уже в конце следующего года она планирует представить последующее большое обновление потребительской платформы вместе с процессорами Meteor Lake, где число нововведений будет точно не меньшим, чем в Alder Lake. В нём Intel начнёт применять тайловую (многочиповую) топологию, полупроводниковые кристаллы, выпущенные по технологии Intel 4, и новые итерации процессорных микроархитектур. Так что посвящённые новым процессорным дизайнам статьи, подобные этой, будут теперь выходить на нашем сайте заметно чаще.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|