Организация JEDEC, отвечающая за определение спецификаций стандартных типов памяти, завершает разработку SPHBM4 (Standard Package High Bandwidth Memory) — нового стандарта памяти, предназначенного для обеспечения полной пропускной способности уровня HBM4 с «узким» 512-битным интерфейсом, большей ёмкостью и более низкими затратами на интеграцию за счёт совместимости с традиционными текстолитовыми подложками. Если эта технология получит широкое распространение, она заполнит многие пробелы на рынках, которые могла бы обслуживать HBM.

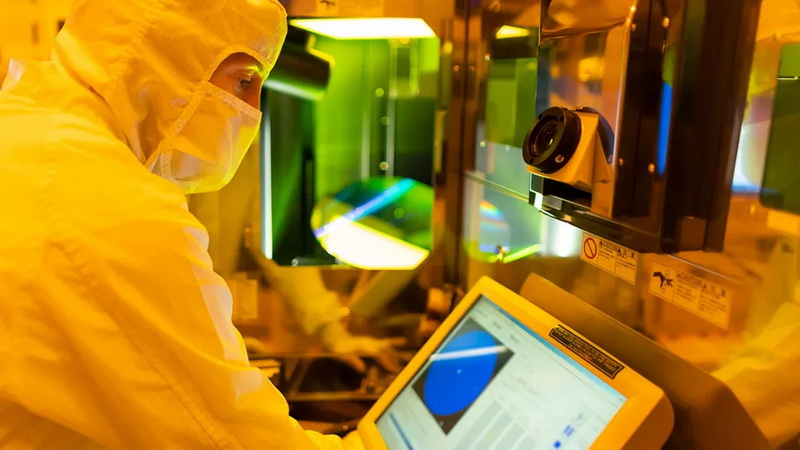

Источник изображения: Micron

Хотя чипы HBM с 1024-битным или 2048-битным интерфейсом обеспечивают непревзойдённую производительность и энергоэффективность, для интеграции они требуют много ценного кремниевого пространства внутри высокопроизводительных процессоров, что ограничивает количество стеков HBM на чипе и, следовательно, ёмкость памяти, поддерживаемую ИИ-ускорителями, влияя как на производительность отдельных ускорителей, так и на возможности больших кластеров, использующих их.

В стандартном корпусе SPHBM4 эта проблема решается за счёт уменьшения ширины интерфейса с 2048 бит до 512 бит с сериализацией 4:1 для сохранения той же пропускной способности. JEDEC не уточняет, означает ли «сериализация 4:1» учетверение скорости передачи данных с 8 ГТ/с в HBM4 или введение новой схемы кодирования с более высокими тактовыми частотами. Тем не менее, цель очевидна: сохранить суммарную пропускную способность HBM4, но в условиях 512-битного интерфейса.

Внутри корпусов SPHBM4 будет использоваться стандартный базовый кристалл HBM4, что упростит разработку контроллера (по крайней мере, на логическом уровне) и гарантирует, что ёмкость на стек останется на уровне HBM4 и HBM4E (64 Гбайт на стек HBM4E), интерфейс которого будет конвертирован в более узкую шину. На бумаге это означает возможность четырёхкратного увеличения ёмкости памяти SPHBM4 по сравнению с HBM4, но на практике разработчики чипов для ИИ, вероятно, будут балансировать между ёмкостью памяти с более высокими вычислительными возможностями и универсальностью, поскольку площадь кремниевых кристаллов становится дороже с каждой новым процессом технологической обработки.

Почему не использовать память SPHBM4 в составе игровых видеокарт, обеспечив тем самым для последних более высокую пропускную способность при умеренном увеличении стоимости по сравнению с GDDR7 или потенциальной GDDR7X с кодированием PAM4?

Разработанная для обеспечения пропускной способности уровня HBM4, память SPHBM4 принципиально спроектирована таким образом, чтобы отдавать приоритет производительности и ёмкости перед другими соображениями, такими как энергопотребление и стоимость. Хотя SPHBM4 дешевле, чем HBM4 или HBM4E, она всё ещё требует многослойной компоновки кристаллов, которые физически больше и, следовательно, дороже, чем стандартные микросхемы DRAM, базового кристалла интерфейса, обработки TSV, проверенных технологических процессов изготовления кристаллов и усовершенствованной сборки в корпусе. Эти этапы доминируют в стоимости и плохо масштабируются с увеличением объёма производства по сравнению со стандартной GDDR7, которая выигрывает от огромных объёмов потребительского и игрового рынка, простых корпусов и отработанной сборки печатных плат. Замена множества чипов GDDR7 на один усовершенствованный SPHBM4 может не снизить затраты, а, наоборот, увеличить их.

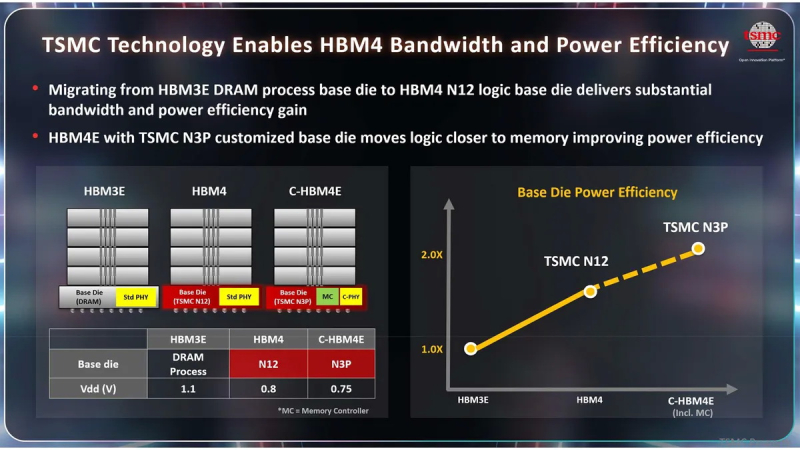

Хотя 512-битная шина памяти остаётся сложным интерфейсом, JEDEC утверждает, что SPHBM4 обеспечивает 2.5D интеграцию на обычных текстолитовых подложках и не требует дорогостоящих межсоединений, что значительно снижает затраты на интеграцию и потенциально расширяет гибкость проектирования. Между тем, благодаря стандартному 512-битному интерфейсу, SPHBM4 может предложить более низкую стоимость (благодаря объёму производства, обеспечиваемому стандартизацией) по сравнению с решениями C-HBM4E, которые используют интерфейсы UCIe или собственные разработки.

По сравнению с решениями на основе кремния, трассировка на тектолитовой подложке позволяет использовать более длинные электрические каналы между SoC и стеками памяти, что потенциально снижает ограничения по компоновке в больших корпусах и позволяет разместить большую ёмкость памяти вблизи корпуса, чем это возможно в настоящее время.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018