⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Производство CPU. Планы на 2003-2007-й год

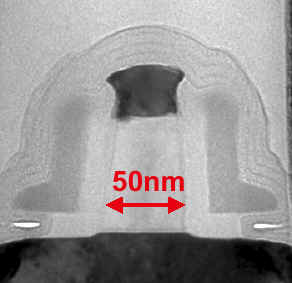

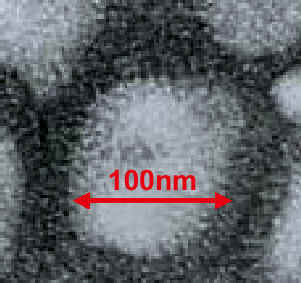

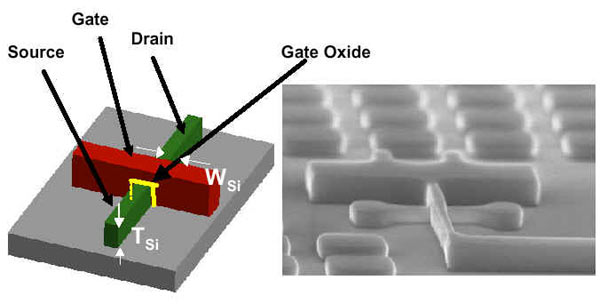

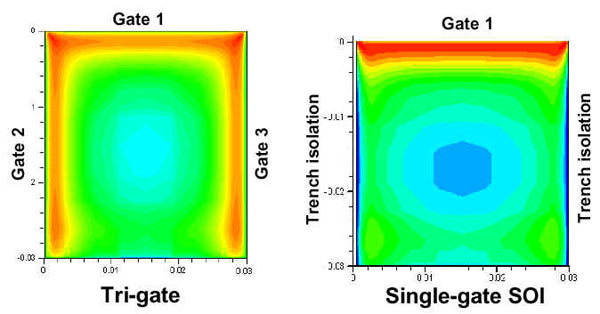

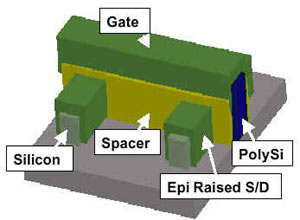

Планы IntelА вот теперь можно и вернуться к Intel. На сегодняшний день, базовым для компании является техпроцесс с элементами размерностью в 130 нм (ширина затвора транзистора - 60 нм), на основе ультрафиолетовой литографии с комбинацией длин волн в 248 и 193 нм (используется для критических участков чипа). Еще нельзя сказать, чтобы компания перешла на 300 мм пластины - на сегодняшний день подавляющее большинство фабрик компании все еще использует 200 мм, а 300 мм фабрики главным образом будут отданы уже под 90 нм чипы. Когда обладаешь таким количеством фабрик, то их техническое перевооружение отнимает массу времени и денег, и самым совершенным техпроцессом всегда будут обладать всего лишь одна-две фабрики. Даже несмотря на то, что 300 мм пластины обладают явным экономическим преимуществом, увеличивая выход годных чипов с пластины по сравнению с 200 мм, по данным Intel, в 2.25-2.5 раз, выход чипов вообще с фабрики, при производстве одних и тех же чипов - в 1.6-2.2 раза, при одинаковой стоимости фабрик. Итого, конечная себестоимость чипа, в среднем, уменьшается на 30 процентов. Впрочем, основные вещи от диаметра пластин все же не зависят - шесть слоев металлизированных проводников везде остаются неизменными, везде остаются медными: с алюминием, бывшим безальтернативным выбором в начале 90-х, уже давно распрощались все крупные производители чипов. Точно так же, как стандартом для любого последнего процессора Intel остается упаковка FCPGA. Впрочем, некоторые изменения здесь произойдут уже в этом году, с переходом на 90 нм техпроцесс. Впрочем об особых изменениях здесь речи не идет, достаточно сказать, что Intel намерен сохранить при переходе от 130 до 90 нм порядка трех четвертей всего используемого оборудования (речь идет о том 130 нм техпроцессе, который используется с 300 мм пластинами, разумеется). Еще бы - учитывая количество фабрик, которые с течением времени придется на него переводить.   90 нм транзистор и вирус гриппа Структура транзистора изменится несколько больше. Не в количественном выражении - ширина канала уменьшится всего лишь с 60 до 50 нм, поскольку токи утечки уже при 130 нм техпроцессе начали становиться настоящим бичом новых процессоров, а они, при прочих равных, прямо зависят от ширины канала, которая, в свою очередь, связана со скоростью и размером транзисторов. Пытаясь, при сохранении положительных эффектов изменений, нивелировать их отрицательные стороны, Intel в своем 90 нм техпроцессе начал использовать такие вещи, как "растянутый кремний", очень тонкий слой оксида в затворе, и новый Low-k диэлектрик для изоляции медных соединений - обогащенный углеродом оксид. Очень тонкий слой оксида действительно очень тонкий - 1.2 нм, что полностью соответствует уже известному нам правилу, что его толщина должна составлять 1/45 от глубины канала, которая у 90 нм транзистора примерно равна ширине. Но ведь выше уже шла речь об ограничении в 2.3 нм. Ну что же, очевидно, что если поверить Intel, утверждающему, что он продолжает использовать SiO2, то компании пришлось предпринять какие-то действия, позволившие повысить его изолирующие способности, возможно, сжав кристаллическую решетку. В будущем, впрочем, компания перейдет к более радикальным мерам, но об этом чуть позже. Растянутый кремний. Его задача целиком и полностью противоположна предыдущей. Если слой оксида предназначен для предотвращения прохода по нему электронов, то прямо под ним находится тот самый переход по которому электроды, при открытом затворе, перемещаются с эмиттера на коллектор. И вот тут то требуется, чтобы ток был максимально большим, чтобы электроны совершали этот путь максимально легко и быстро. Обычно материалом канала служит кремний, но в данном случае его еще и "растянули", сделав так, что атомы изначальной кристаллической решетки разошлись на большее расстояние друг от друга. Очевидно, что чем больше пространство между атомами материала, тем меньшее сопротивление испытывают проходящие сквозь него электроны. По утверждению Intel, результат применения растянутого кремния выражается в увеличении рабочего тока на 10-20 процентов, причем за счет возрастания себестоимости всего на 2 процента. Еще одним дополнительным моментом в 90 нм техпроцессе стал седьмой слой металлических (медных) проводников, обеспечивающий большую гибкость при создании комплексных процессоров, состоящих из более чем ста миллионов транзисторов, вроде того же Prescott. Но тут все совсем понятно и очевидно, и не нуждается ни в каких дополнениях. Разве что только то, что здесь Intel традиционно на шаг отстает от наиболее передовых техпроцессов. В то время, когда ведущие производители предлагали техпроцессы с семью слоями металлизации, компания в своем 130 нм использовала шесть. Сейчас Intel будет использовать семь - а компании вроде IBM уже объявили техпроцессы с восемью.  Это, правда, шесть слоев, но, зато - красиво. ;) Надо лишь добавить, что по мере уменьшения транзисторов и, соответственно, увеличения их количества в процессоре, ситуация с металлическими проводниками между ними, начинает играть все более важную роль, в частности, уже с их емкостью, влияющей на скорость передачи информации. В своем 90 нм техпроцессе Intel начал применять новый диэлектрик между соединениями - на смену SiOF пришел обогащенный углеродом оксид, по утверждению Intel, увеличивающий эффективность их работы на 18 процентов. Prescott еще только предстоит пойти в массовое производство, пока же Intel демонстрирует свои новые возможности на SRAM, являющейся, впрочем, основой одного из ключевых элементов сегодняшних процессоров - кэш-памяти. С помощью 90 нм техпроцесса компании удалось поставить новый рекорд, разместив 6-транзисторную ячейку SRAM на площади всего лишь в один квадратный микрон, что дает 52 Мбит для чипа с размерами 10х11 мм, состоящего из 330 миллионов транзисторов, почти в 8 раз больше, чем число транзисторов в Pentium 4. Таким образом, 8 Мбит кэша второго уровня у Prescott будут располагаться на площади всего лишь около 4х4 мм!  Тот самый СРАМ :) Таким для Intel является настоящее, а что же ждет нас в будущем? В первую очередь, конечно же, движение по привычному пути развития, выжимая остатки возможного из кремниевых транзисторов - то, что в Intel называется TeraHertz Transistor. Несмотря на то, что даже сегодняшние технологии позволяют в единичном экземпляре произвести транзистор с размерностью всего лишь в 15 нм, очевидно, что при том количестве транзисторов, которое подразумевают такие размеры, энергопотребление и тепловыделение чипа в целом, а также суммарный ток утечки, сделают невозможным его практическое использование без кардинальных новшеств в техпроцессе. TeraHertz Transistor - это, как легко можно понять, в первую очередь замена материалов, поскольку именно они определяют базовые характеристики транзистора. Окончательно производится отказ от использования диоксида кремния в роли разделительного слоя между затвором и каналом - ему на смену приходит некий материал, называемый Intel "high k gate dielectric", по утверждениям компании уменьшающий утечку электронов с канала в затвор в 10 тысяч раз по сравнению с SiO2. Сказанного ранее достаточно для того, чтобы понять всю важность этой, давно назревшей замены: она позволяет в будущем снизить толщину изолирующего слоя до десятых долей нанометра, при сохранении вполне приемлемых значений утечка тока затвора. Вторая ключевая деталь - это то, что в Intel называют "транзистор с обедненным субстратом", технология, фактически, являющаяся разновидностью SOI. Но с улучшениями - Intel всегда очень настороженно относился к SOI, и просто так он бы его использовать не начал. В свое время у компании были очень серьезные возражения против SOI в любом из его вариантов: с каналом, где лишь часть его является обедненной, или же вся длина канала. В первом случае, по мнению Intel, особых выгод не появляется, а во втором - потребуется делать канал очень малой длины, порядка 10 нм, что очень сложно в производстве и приведет к тому, что очень сильно возрастет внешние сопротивление транзистора по причине уменьшения глубины эмиттера и коллектора. Поэтому транзистор с обедненным субстратом (depleted substrate transistor, DST) представляет из себя первый подход, с полностью обедненным каналом, но с небольшой модификацией, устраняющей его основной минус: канал сделан действительно очень коротким, полностью обедненным, так что сохраняется полный контроль над ним, рабочий ток, проходя непосредственно под затвором, не ионизирует находящуюся под проводящим слоем часть канала транзистора, вызывая эффект его виртуального удлинения, в результате чего характеристики транзистора начинают "плыть". Но все это пока в равной мере относится и к обычному SOI транзистору с полностью обедненным каналом - вопрос по прежнему остается в серьезном росте внешнего сопротивления. Так вот, у DST Intel не позволил влиять глубине канала на глубину стока и коллектора, нарастив необходимую разницу в глубине не вниз, как обычно, а вверх. Все зайцы убиты одним выстрелом: по прикидкам Intel, более чем существенное сокращение тока в нерабочем состоянии даст возможность и дальше продолжать неуклонное понижение питания, ниже 1.0 В, и где-то до 0.6 В к 2010 году.  Вот, собственно говоря, сочетание этих двух вещей, high k диэлектрик затвора и транзистор с обедненным субстратом, Intel и называет TeraHertz Transistor, имея на это, кстати, полное право - в комплексе, они делают возможным создание 32 нм (раза в три меньше, чем вирус гриппа) транзисторов с длиной канала до 15 нм и напряжением порядка 0.75 В, действительно работающих на частоте в 1 TГц. Впрочем, на этом новведения Intel в области транзисторов не заканчиваются. В той же половине нынешней декады, когда начнется использование технологий, составляющих TeraHertz Transistor, Intel намерен совместить их с новой архитектурой самого транзистора - Tri-gate Transistor. Последние три с половиной десятка лет в микроэлектронике используется одна и та же структура транзистора: управляющий электрод, два под ним, и идущий от одного из них к другому поток электронов. Практически двумерная схема - плоскость. В последнее время лидеры микропроцессорной отрасли начали серьезные исследования в области уже "трехмерных" процессоров, с несколькими затворами и каналами. Как понятно по названию, Intel в своей экспериментальной архитектуре предлагает использование трех каналов в одном транзисторе. Об ограничениях традиционной архитектуры выше было сказано - фактически, борьба с утечками поглощает сегодня большинство усилий инженеров. Требуется либо выжимать по капле возможности из обычных транзисторов, либо перейти на что-то новое. Что же из себя вообще представляет транзистор с тремя каналами. Во-первых, он действительно трехмерный даже на первый взгляд - из привычной плоскости кремниевой пластины выступает затвор и эмиттер с коллектором, представляющие из себя крестообразное пересечение: брусок эмиттера/коллектора, пересеченный бруском затвора, изолированного в местах пересечения привычным оксидом. Как бы перевернутый транзистор, не врастающий в пластину, а вырастающий из нее.  Таким образом, транзистор работает сразу в трех измерениях: место среза затворного бруска представляет из себя прямоугольник, верхней и боковыми сторонами которого являются электроды - затворы. Сравнить с проекцией обычного транзистора, где у того же прямоугольника управляющий электрод находится лишь сверху, со всеми вытекающими отсюда обстоятельствами: канал приходится заряжать/разряжать для включения/выключения транзистора гораздо дольше, а напряжение для этого прикладывать - гораздо больше.  Но на этом все отнюдь не заканчивается, напротив - все только начинается. Кто сказал, что затворный брусок можно пересечь лишь одним бруском эмиттера/коллектора? Никто не мешает нам пересечь его сразу несколькими такими брусками, и в результате получится следующая картина: мы включаем транзистор, подавая отпирающий ток на затвор по всей его длине. В результате ток начинает течь во всех брусках, пересекающих затворный, правильно? А рабочий ток транзистора в целом, который, стоит напомнить, является одним из основных параметров его производительности, будет равен сумме значений рабочего тока каждого из таких пересечений! Таким образом, к примеру, с шестью выводами (три - эмиттер, три - коллектор), грубо говоря, не беря в рассмотрение куда большую эффективность (до 20 процентов), мы получаем либо тот же рабочий ток, что и у обычного транзистора при втрое меньшем исходном напряжении, либо, при том же - втрое больший рабочий ток. Дело можно было бы затевать уже только ради этого.   На первый взгляд трехзатворные транзисторы имеют все преимущества по производительности перед своими классическими собратьями, в то же время, будучи способными производиться с использованием того же оборудования и технологий (включая те, что лежат в основе TeraHertz Transistor), а в некоторых отношениях они даже более легки в производстве, облегчая, скажем, требования по длине канала в 2-3 раза, что очевидно, учитывая куда большую его эффективность с тремя затворами. По сути, здесь можно поставить знак равенства между длиной затвора классического транзистора, и произведением высоты на ширину затвора - у трехзатворного. Очевидно, что величины получатся несравнимые. Тем не менее, пока что эта разработка числится в сугубо экспериментальных, с прицелом на возможное использование во второй половине нынешней декады. Естественно, что для того, чтобы обеспечить производство процессоров с транзисторами такой размерности, соответствующим образом должна развиваться литография - процесс, с помощью которого и появляются транзисторы на поверхности кремниевой пластины. Сейчас у Intel, как уже упоминалось, переходный этап - для создания ряда элементов 90 нм чипа удалось приспособить старое доброе 248 нм оборудование, для особо критичных участков - используются новые 193 нм установки, впрочем, таких участков, по данным Intel, набирается менее 20 процентов. Теперь же компания может позволить себе несколько расслабиться, потихоньку увеличивая долю 193 нм оборудования, поскольку его потенциала хватит и для производства чипов с 65 нм транзисторами. Хотя и там придется использовать аналогичную смесь из 193 нм систем с уже созданными сегодня 157 нм устройствами, работающими в D1C в Орегоне. Дальше уже наступит черед Extreme Ultraviolet (EUV) Lithography, использующей свет с длиной волны 13.4 нм (сравним с сегодняшними 193 нм!), которой последние годы занимается консорциум EUV LLC, состоящий из всех ведущих производителей литографического оборудования и производителей чипов. Дела идут достаточно гладко, первые маски были созданы еще в начале 2001 года - с размерностью элементов в 200 нм, однако, пока свет через систему зеркал дойдет до поверхности кремниевой пластины, изображение будет сжато в четыре раза, так что с помощью таких масок вполне можно печатать элементы с размерностью в 50 нм. Как раз то, что и требуется. Впрочем, на достигнутом никто не останавливается - дальше на очереди маски со 120 нм разрешением, которое понадобится уже к концу этого десятилетия для создания 30 нм транзисторов. Intel ожидает начала использования EUV при производстве процессоров где-то с 2005 года, когда компания займется производством чипов по 45 нм техпроцессу.  Опытный образец EUV установки С преодолением всех преград, препятствующих увеличению транзисторов на чипе (а следовательно - и росту количества контактов у процессора) во весь рост станет другой сопутствующий вопрос - использование адекватной таким масштабам упаковки чипа, поскольку без соответствующей защиты, подвода энергии и отвода тепла, обеспечению надежного использования всего этого множества сигнальных линий, потенциал чипа попросту невозможно будет использовать. Впрочем, ответ на этот вопрос у Intel уже имеется - это Bumpless Build-Up Layer (BBUL). Очень логичная, если не сказать - красивая, технология. Что представляет из себя сегодняшняя FCPGA? Чип крепится сверху основного корпуса, соединяясь с ним посредством предназначенных специально для этой цели контактных площадок из органического материала - solder bumps. От контактных площадок сигнал идет к слоям металлических соединений, расположенных в верхней части корпуса, а дальше, через каналы в нем, в нужном порядке добирается до нижних слоев проводников, подсоединенных уже к выводам процессора. По сравнению с теми методами, что были раньше - прогресс очевидный: толщина процессора составляет всего порядка 2 мм (1 мм на корпус, 1 мм - на чип с контактными площадками), открытость верхней поверхности чипа позволяет организовать достаточно эффективное охлаждение через металлическую крышку, прикрывающую чип от повреждений. Но: всегда есть место для улучшений. BBUL в этом плане делает достаточно много. В основе этого метода упаковки лежит размещение чипа непосредственно в корпусе, в специально предназначенной для этого нише. В результате, как минимум становится вдвое меньше высота, и легче сам корпус, что очень важно для тех же ноутбуков, но затевалось все отнюдь не только ради этого. Все слои металлических соединений теперь находятся внизу, между чипом и ножками процессора, так что органики больше нет - на всем пути следования сигнала находится медь, что соответствующим образом отражается на его надежности. Вдобавок, отсутствие контактных площадок позволяет легче развести большее количество соединений.  Конденсаторы, питающие чип, расположены теперь гораздо ближе к нему, не будучи отделены от него всей толщей корпуса. Так что можно и требования по питанию слегка ослабить, и проще подавать его непосредственно туда, где оно необходимо. Кстати, особенно удобен такой корпус для встраивания в него нескольких чипов, вплоть даже до процессора, памяти, графического чипа и чипсета. В общем, плюсов для комплексных продуктов вполне хватает, и уже с 2005-2006 года Intel должен будет начать использовать BBUL в своих коммерческих продуктах. Говоря о совсем уж отдаленной перспективе: естественно, как и конкуренты, Intel активно изучает "жизнь после кремния", в частности, совместно с учеными Гарварда изучая кремниевые нановолокна и углеродные нанотрубки. Сегодня они выглядят предпочтительными кандидатами на роль технологий "пост'2010", какая же именно из них выйдет победителем - говорить пока что рано.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|