|

Опрос

|

реклама

Быстрый переход

Власти США назвали пошлины на полупроводники действенным стимулом к локализации производства чипов

23.05.2026 [04:34],

Алексей Разин

Торговый представитель США Джеймисон Грир (Jamieson Greer) недавно признался, что власти страны продолжают считать импортные пошлины на полупроводниковые компоненты эффективным инструментом стимулирования локального производства. При этом в ближайшее время у правительства нет планов по их заметному изменению.

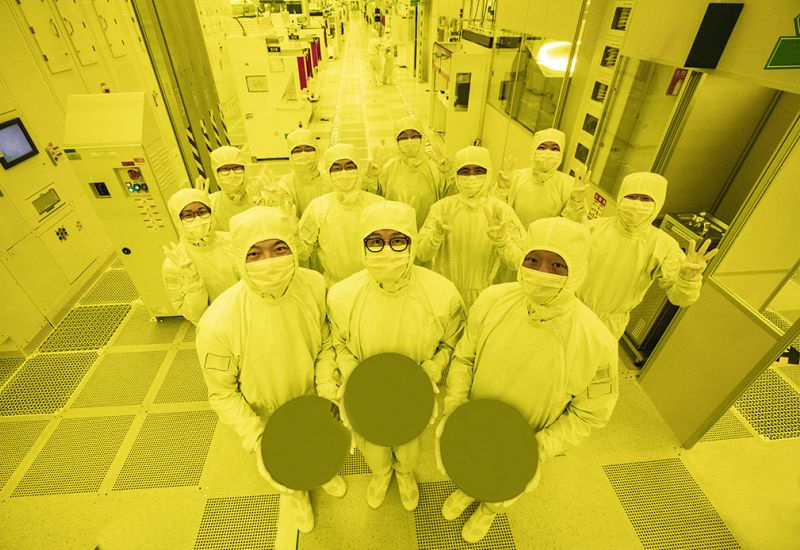

Источник изображения: Micron Technology Свои заявления чиновник сделал на мероприятии, посвящённом расширению предприятия Micron Technology в северной части штата Вирджиния. По его словам, правительство продолжает вести диалог с представителями отрасли по поводу величины и сроков введения новых тарифов, хотя «завтра или на следующей неделе» никто их вводить не собирается. «Мы должны удостовериться, что сделаем это вовремя и в нужном размере, чтобы упростить процесс возвращения промышленности в США», — пояснил Грир. В январе этого года Министерство торговли США подтвердило, что зависимость от импорта полупроводниковых компонентов представляет угрозу для национальной безопасности. Президент Дональд Трамп (Donald Trump) поручил чиновникам провести переговоры с ключевыми экспортёрами на тему тарифного регулирования. По итогам недавней встречи американского президента с китайским коллегой позиция властей США по этому вопросу не изменилась, как подчеркнул Грир. Действующий подход позволяет локализующим производство в США компаниям ввозить определённую часть своей продукции из-за рубежа по льготным тарифным ставкам, но только при условии последующей локализации её выпуска. Micron собирается в ближайшие двадцать лет направить $200 млрд на развитие производства памяти в США. Компания старается нарастить объёмы выпуска памяти в условиях бума ИИ, но дополнительные мощности появляются медленнее, чем растёт спрос. На конкурирующих Samsung и SK hynix власти США готовы тоже воздействовать при помощи импортных тарифов, если те не будут вкладываться в расширение своего производства в США. Глава Micron пояснил, что на строительство нового предприятия уходит несколько лет, а вот как быстро готовый корпус можно оснастить оборудованием, зависит от текущих прогнозов по рыночному спросу на продукцию. Главное в этой сфере — быть готовым к удовлетворению спроса, как подчеркнул генеральный директор компании Санджей Мехротра (Sanjay Mehrotra). Компания сейчас заключает с клиентами долгосрочные контракты, чтобы повысить предсказуемость поставок памяти. Китайские контрактные производители чипов начали поднимать цены на услуги, чтобы урвать свой кусок ИИ-пирога

22.05.2026 [22:57],

Алексей Разин

Выгоду от высокого спроса на полупроводниковые компоненты в условиях бума ИИ ощущают не только западные производители памяти и чипов под заказ, но и их китайские конкуренты. Они тоже не прочь поднять цены на свои услуги, как отмечает TrendForce со ссылкой на китайские СМИ.

Источник изображения: SMIC В первом квартале текущего года основная часть китайских публичных разработчиков чипов призналась, что их операционные расходы выросли в годовом сравнении, во многом из-за роста затрат на услуги подрядчиков, которые выпускают для них чипы. Сообщается, что уровень загрузки конвейера ведущей местной компании в этой сфере — SMIC, поднялся в мае почти в два раза по сравнению с третьим кварталом прошлого года. SMIC и её ближайший конкурент Hua Hong завершили первый квартал этого года ростом не только выручки, но и нормы прибыли, хотя данный сезон обычно характеризуется спадом клиентской активности. Цены на категории продукции, пользующиеся повышенным спросом, были увеличены. Осознавая неизбежность такой тенденции, некоторые клиенты SMIC предпочли закупиться продукцией впрок сверх текущей потребности. Во втором квартале SMIC рассчитывает выйти на норму прибыли в диапазоне от 20 до 22 %, что на два процентных пункта выше показателя предыдущего квартала. Руководство SMIC отметило сразу несколько факторов, способствующих росту спроса на её услуги. Помимо отсутствия свободных квот на производство чипов у зарубежных конкурентов, растёт потребность мировой ИИ-отрасли в компонентах для инфраструктуры, включая силовую электронику. Кроме того, внедрение ИИ в физические устройства типа систем автопилота и робототехники поднимает спрос на специализированные датчики и прочие компоненты, которые SMIC способна выпускать. Hua Hong поднимала цены на свои услуги в 2025 году и намеревается продолжить тенденцию в 2026 году — по крайней мере, в части обработки кремниевых пластин типоразмера 300 мм. Силовая электроника тоже пользуется спросом, как отмечают в Hua Hong, поскольку строительство серверной инфраструктуры для ИИ подразумевает закупку не только передовых чипов. Мировые лидеры в сфере контрактного производства полупроводниковых компонентов типа TSMC и Samsung концентрируются на более доходных передовых техпроцессах, поэтому обслуживание спроса на зрелые технологии постепенно становится специализацией китайских контрактных производителей. Кроме того, тайваньские контрактные производители «второго эшелона» также поддерживают высокий уровень цен на свои услуги, что невольно заставляет их клиентов обращаться к китайским конкурентам. Последние к тому же консолидируют активы, чтобы лучше соответствовать запросам рынка и оптимизировать затраты. Работники чипового бизнеса Samsung выбили бонусы до $428 000 — остальные почувствовали себя обделёнными

22.05.2026 [15:46],

Алексей Разин

Южнокорейская компания Samsung Electronics является крупнейшим производителем микросхем памяти, но это не значит, что доходы сотрудников прочих подразделений должны зависеть только от конъюнктуры рынка памяти. Добившись повышения премий для сотрудников, занятых в производстве чипов, профсоюз Samsung невольно создал причину для недовольства работников, задействованных на других направлениях.

Источник изображения: Samsung Electronics Следует признать, что профсоюз всё же не забыл про сотрудников подразделений Samsung, которые специализируются на других видах продукции, но упор был сделан именно на улучшении благосостояния тех, кто связан с полупроводниковым производством. Часть операционной прибыли компании, которая должна распределяться в виде ежегодных премий, всё равно будет преимущественно оседать в карманах работников, связанных с выпуском чипов. Они получат до 40 % всего фонда премирования, а оставшиеся 60 % будут распределены между прочими структурными единицами в составе Samsung Electronics. Как утверждает Bloomberg, разрыв в размерах годовой премии может быть 100-кратным. Например, если занятые в производстве памяти сотрудники Samsung будут получать более $400 000 премиальных в год, то работники, занятые производством телевизоров, — в 100 раз меньше. Руководство Samsung очень не хотело повышать премии сотрудникам убыточных подразделений, но профсоюз добился, чтобы потолок годовой премии для них был повышен с обычных 50 % годовой зарплаты до 60 %. Правда, новые условия вступят в силу только в следующем году. Формально, как поясняет Chosun Daily, ограничение на величину годовой премии так и осталось на уровне 50 % для всех сотрудников Samsung Electronics, просто на ближайшие десять лет предусмотрена дополнительная стимулирующая выплата, наличие которой будет зависеть от достижения операционной прибылью Samsung определённой величины на конкретном временном интервале. Так, до 2029 года порог установлен на уровне $1,3 млрд, причём учитываться будет именно операционная прибыль полупроводникового подразделения компании. В период с 2029 по 2035 годы дополнительные выплаты будут предусмотрены, если эта прибыль превысит $660 млн. Как отмечалось ранее, основная часть премиальных выплат будет осуществляться в форме акций Samsung, на эти нужды будет направляться до 10,5 % годовой операционной прибыли. Сотрудники смогут сразу продать треть полученных акций, ещё треть — через год, а оставшуюся часть — через два года после получения. Лишь 1,5 % годовой операционной прибыли будет выплачиваться в виде денежных премий. Примечательно, что размер годовой премии сотрудников Samsung теперь будет превышать сумму основной зарплаты за этот период, если учитывать возможность продажи акций. Эта пропорция справедлива даже для убыточных подразделений. К ним относятся LSI, разрабатывающее процессоры Samsung, и контрактное направление Foundry. Их сотрудники смогут получить до $122 000 премиальных выплат. Впрочем, по сравнению с занятыми в производстве памяти сотрудниками это весьма скромная сумма, ведь те получат по $428 000, если прогноз по операционной прибыли на этот год сбудется. «Промежуточные» с точки зрения динамики финансовых показателей подразделения Samsung смогут выплачивать своим сотрудникам в среднем по $336 000. В соглашении с профсоюзом присутствует и возможность выплаты премий подрядным организациям и партнёрам Samsung Electronics, если их профсоюзные объединения запросят такую опцию. Эксперты теперь опасаются, что работники смежных отраслей начнут по примеру профсоюза Samsung требовать повышения премий и зарплат. IBM создаст контрактное производство чипов завтрашнего дня — квантовое

22.05.2026 [11:39],

Геннадий Детинич

IBM и Министерство торговли США объявили о намерении создать Anderon — новую дочернюю компанию IBM с широкими правами самостоятельной работы. Предприятие будет обрабатывать 300-мм «квантовые» пластины для выпуска квантовых процессоров и сопутствующей электроники. Это попытка возврата IBM к контрактному производству после продажи заводов компании GlobalFoundries в 2014 году, но на новом уровне — для работы с заказчиками в сфере квантовых вычислений.

Источник изображения: IBM Деньгами в создании Anderon примет серьёзное участие Министерство торговли США. Оно внесёт в общий котёл $1 млрд в рамках закона CHIPS Act, а ещё $1 млрд выделит IBM. Также компания передаст новой структуре интеллектуальную собственность, производственные активы и профильных специалистов. Штаб-квартира и производство будут расположены в Олбани, штат Нью-Йорк. Выбор 300-мм пластин обусловлен современной производственной архитектурой — от изготовления заготовок для пластин до боксов для транспортировки, тестового и промышленного оборудования. Сегодня в этом сегменте представлено всё самое лучшее, и этим было бы грех не воспользоваться. На первом этапе запуска производства, если дело до него дойдёт (пока подписан только документ о намерениях), компания Anderon будет выпускать пластины для сверхпроводниковых кубитов и сопутствующей электроники. Это именно тот тип кубитов, на котором IBM строит свои квантовые процессоры: сверхпроводящие схемы охлаждаются почти до абсолютного нуля, а квантовые состояния управляются микроволновыми сигналами. Схемы с кубитами будут содержать сверхпроводящую разводку, сквозные кремниевые переходы (TSV), контактные группы и другие элементы. Также завод будет тестировать чипы и, возможно, заниматься их упаковкой. В дальнейшем IBM намерена организовать на предприятии Anderon контрактное производство для обслуживания заказов со всего мира. На этом этапе компания начнёт осваивать изготовление иных типов кубитов, отличных от её собственных. Тем самым компания будет стремиться стать мировым центром производства квантовых процессоров. На момент публикации пресс-релиза расшифровки названия или аббревиатуры Anderon не приводилось. На наш взгляд, это созвучная модификация и комбинация слов under и on, что можно трактовать как «включаем ниже», следуя квантовой логике проекта. Но мы можем ошибаться. Будет интересно узнать официальную версию. Lam Research собирается внедрять ИИ в оборудование для производства чипов, чтобы снизить уровень брака продукции

22.05.2026 [06:59],

Алексей Разин

До сих пор считалось, что искусственный интеллект связан с оборудованием для производства чипов только ростом спроса на него в условиях бума, но представители Lam Research дали понять, что соответствующие технологии способны снизить уровень брака и повысить производительность при использовании этого оборудования по прямому назначению.

Источник изображения: Lam Research Как заявил в интервью Reuters генеральный директор Lam Research Тим Арчер (Tim Archer), этот американский производитель оборудования для выпуска чипов намерен внедрить в свои изделия дополнительные датчики и алгоритмы с использованием ИИ, которые помогут быстрее выявлять проблемные места в дизайне чипов и обнаруживать дефекты на ранних этапах. Клиентам это позволит выпускать больше чипов с меньшим уровнем брака. По словам Арчера, ИИ позволяет наделить оборудование для производства чипов способностью обнаруживать те проблемные состояния, которые ранее не выявлялись достоверно с помощью классических методов диагностики. Lam Research также собирается не только расширять свою калифорнийскую площадку, но и построить лабораторию в Аризоне, чтобы быть ближе к крупным заказчикам в лице TSMC и Intel, у которых в этом штате имеются предприятия по производству чипов. Эта инициатива потребует примерно $45 млн инвестиций. Работники чипового бизнеса Samsung выбили премии почти по $340 000 на человека

21.05.2026 [15:48],

Алексей Разин

Буквально в последний момент руководству Samsung Electronics удалось при поддержке властей Южной Кореи предотвратить крупнейшую в истории компании забастовку сотрудников, которые требовали изменения условий ежегодного премирования. В этом году, если прогнозы по величине операционной прибыли Samsung оправдаются, некоторые из них получат премии по $340 000 на человека в среднем.

Источник изображения: Samsung Electronics Подобная сумма получена представителями Bloomberg по итогам расчётов, исходя из ожидаемой величины операционной прибыли Samsung Electronics в этом году. На премирование сотрудников, занятых в производстве чипов, Samsung может направить до $26,6 млрд. Если учесть, что в этой сфере на предприятиях компании занято около 78 000 человек, то каждому в среднем достанется по $340 000. В прошлом году размер годовой премии был более чем в три раза меньше, например. Если премии будут распределяться только среди сотрудников, занятых на производстве именно чипов памяти, то их средняя величина может даже приблизиться к $400 000 на человека. К слову, не все премиальные выплаты сотрудникам будут осуществляться собственно в денежной форме. Временное соглашение с профсоюзом, которое ещё только предстоит утвердить, подразумевает распределение 10,5 % операционной прибыли в форме акций среди сотрудников, и только 1,5 % в денежной форме. Подобная схема премирования будет действовать на протяжении десяти лет, если прибыль Samsung будет удерживаться на определённом уровне или превышать его. В этом году, как ожидают аналитики, операционная прибыль Samsung должна вырасти в семь раз до $221 млрд. Премия за 2026 год будет выплачена сотрудникам Samsung в начале 2027 года, и до трети полученных акций они смогут продать сразу, а оставшуюся их часть — поэтапно на протяжении последующих двух лет. Естественно, внука основателя Samsung Ли Чжэ Ёна (Lee Jae-yong) бум искусственного интеллекта тоже обогатил существенным образом. Его личное благосостояние оценивается в $32 млрд, делая его самым обеспеченным в Южной Корее человеком. Его ближайшие родственники по состоянию на март этого года располагали сообща около $45,5 млрд, находясь на третьем месте среди богатейших семейств Азии. Акции Samsung подскочили на 6 % после постановки на паузу масштабной забастовки

21.05.2026 [11:52],

Владимир Фетисов

Стоимость ценных бумаг Samsung Electronics выросла в четверг более чем на 6 % после того, как поздно вечером в среду профсоюз компании приостановил запланированную ранее 18-дневную забастовку. Достижение предварительных договорённостей между сторонами конфликта снизило опасение по поводу возможного снижения объёмов производства.

Источник изображения: Samsung Electronics Изначально профсоюз заявил, что забастовка состоится. Это произошло после того, как прошедшие в среду переговоры с участием представителей правительства Южной Кореи провалились. Однако ещё один раунд переговоров под руководством министра труда и занятости Ким Ён Хуна (Kim Young-hoon) позволил добиться прогресса и достигнуть предварительного соглашения. Росту стоимости акций Samsung также способствовал оптимизм инвесторов в отношении ценных бумаг других представителей полупроводниковой отрасли. Недавно Nvidia отчиталась об очередном сильном квартале, в рамках которого выручка компании выросла на 85 % до $81,62 млрд, тогда как за аналогичный период годом ранее этот показатель составил $44,06 млрд. Во время брифинга, который транслировал государственный телеканал KTV на YouTube, Ким Ён Хун подчеркнул, что пока речь идёт только о предварительном соглашении и до финального соглашения «предстоит пройти долгий путь». Он добавил, что осталось множество нерешённых вопросов, но разрыв между двумя сторонами «значительно сократился», поскольку профсоюз пошёл на значительные уступки. По данным южнокорейского информагентства Yonhap, высокоприбыльное полупроводниковое подразделение Samsung получит 40 % от общего бонусного фонда, тогда как другие бизнес-единицы компании разделят оставшиеся 60 % фонда. Спорное решение о том, как разделить бонусы среди убыточных подразделений Samsung, отложено на год. В сообщении сказано, что Samsung согласилась выделить специальный бонус в размере 10,5 % операционной прибыли для полупроводникового подразделения, одновременно приняв требования профсоюза по привязке бонусов к операционной прибыли и отмене верхнего предела для таких выплат. По данным источника, Samsung также будет частично финансировать специальные бонусы акциями компании в течение как минимум 10 лет при условии, что полупроводниковое подразделение превысит целевые показатели по операционной прибыли в 200 трлн вон ($133,65 млрд) в 2026-2028 годах. В дополнение к этому целевой показатель на 2029-2035 годы был снижен до 100 трлн вон. Samsung увернулась от забастовки, способной взвинтить цены на память — рабочие добились повышения премий

20.05.2026 [23:00],

Николай Хижняк

Профсоюз сотрудников Samsung Electronics объявил о приостановке забастовки, которая должна была начаться в четверг. Это произошло после того, как представители работников достигли предварительного соглашения с руководством компании о вознаграждениях, пишет Reuters. Это позволило избежать последствий, которые угрожали экономике Южной Кореи и глобальным поставкам микросхем.

Источник изображения: Samsung Electronics Запланированная 18-дневная забастовка, в которой должны были принять участие почти 48 000 членов профсоюза, была поставлена на паузу до тех пор, пока предварительное соглашение не будет вынесено на голосование. Голосование пройдёт с 22 по 27 мая, сообщил журналистам лидер профсоюза Чхве Сын Хо (Choi Seung-ho) поздно вечером в среду. Ранее на сайте профсоюза было опубликовано уведомление о том, что голосование пройдёт с 23 по 28 мая. Samsung по-прежнему остаётся одним из самых престижных работодателей в Южной Корее, но сотрудники компании были недовольны разницей в премиях по сравнению с более мелким конкурентом — компанией SK hynix, а также предложенным распределением бонусов между подразделениями Samsung. В отдельном заявлении Samsung Electronics говорится, что стороны достигли предварительного соглашения о заработной плате и коллективных переговорах и обязались «выстраивать зрелые и конструктивные отношения между работниками и руководством». Соглашение было достигнуто в последний момент после нескольких дней переговоров, которые неоднократно срывались, в том числе в среду, когда профсоюз объявил о начале забастовки. Переговоры возобновились позже в тот же день после того, как министр труда Южной Кореи Ким Ён Хун (Kim Young-hoon) лично выступил посредником между сторонами. Как ранее сообщалось, стороны не могли прийти к согласию по поводу распределения бонусов за производственные показатели между высокодоходным подразделением по производству памяти и убыточными подразделениями по контрактному производству логических микросхем. Лидер профсоюза Чхве Сын Хо заявил, что стороны договорились о распределении прибыли между убыточными подразделениями, и ожидает, что члены профсоюза одобрят соглашение о заработной плате. «Мы сделаем всё возможное, чтобы стабилизировать отношения между работниками и руководством Samsung Electronics в будущем», — сказал он. По словам одного из представителей профсоюза, участвовавшего в переговорах, Samsung согласилась отменить 50-процентный лимит на премиальные выплаты, привязать премиальные выплаты к операционной прибыли и официально закрепить изменения в контрактах. Он отказался назвать своё имя, поскольку не имел права общаться с прессой. «Это очень выгодная сделка», — заявил он. Кроме того, согласно документу, опубликованному профсоюзом, Samsung выделит около 10,5 % от «согласованных показателей эффективности бизнеса» на специальные премиальные выплаты для подразделения по производству чипов, в состав которого входят подразделения по производству памяти и логических микросхем. По словам представителя профсоюза, в качестве показателя эффективности бизнеса рассматривается операционная прибыль. Специальные премиальные выплаты будут выплачиваться акциями компании в течение как минимум 10 лет. Согласно документу, в период с 2026 по 2028 год подразделение по производству чипов должно получить более 200 трлн вон ($133,58 млрд) в виде годовой операционной прибыли, а в период с 2029 по 2035 год — 100 трлн вон. Руководством Samsung отказалось комментировать детали сделки, пишет Reuters. Компания Samsung, на долю которой приходится почти четверть всего экспорта Южной Кореи, также является крупнейшим в мире производителем микросхем памяти. Забастовка профсоюза сотрудников компании могла привести к сбоям в работе всей компании, что спровоцировало бы рост цен на фоне бума в сфере искусственного интеллекта, который привёл к дефициту продукции. «Мы благодарны за взвешенное решение, принятое в интересах страны и общества. Такой исход стал возможен благодаря усилиям правительственных чиновников, в том числе министра труда, который до последнего выступал посредником», — заявил представитель официальная резиденция президента Южной Кореи, пишет информационное агентство Yonhap. Представитель Центрального банка страны, пожелавший остаться анонимным, прогнозировал, что забастовка может снизить рост экономики Южной Кореи на 0,5 процентного пункта по сравнению с прогнозируемыми 2 % в этом году. Представители правительства Южной Кореи заявляли, что могут прибегнуть к экстренному арбитражу — инструменту, который применяется крайне редко, но который мог бы приостановить забастовку на 30 дней. Пользователи онлайн-форума для акционеров Samsung выразили облегчение в связи с принятым предварительным соглашением. «Я выражаю благодарность и поздравляю всех», — говорилось в одном из сообщений. Другие приветствовали предложение о выплате бонусов акциями компании, заявив, что это может повлиять на стоимость акций Samsung. Акции Samsung упали на 0,2 %, а с начала недели — на 2,8 %. Некоторые инвесторы заявили, что их больше беспокоят перспективы постоянного роста затрат на рабочую силу, чем разовые расходы, связанные с забастовкой. Возглавив Intel, Лип-Бу Тан объявил войну дефектным процессорам и нерадивым инженерам

20.05.2026 [15:51],

Алексей Разин

Компания Intel своего звания «процессорного гиганта» добивалась десятилетиями, за это время она выпустила огромное количество продукции, которая не была безупречна во многих смыслах, а потому нередко требовала исправлений на аппаратном уровне. Генеральный директор Лип-Бу Тан (Lip-Bu Tan) недавно признался, что готов увольнять тех разработчиков, которые не могут обеспечить приемлемое качество процессоров буквально с первой ревизии.

Источник изображения: Intel Откровения заступившего на пост главы Intel в марте прошлого года Лип-Бу Тана прозвучали на технологической конференции JP Morgan, как отмечает Tom’s Hardware. Как было известно ранее, новый руководитель Intel стал принимать более активное участие в утверждении дизайна продуктов и обсуждении их характеристик. Дело дошло до того, что Лип-Бу Тан требует от инженеров Intel, чтобы даже начальная ревизия A0, которая используется для выпуска предсерийных процессоров после получения цифрового проекта, демонстрировала почти полное отсутствие дефектов и характеристики, близкие к целевым показателям серийной продукции. «Говоря о графике, я внедрил культуру, которая подразумевает, чтобы A0 была готова к производству. A0 — это когда создаётся цифровой проект, он должен сразу проходить все тесты. В Intel не было такой культуры, но я сказал, что A0 должен проходить тесты с первого раза. B0 — сохраняешь рабочее место. Всё, что выше этого — уволен», — пояснил свой подход нынешний генеральный директор Intel. По его словам, сотрудники компании сперва приняли это за шутку, но когда столкнулись с практическим применением этого принципа, стали гораздо серьёзнее подходить к разработке процессоров и поиску дефектов на этапе проектирования. В комбинации со сложным дизайном процессоров и применением передовых техпроцессов достичь безупречности характеристик с первой ревизии весьма сложно, поэтому трудно предугадать, каким образом внедрение такой культуры проектирования повлияет на развитие Intel. Возможно, инженеры компании станут реже предлагать радикальные изменения и улучшения характеристик, чтобы лишний раз не рисковать. Nvidia тоже нередко запускает в производство чипы первых ревизий, но при этом на уровне функциональных блоков закладывается некоторая избыточность, чтобы в случае проявления дефектов можно было компенсировать их другими ресурсами. Ранее Intel подходила к проблеме более снисходительно. Например, серверные процессоры Sapphire Rapids пережили за свою историю двенадцать ревизий, которые были призваны устранить около 500 ошибок и дефектов разной степени значимости. Впрочем, главу Intel можно понять — чем меньше времени тратится на устранение дефектов в уже выпускаемых процессорах, тем быстрее выводятся на рынок новые изделия должного качества. Глава Intel в интервью CNBC также пояснил, что компания желает учесть прежние ошибки, и сделать перспективный план выпуска новых продуктов более простым. По его словам, с первых дней в должности генерального директора он сразу подчинил себе всю инженерную работу. Как признаётся Тан, прежнему генеральному директору инженерные специалисты напрямую не подчинялись. Главе компании отчитывалось такое количество сотрудников, что он просто упускал из виду технические моменты. Тан считает, что упрощение дизайна продуктов позволило бы решить многие проблемы Intel. Он также считает важным регулярное и плотное взаимодействие с клиентами с целью укрепления доверия к компании. Выпуск продукции по передовой технологии 14A она собирается наладить в 2028 году в режиме опытного производства, а к 2029 году перейти к массовому. Бум ИИ загнал производителей SSD и модулей памяти в многомиллионные долги

20.05.2026 [10:50],

Алексей Разин

Выпускаемые лидерами рынка микросхемы памяти ещё нужно разместить на модулях памяти и SSD, и для производителей таких устройств нынешняя динамика роста цен в сочетании с дефицитом создаёт довольно сложные условия работы. Они вынуждены залезать в многомиллионные долги ради обеспечения товарных запасов, позволяющих ритмично отгружать продукцию.

Источник изображения: Micron Technology Как сообщает TechSpot со ссылкой на тайваньское издание Commercial Times, местные производители модулей памяти и твердотельных накопителей типа Adata, TeamGroup, Apacer, Innodisk, Transcend и Silicon Power сообща заняли около $880 млн только для того, чтобы закупить нужное количество микросхем памяти для поддержания бизнеса. Выпуск облигаций, кредиты и даже размещение акций используются участниками рынка для финансирования соответствующих нужд. Всё это происходит на фоне роста финансовых показателей производителей модулей памяти и твердотельных накопителей. Выручка Adata по итогам марта впервые превысила $316 млн, что в национальной валюте Тайваня соответствует круглой сумме в 10 млрд местных долларов. Квартальная выручка Adata более чем удвоилась в годовом сравнении до $826 млн. По сути, производителям модулей памяти и твердотельных накопителей грех жаловаться на финансы, но для экстренного пополнения оборотных средств им всё равно приходится прибегать к заимствованиям. Тем более, что цены на микросхемы памяти растут на десятки процентов за квартал, иной раз увеличиваясь кратно, а потому на закупку сырья уходит очень много денег. Ситуация будет только усугубляться, поскольку собственно производство микросхем памяти не будет заметно расширяться вплоть до следующего года или более позднего периода. Крупнейшая забастовка в истории Samsung всё ближе — переговоры снова провалились

20.05.2026 [07:49],

Алексей Разин

Очередной этап переговоров между представителями профсоюза сотрудников Samsung Electronics и работодателем, который проходил при посредничестве южнокорейских властей, так и не позволил сторонам достичь согласия по всем ключевым пунктам, и теперь угроза 18-дневной забастовки, которая должна начаться завтра, становится более реальной.

Источник изображения: Samsung Electronics Суд накануне хотя и запретил профсоюзу Samsung, охватывающему около 48 000 сотрудников компании, создавать условия для причинения серьёзного ущерба работодателю или окружающей среде, в полной мере акцию протеста предотвратить не в силах. Глава профсоюза Цой Сон Хо (Choi Seung-ho), на заявление которого ссылается Reuters, сообщил о готовности объединения провести 18-дневную забастовку в соответствии с ранее намеченным планом. Стороны в ходе переговоров сблизили позиции по всем пунктам, кроме одного, который для профсоюза имел принципиальное значение. По всей видимости, речь идёт о принципе распределения годовых премий, на изменении которого настаивал профсоюз. Он считал, что Samsung должен распределять между сотрудниками до 15 % операционной прибыли ежегодно, без ограничения по сумме выплат, которое сейчас находится на уровне 50 % от годовой зарплаты. По словам Цоя, профсоюз принял последнее предложение, сделанное правительственным медиатором. В свою очередь, руководство Samsung Electronics заявило, что профсоюз настаивал на неприемлемых условиях: «Причина, по которой соглашение не может быть достигнуто, заключается в избыточности требований профсоюза, которые подрывают фундаментальные принципы управления компанией». Работодатель считает, что не может на регулярной основе предлагать сотрудникам убыточных подразделений столь высокие годовые премии. В минувшие выходные власти Южной Кореи пригрозили Samsung принудительным арбитражем, в результате которого начало забастовки может быть отложено на 30 дней, пока представители государственных структур принимают участие в переговорах. Акции Samsung упали в цене более чем на 3 %. Компания обеспечивает почти четверть национального экспорта Южной Кореи и является крупнейшим в мире производителем памяти. Длительная забастовка сотрудников в условиях нехватки памяти на мировом рынке навредит не только репутации самой Samsung, но и всей корейской экономике. ASML пообещала первые серийные чипы на High-NA EUV уже в этом году

19.05.2026 [17:46],

Алексей Разин

До сих пор главным покупателем сверхдорогих литографических систем ASML с высоким значением числовой апертуры (High-NA EUV) считалась компания Intel, но они до сих пор были ей интересны с точки зрения экспериментов в рамках подготовки к переходу на технологию 14A. Сама ASML заявила, что первые продукты, выпущенные с помощью такого оборудования, появятся в ближайшие месяцы.

Источник изображения: ASML Напомним, Intel начала закупать у ASML системы семейства TwinScan EXE:5000, которые использовались для прототипирования, ещё в середине 2023 года. Позже она забронировала весь тираж сканеров ASML данного класса на 2024 год, а к концу 2025 года установила у себя первую систему серии TwinScan EXE:5200, которую теоретически можно использовать в серийном производстве. Данное оборудование обеспечивает дальнейшее уменьшение геометрических параметров полупроводниковых компонентов, увеличивая плотность размещения транзисторов на кристалле и повышая тем самым быстродействие чипов. Новый сканер способен обрабатывать до 220 кремниевых пластин в час. Заметим, что в серийном производстве Intel наверняка не будет применять технологию High-NA EUV для обработки сразу нескольких слоёв чипа, а станет постепенно внедрять её только на нужных этапах. TSMC к оборудованию с высоким значением числовой апертуры пока присматривается издалека, считая его слишком дорогим для использования в массовом производстве. Samsung Electronics старается не отставать от Intel и постепенно обзаводится подобными сканерами ASML, аналогичным образом поступает и конкурирующая SK hynix. Соответственно, эти литографические сканеры можно будет использовать и для производства логических компонентов, и при выпуске микросхем памяти. На это как раз намекнул генеральный директор ASML Кристоф Фуке (Christophe Fouquet) на отраслевом мероприятии, организованном бельгийской Imec: «В ближайшие несколько месяцев мы ожидаем увидеть первые продукты — как в сегменте логики, так и памяти, обработанные на системах класса High-NA». Одна такая литографическая система ASML обходится заказчикам почти в $400 млн. Хотя само оборудование обходится дорого в закупке, оно снижает потребность в оснастке, используемой для экспозиции фотошаблонов, а также ускоряет процесс изготовления чипов. Южнокорейский суд запретил работникам Samsung бастовать из-за низких премий — разве что понемножку

19.05.2026 [09:56],

Алексей Разин

Уже в этот четверг Samsung Electronics может столкнуться с крупнейшей в своей истории акцией протеста сотрудников, которая охватит до 50 000 работников компании, настаивающих на повышении зарплат и премий. Южнокорейский суд запретил профсоюзу прибегать к действиям, которые приведут к масштабному ущербу для компании или окружающей среды.

Источник изображения: Samsung Electronics Сама по себе забастовка не запрещается, но в её ходе участники должны придерживаться разумных пределов. Согласно предписанию суда, действия участников забастовки не должны представлять угрозу для сотрудников Samsung или приводить к порче оборудования или продукции. Для этого определённые объёмы её выпуска должны поддерживаться, чтобы находящиеся в обработке кремниевые пластины не пришлось списывать в брак. Профсоюзу также запрещено доводить до поломки оборудования или образования чрезмерного количества отходов, блокировать доступ персонала на рабочие места или оставлять работающее оборудование без присмотра, включая выходные и праздничные дни. Ключевой персонал Samsung должен оставаться на своих местах и работать даже в период проведения забастовки, как постановил суд. Непосредственно переговоры между профсоюзом и руководством Samsung Electronics пока не демонстрируют признаков прогресса. Работодатель готов единовременно выплатить крупную премию избранным сотрудникам, но не собирается снимать ограничение на предельный размер регулярной годовой премии, который сейчас установлен на уровне 50 % от годовой зарплаты сотрудника. Кроме того, профсоюз настаивает, что на выплату премий персоналу нужно направлять до 15 % операционной прибыли на ежегодной основе. Власти страны готовы прибегнуть к экстренному арбитражу и вмешательству в управление компанией, если руководство Samsung Electonics и профсоюз не смогут договориться об условиях, позволяющих сохранить объёмы выпуска продукции в нужных количествах. «Очень серьёзный прорыв»: Intel уверена, что техпроцесс 14A позволит ей снова бросить вызов TSMC

19.05.2026 [07:27],

Алексей Разин

На техпроцесс 18A делало большие ставки и прежнее руководство Intel, но нынешний генеральный директор Лип-Бу Тан (Lip-Bu Tan) ещё и выражает удовлетворение тем прогрессом, который компания демонстрирует в улучшении показателей качества продукции. Более того, он уверен, что следующий техпроцесс Intel 14A позволит компании конкурировать с TSMC.

Источник изображения: Intel Столь амбициозные высказывания прозвучали из уст Лип-Бу Тана в ходе выступления на телеканале CNBC. Во-первых, контрактный бизнес он назвал очень важным не только для самой Intel, а для всей национальной экономики. В первые месяцы после прихода Лип-Бу Тана на пост генерального директора Intel весной прошлого года, как он признался, уровень выхода годной продукции в рамках техпроцесса 18A был «не очень хорошим». Сейчас он буквально повышается на 7 или 8 % ежемесячно, и Тан этим весьма доволен. Данный прогресс привлекает потенциальных клиентов к Intel 18A, хотя их имена глава компании называть категорически отказывается, уклоняясь от прямого ответа на вопрос о начавшемся сотрудничестве с Apple. По словам главы Intel, во втором полугодии соглашения о сотрудничестве в сфере контрактного производства чипов могут быть заключены со множеством клиентов. Развитие производства чипов на территории США глава Intel считает задачей государственной важности, поскольку за её пределами сейчас выпускается более 90 % передовой продукции. Тан убеждён, что следующий техпроцесс 14A позволит Intel соперничать с TSMC на равных: «Он будет доступен в одно время с TSMC, это будет очень, очень серьёзный прорыв». Apple научилась зарабатывать даже на бракованных чипах — их годами ставят в iPhone, iPad и Mac

18.05.2026 [16:14],

Алексей Разин

Специфика массового производства такова, что полностью исключить брак невозможно, а при изготовлении полупроводниковых компонентов он неизбежен в силу сложности техпроцессов и миниатюрности изделий. Apple старается применять свои дефектные чипы с выгодой, продавая их в составе не тех устройств, для которых они изначально предназначались.

Источник изображения: Apple Как отмечает 9to5Mac со ссылкой на публикацию The Wall Street Journal, дефектные экземпляры чипов Apple применялись и применяются следующим образом: A15 Bionic — в составе iPhone SE; A17 Pro — в составе iPad mini; A18 — в iPhone 16e; A19 — в iPhone 17e; A19 Pro — внутри iPhone Air. Более того, такая практика существует ещё со времён iPhone 4, поскольку процессоры A4 нашли применение в телевизионных приставках Apple TV, где их высокий уровень энергопотребления никого особо не смущал. Разработанные для Apple Watch процессоры S7 также прописались в HomePod, поскольку использовать их по прямому назначению было проблематично. Сортировка чипов по признаку наличия у них разного количества функционирующих блоков позволила Apple предложить ноутбуки MacBook Neo по довольно привлекательной для западных покупателей цене. Чипы A18 Pro в их составе имеют только пять ядер графической подсистемы вместо шести у iPhone 16 Pro. Специально для MacBook Neo чипы с пятью графическими ядрами не выпускаются: на оснащение этих ноутбуков направляются дефектные экземпляры A18 Pro, у которых работают только пять ядер из шести. Как сообщается, Apple даже столкнулась с необходимостью заказать дополнительное количество чипов A18 Pro, поскольку запасы «отсеянных» на этапе подготовки к выпуску iPhone 16 Pro быстро истощились из-за высокого спроса именно на MacBook Neo. Различия в характеристиках чипов могут наблюдаться даже в пределах одной продуктовой линейки Apple. Например, MacBook Air на базе чипа M1 в старших комплектациях имеет восемь графических ядер, а младшая версия за $999 довольствуется семью. Это позволяет предлагать начальный вариант MacBook Air по привлекательной цене и не выбрасывать те чипы, которые не полностью работоспособны по признаку количества графических ядер. |