На конференции ISSCC 2023 представители компании SK hynix выступили с докладом, в котором сообщили о разработке флеш-памяти 3D NAND с более чем 300 слоями. Документ готовили 35 инженеров компании, что лишний раз подчёркивает сложность совершенствования техпроцесса производства многослойной флеш-памяти. Примечательно, что разработчики намерены не только увеличить плотность записи, но и значительно поднять пропускную способность чипов: со 164 Мбайт/с до 194 Мбайт/с.

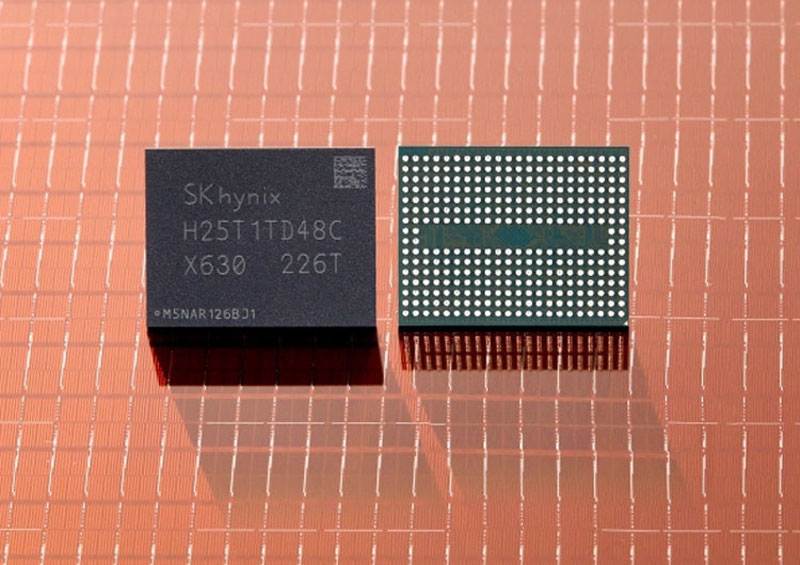

Предыдущий рекордсмен — 238-слойная 3D NAND SK hynix. Источник изображения: SK hynix

Нетрудно понять, что инженеры SK hynix работают по двум основным и важнейшим направлениям: они намерены повысить плотность записи (снизить стоимость хранения каждого бита данных) и повысить производительность. С появлением «многоэтажной» 3D NAND повышать плотности записи стало довольно просто в идее, но сложно в исполнении — это увеличение числа слоёв с одновременным сокращением шага между слоями. И то и другое ведёт к росту сопротивления линии wordline (WL), соединяющей ячейки в строке матрицы. Этот рост приходится тем или иным образом компенсировать, иначе пострадают быстродействие и энергоэффективность.

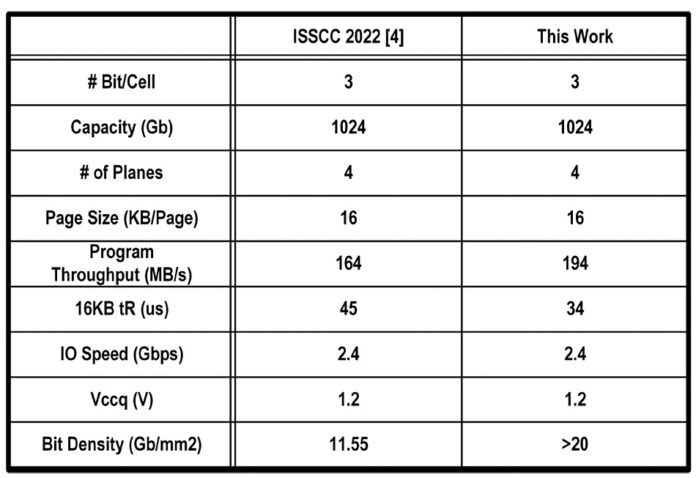

Сравнение 238- и 300-слойной 3D NAND

SK hynix рассказала о гипотетическом чипе памяти NAND с более чем 300 слоями, который состоит из трёхбитовых (TLC) ячеек и может похвастаться ёмкостью 1 Тбит. За счёт увеличения числа слоёв плотность размещения ячеек вырастет с 11,55 Гбит/мм2 у актуальной 238-слойной памяти до более чем 20 Гбит/мм2. Общую производительность памяти предложено поднимать пятью отдельными способами, в целом направленными на ускорение процессов записи, стирания и чтения. Для этого придётся внести изменения в последовательности и тайминги команд.

В частности, предложено реализовать метод тройной проверки программирования (TPGM) вместо ранее двойной проверки DPGM. В новой версии ячейки будут делиться на четыре группы, а не на три. Технология TPGM уменьшает параметр tPROG и это вместе с увеличенной разбивкой примерно на 10 % сократит время программирования ячеек.

Также параметр tPROG уменьшит новая технология адаптивного предварительного заряда невыбранной строки (AUSP). Это ускорит работу с ячейками ещё примерно на 2 %. Ещё немного ускорения получится за счёт снижения ёмкостной нагрузки на линию WL, что обеспечит метод программируемой фиктивной строки (PDS). Метод всепроходного нарастания (APR) даст уменьшение времени считывания (tR), что выразится в сокращении времени реакции линии WL на новый уровень напряжения и улучшит время чтения на 2 %. Наконец, для улучшения качества обслуживания во время стирания применят метод повторного чтения на уровне плоскости (PLRR).

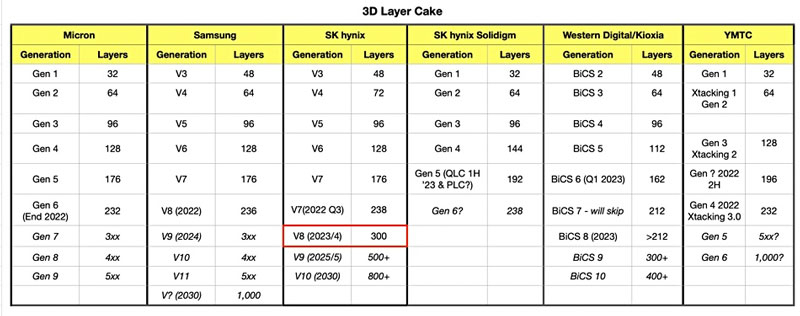

Компиляция по данным о поколениях 3D NAND разных производителей. Источник изображения: blocksandfiles.com

Всё вместе, как сказано выше, позволит поднять скорость работы 1-Тбит 3D NAND TLC компании SK hynix за поколение с 164 Мбайт/с до 194 Мбайт/с с одновременным увеличением плотности записи. Уточним, представители компании не стали и вряд ли могли раскрыть производственный график по выпуску памяти NAND 300+. Можно ожидать, что первые прототипы начнут появляться к концу года или даже не раньше начала 2024 года. Пока же и в течение текущего года в производстве будет находиться память с 230+ слоями, выпуск которой в той или иной степени наладили все главные игроки рынка NAND-памяти.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться