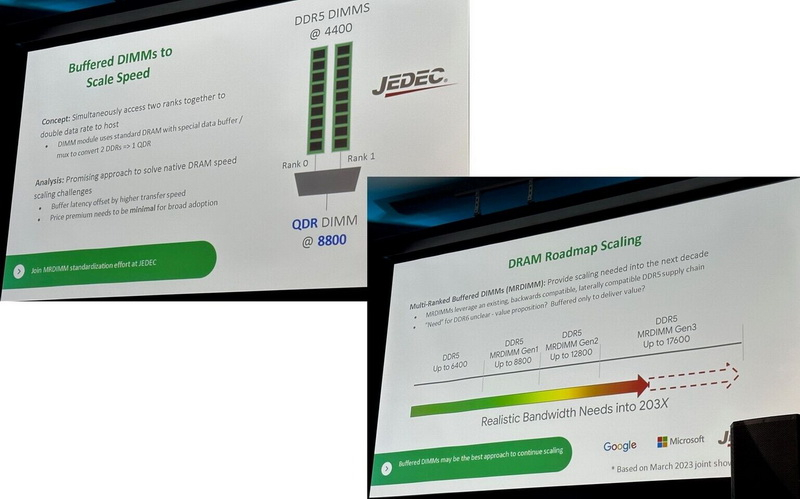

Компания AMD и ассоциация JEDEC ведут разработку нового стандарта оперативной памяти DDR5 в виде MRDIMM-модулей. Это модули DIMM с многоранговой буферизацией, которые должны удвоить пропускную способность по сравнению со стандартными модулями DDR5 DRAM. Такая память в перспективе будет применяться в серверных решениях.

Источник изображения: Tom's Hardware

Необходимость во всё большем объёме оперативной памяти особенно актуальна для серверного направления. Однако простое добавление дополнительных слотов памяти на материнскую плату приведёт к увеличению размеров систем. Использование технологий вроде распаянной высокопроизводительной памяти HBM — дорого и масштабируется только до определённого объёма памяти. Для решения проблемы инженеры JEDEC при поддержке AMD ведут разработку нового стандарта памяти MRDIMM.

Концепция MRDIMM заключается в объединении двух модулей DDR5 и одновременном использовании обоих рангов. Например, при объединении таким образом двух модулей DDR5 со скоростью 4400 МТ/с, на выходе получится 8800 МТ/с. По словам разработчиков, для этого используется специальный буфер данных или мультиплексор — он объединяет все ранги и преобразовывает два DDR (Double Data Rate — удвоенная скорость передачи данных) в один QDR (Quad Data Rate — четырёхкратная скорость передачи данных).

По сути, представленная технология может заменить собой Compute Express Link (CXL) или High Bandwidth Memory (HBM). При этом она является более универсальным решением для увеличения эффективности подсистемы памяти, нежели указанные выше методы. Сначала планируют представить версию Gen 1 с возможностью работы на скорости 8800 МТ/с, затем будут представлены версии Gen 2 на 12 800 МТ/с. В более отдалённой перспективе, возможно, после 2030 года, будет представлена версия памяти MRDIMM Gen 3 со скоростью передачи данных 17 600 МТ/с.

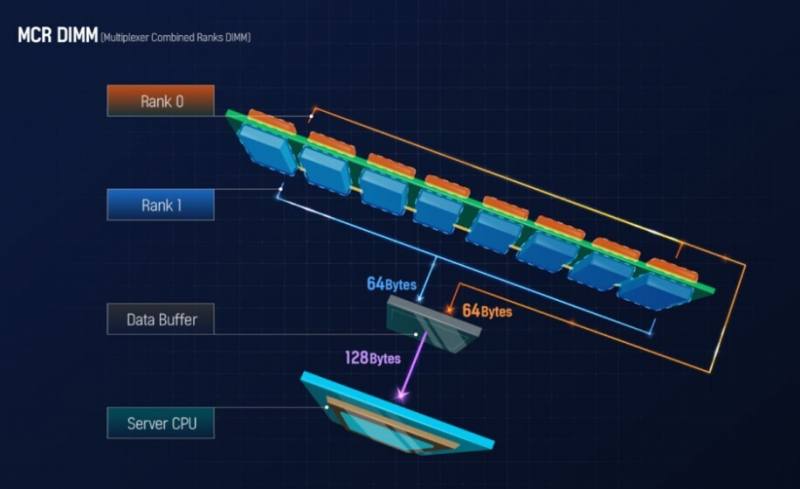

Следует отметить, что у компании SK hynix есть аналогичное решение в виде памяти MCRDIMM (на изображении выше), которое она разработала при поддержке Intel и Renesas. С помощью специального чипа, разработанного Renesas и выступающего в роли буфера данных, SK hynix обеспечила возможность одновременно задействовать два ранга памяти (чипы с обеих сторон модуля) для увеличения ширины канала данных до 128 бит вместо привычных 64 бит. Однако такие решения станут доступны на рынке не ранее 2024–2025 годов, когда появятся новые поколения серверных платформ.

Источники:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться