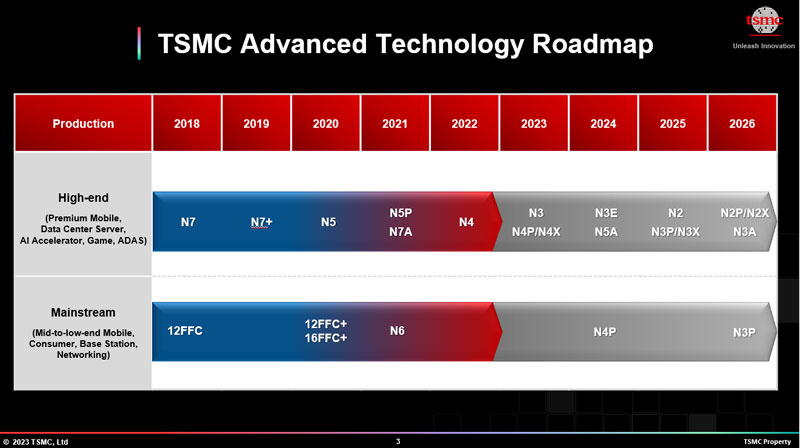

Компания TSMC рассекретила планы совершенствования 2-нм техпроцесса N2, массовое производство по которому должно стартовать в 2025 году. Спустя год после этого будет внедрён оптимизированный по шине питания техпроцесс N2P, а ещё через некоторое время компания запустит техпроцесс N2X для решений с высшей производительностью. Развитие 2-нм техпроцесса TSMC будет стремительным, что может объясняться опасениями TSMC отстать от Intel и Samsung.

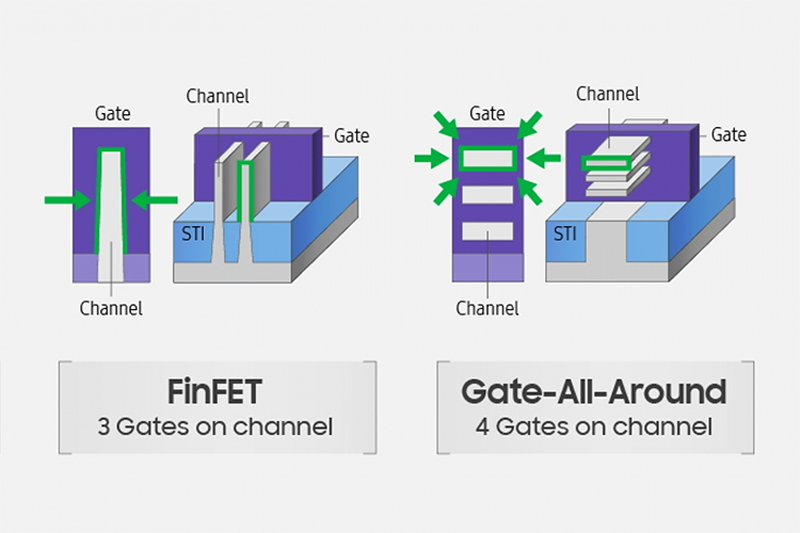

Пример транзисторов с вертикальными рёбрами и круговым затвором (справа). Источник изображения: Samsung

Официально техпроцесс с нормами 2 нм тайваньский чипмейкер представил летом прошлого года. Производство полупроводников с этими технологическими нормами начнётся в 2025 году. Главной особенностью техпроцесса N2 станет переход с FinFET на транзисторы с круговым затвором (GAAFET). Это снизит токи утечки, позволит гибко регулировать производительность и оптимизирует потребление. Другой важной особенностью техпроцесса N2 должен был стать перенос линий питания чипа на другую сторону кристалла, что будет означать развязку шины данных и управления с питанием.

Источник изображений: TSMC

Как теперь становится понятно, перенос линий питания ожидается в процессе внедрения техпроцесса N2P, что произойдёт в 2026 году. Из предыдущих заявлений компании первой реализации идеи можно было ожидать в 2025 году. Разнесение интерфейсов питания и данных по разные стороны кристалла решает множество проблем. Так, линии подвода питания к транзисторам станут короче, что снизит их сопротивление. Разнесение разводки уменьшит площадь кристаллов, львиную долю которой съедали линии передачи и межслойные контакты. Наконец, хотя это не всё, снизятся взаимные помехи, что скажется на стабильности сигнальных характеристик чипов.

Снижение площади кристалла, занятой контактами и разводкой, приведёт к значительному увеличению плотности транзисторов. Ранее TSMC заявляла, что переход от техпроцесса с нормами 3 нм к нормам 2 нм увеличит плотность транзисторов на 10 %. К настоящему моменту прогноз был улучшен до 15 % и, в случае внедрения техпроцесса N2P, плотность может вырасти на двухзначную величину, которую компания пока не конкретизирует. Закон Мура вздохнёт ещё раз перед своей смертью.

О техпроцессе N2X, который будет внедряться в 2026 году или позже, компания ничего не сообщила. Можно предположить, что это будет не слишком распространённое предложение, тогда как техпроцесс N2P обещает стать рабочей лошадкой компании на этапе 2-нм производства чипов.

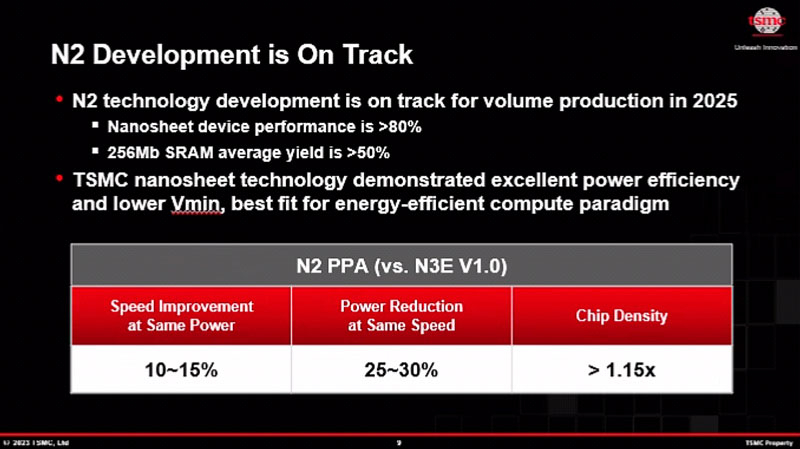

Также компания сообщила о прогрессе в подготовке базового 2-нм техпроцесса. Производительность транзисторов GAAFET в составе опытного кремния доходит до 80 % от целевых значений. И это за два года до начала внедрения, что очень и очень хорошо. При этом уровень брака при производстве 2-нм ячеек SRAM объёмом 256 Мбит снизился до 50 % и менее.

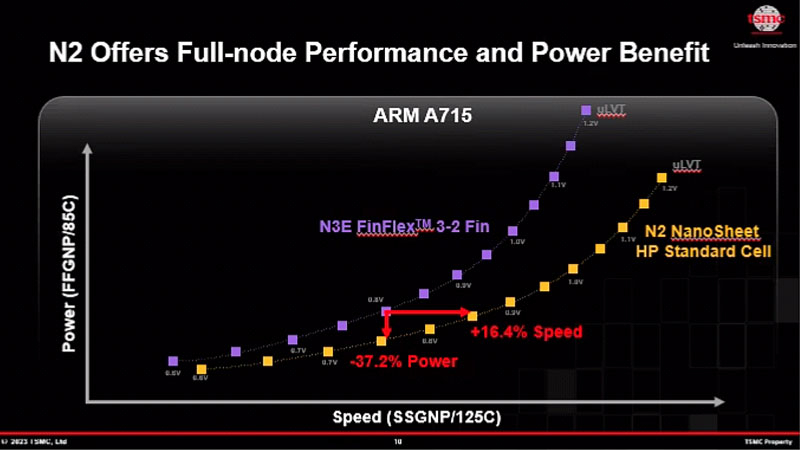

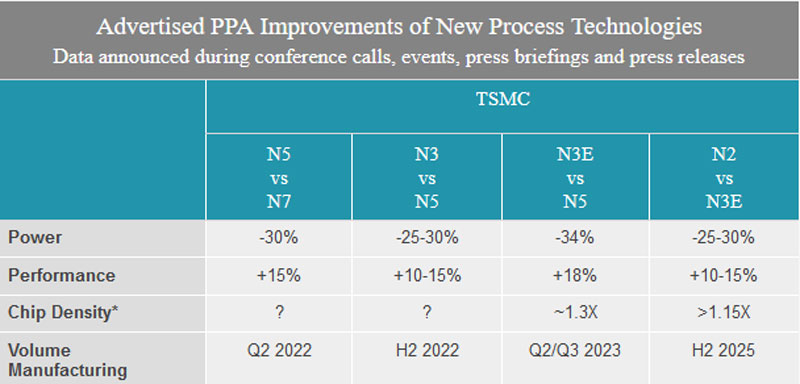

Источник изображения: Anandtech

В целом техпроцесс с нормами 2 нм позволит TSMC повысить производительность транзисторов на 10–15 % при той же мощности и сложности, или снизить энергопотребление на 25–30 % при тех же тактовых частотах и количестве транзисторов. На бумаге TSMC отстаёт от компании Intel на год или два и успехи одной из компаний не дают покоя другой. Если каждая из них сдержит обещания, то чипы TSMC с транзисторами GAAFET появятся на два года позже аналогичных чипов Intel (20A), что также касается планов переноса линий питания на обратную сторону кристалла.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться