Так называемое второе поколение 3-нм техпроцесса в исполнении TSMC обычно фигурировало во внутренних документах тайваньской компании под обозначением N3E и было привязано по срокам внедрения ко второй половине 2023 года. На минувшей квартальной конференции представители TSMC уточнили, что к массовому производству чипов по технологии N3E компания будет готова приступить в четвёртом квартале текущего года.

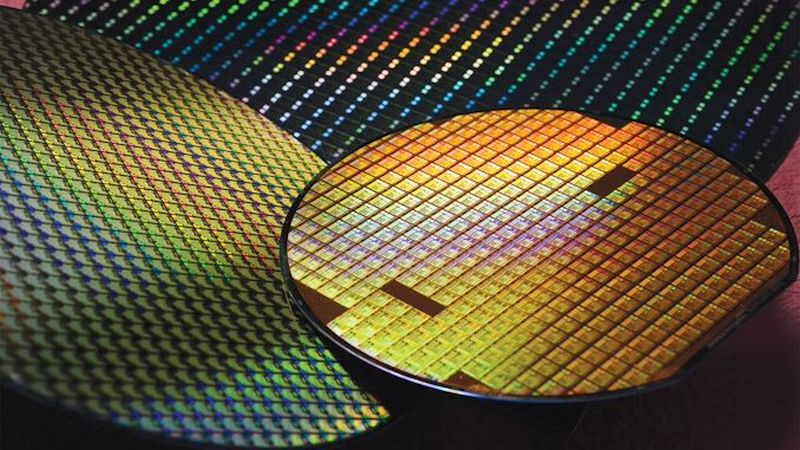

Источник изображения: TSMC

Генеральный директор TSMC Си-Си Вэй (C.C. Wei) на отчётом мероприятии в конце этой недели заявил буквально следующее: «N3E расширяет наше семейство N3 за счёт возросшего быстродействия, сниженного энергопотребления и уровня выхода годной продукции, а также обеспечивает полную поддержку платформ как в сегменте высокопроизводительных вычислений, так и для применения в смартфонах. N3E прошёл квалификационные тесты, достиг целевых показателей по быстродействию и уровню брака, в массовое производство он будет запущен в четвёртом квартале этого года».

Напомним, если базовый вариант техпроцесса N3, который компания TSMC использует для массового производства компонентов по заказу той же Apple с конца прошлого года, обеспечивает снижение энергопотребления до 25–30 %, улучшение производительности на 10–15 % и экономию площади кристалла до 42 % по сравнению с техпроцессом N5, то в случае с N3E за счёт некоторого уменьшения плотности размещения транзисторов (на 7,8 % по сравнению с N3) предлагает более высокий уровень выхода годной продукции и упрощение самого производства, что благоприятно сказывается и на себестоимости продукции. Кроме того, N3E увеличивает экономию в энергопотреблении до 32 % по сравнению с N5, а производительность транзисторов возрастает на 18 % вместо 15 % у базового N3.

По сути, N3E лишь немногим жертвует с точки зрения плотности размещения транзисторов по сравнению с N5: она увеличивается в 1,6 раза вместо 1,7 раз у более дорогого в производстве N3. Как ожидается, N3E сможет привлечь большее количество клиентов к услугам TSMC, чем это удалось N3. Впрочем, даже базовый вариант своего 3-нм техпроцесса руководство компании считает лучшим на рынке с точки зрения производительности, плотности размещения транзисторов и энергопотребления, а потому подчёркивает, что во второй половине текущего года объёмы выпуска чипов с его использованием заметно возрастут, причём как в сегменте высокопроизводительных вычислений, так и в сегменте смартфонов.

Руководство TSMC на этой неделе также выразило надежду, что семейство 3-нм техпроцессов в исполнении компании сформирует долговременный спрос со стороны клиентов, и этот технологический цикл будет долгоиграющим с точки зрения продолжительности присутствия на рынке. Базовый техпроцесс N3 к концу этого года будет формировать от 4 до 6 % совокупной выручки компании, хотя пока в отчётности TSMC он вообще не упоминается, хотя фактически используется в серийном производстве с начала текущего года, как минимум.

Этими двумя разновидностями 3-нм техпроцесса TSMC ограничиваться не собирается. Ко второй половине следующего года компания готовится освоить техпроцесс N3P, который снизит энергопотребление на 5–10 % по сравнению с N3E, поднимет быстродействие на 5 % и на 4 % увеличит плотность размещения транзисторов. К 2025 году специально для самых производительных чипов будет внедрён техпроцесс N3X, который позволит применять более высокие напряжения и поднимет быстродействие как минимум на 5 %, но ценой более высокого энергопотребления по сравнению с N3P. Зато плотность размещения транзисторов «трогать» не будут, и она останется на одном уровне с N3P. С этой точки зрения жизненный цикл 3-нм техпроцессов в производственной программе TSMC действительно будет продолжительным.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018