⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

Отечественные микропроцессоры. Были! Есть. Будут?

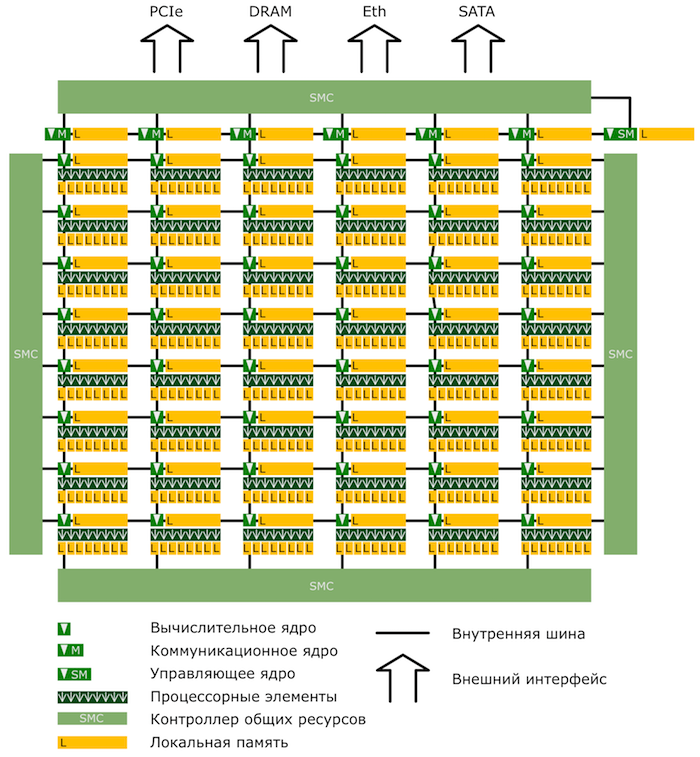

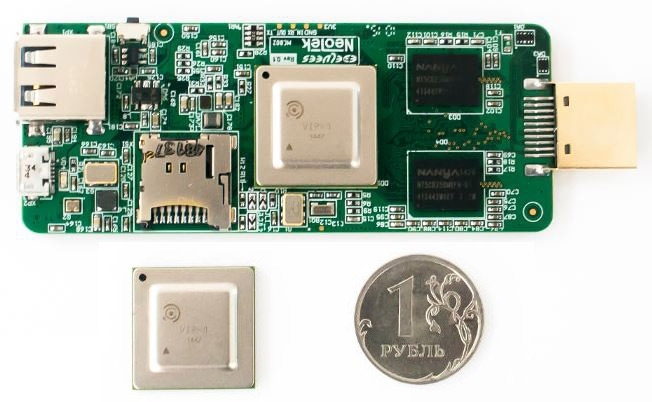

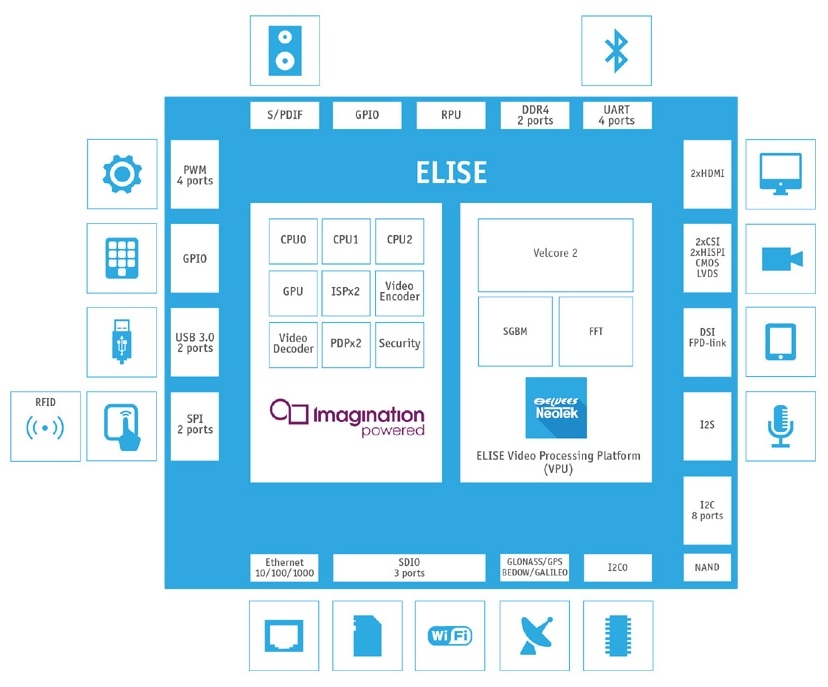

Самая известная отечественная архитектура CPU, которая постоянно вызывает горячие споры, — "Эльбрус e2k". Это последняя из VLIW-реализаций «больших» процессоров общего назначения после ухода Itanium на покой, хотя различные ускорители, DSP и вычислительные блоки до сих пор используют её. Бытует мнение, что VLIW-подход при разработке новой архитектуры был выбран по экономическим соображениям. Да, VLIW, исполняя много инструкций за один цикл, способен показывать хорошую производительность, особенно при возможности распараллеливания. Подход VLIW, грубо говоря, позволяет избавиться хотя бы на начальном этапе от реализации в кремнии традиционных для других архитектур предсказателя ветвлений и суперскалярности, которые вкупе со спекулятивными вычислениями привели к появлению нашумевших уязвимостей Spectre и Meltdown. Это значительно удешевляет разработку и производство СБИС, но перекладывает все эти задачи оптимизации на компилятор, хотя для того же "Эльбруса" проекты по созданию предсказателя не новы. Естественно, требуются собственные оптимизирующие компиляторы как минимум для популярных языков программирования. Но этого мало, нужны ещё переписанные стандартные библиотеки, системные утилиты, средства разработки, адаптированные реализации самых распространённых алгоритмов — и так далее. Чаще всего простой пересборкой проекта (без внесения правок в код) при портировании ПО между принципиально разными архитектурами не обойтись. И, скажем так, ходят слухи, что этот этап подходит к завершению только сейчас (хотя улучшать-то можно бесконечно), но всё равно есть разного рода нюансы вроде весьма своеобразного отношения к стандартам C++ компилятора для "Эльбрусов". Впрочем, в качестве запасного варианта есть динамическая бинарная трансляция x86, позволяющая, пусть и с потерями производительности, запускать уже имеющиеся ОС и ПО. Процессоры массово выпускаются с середины 2000-х и имеют множество модификаций с числом ядер от одного до восьми (на текущий момент). Версии для техпроцесса 90 нм и толще производятся в России, а более тонкие — на зарубежных фабриках (TSMC). Отличительная черта серии — поддержка создания многопроцессорных систем для почти всех моделей, хотя скорость шины для попарного общения CPU — CPU или CPU — мост пока равна 16 Гбайт/с (по 8 в каждую сторону). Не умением, так числом. Другая черта, причем не самая лучшая, касается коммуникации с внешним миром. Текущая версия южного моста КПИ-2 имеет в сумме только 20 линий PCI-E 2.0, а их при построении вычислительных систем сейчас явно мало, так как интерконнект, накопители, ускорители их очень и очень любят. Совместимых с КПИ-2 процессоров сейчас есть только три: "Эльбрус-8С" (28 нм) и "Эльбрус-1С+" (40 нм), а также R2000, упомянутый в разделе про SPARC. Оба "Эльбруса" используют архитектуру четвёртого поколения и способны выполнять до 25 операций за такт. "Эльбрус-8С" — это серверный процессор, содержащий 8 ядер, которые работают на частоте 1 или 1,3 ГГц. Он имеет производительность 250 Гфлопс FP32, а энергопотребление старшей версии не превышает 80 Вт. В связке могут работать сразу четыре CPU. Четырёхканальный контроллер памяти поддерживает до 64 Гбайт DRR3-1600 ECC. В этом году должны быть завершены ОКР для его наследника под названием "Эльбрус-8СВ", построенного на следующем поколении архитектуры: 28 нм, 8 ядер × 1,5 ГГц, до 50 операций на такт, 576 Гфлопс FP32, четыре канала DDR4-2400 ECC. В планах есть создание чипов "Эльбрус-16С" и "Эльбрус-16СВ". Последний ориентирован на суперкомпьютеры и должен быть готов к 2021 году. Он отличается не только повышенной производительностью (2 ГГц, 1,5 Тфлопс FP32) и более тонким техпроцессом (16 нм), но и набором шин. Собственно говоря, это будет уже SoC с контроллерами PCI-E 3.0 и 10 GbE. При этом потребляемая мощность должна быть равна 100 Вт. "Эльбрус-1С+" — тоже SoC, но для компактных или встраиваемых систем. Данная модель содержит одно ядро "Эльбрус", которое работает на частоте до 1 ГГц и имеет производительность до 24 Гфлопс FP32. Двухканальный контроллер памяти DDR3-1600 ECC поддерживает установку 32 Гбайт RAM. Основная «фишка» данной SoC в наличии видеоядер: 2D-ядро MGA2 собственной разработки МЦСТ и отключаемое 3D-ядро GC2500, лицензированное у Vivante. Как и все CPU "Эльбрус", данная модель имеет расширенный диапазон рабочих температур: от -60 до +90° C. Последний из официально представленных продуктов на основе этой SoC был анонсирован несколько недель назад. Это защищённый «внедорожный» ноутбук под кодовым именем ЕС1866. С продуктами на базе CPU "Эльбрус", показанными на выставке "Иннопром-2018", можно ознакомиться в видео ниже. Ну и в целом можно полистать канал автора, если тема "Эльбрусов" интересна. Разработкой готовых решений на базе "Эльбрусов" занимается родственное предприятие ИНЭУМ. Ещё один относительно молодой проект по созданию SoC/CPU. "КВАРК" (KVARC) основан на 32-бит RISC-архитектуре собственной разработки. На основе "КВАРК" компания-разработчик КМ211 предлагает серии ядер "КРОЛИК" КМx8 и КМx32 для микроконтроллеров, которые могут применяться, например, в SIM- или смарт-картах. Есть у компании и готовый вариант микроконтроллера "МАСТЕР КРОЛИК". Сравниваются они с ARM Cortex-M3/M0 и Synopsys DesignWare ARC 601/605. Отдельно подчёркивается, что выпускаться кристаллы могут и в России. Тем интереснее сводная таблица характеристик. Также там приводятся показатели производительности: 2,3 CoreMark/МГц. Для сравнения можно обратиться к обзору "Байкал-Т1", у которого этот показатель немного превышает 5 CoreMark/МГц в пересчёте на ядро (или 10 для всего процессора), но энергопотребление выше. На базе той же архитектуры разработан и микропроцессор общего назначения "МАСТЕР КВАРК" с рабочей частотой до 1450 МГц. Для него подготовлены компилятор и базовые библиотеки, а также портированы ОС Linux 3.4, неназванная версия Android и FreeRTOS. "Мультиклет" (MultiClet) — ещё одна отечественная неклассическая архитектура CPU одноимённой компании. Для понимания её устройства можно почитать критику (там же поиском можно найти и другие материалы о платформе) и ответ разработчиков, ознакомиться с принципами EDGE и документами на "Мультиклет", обратив внимание на метод подсчёта Гфлопс. Сами создатели отмечают, что архитектура универсальная и не имеет аналогов. Из интересных особенностей стоит отметить параллелизм и потенциальную масштабируемость программ на любое число клеток без изменения кода, а также отказоустойчивость путём переноса задач на другие клетки в случае отказа одной из них или одновременное выполнение одного и того же кода на нескольких клетках с последующим арбитражем. Помимо чипов на 180-нм техпроцессе, компания производит собственные платы и устройство «Цифровой Страж Key_P1 MultiClet» для защиты (шифрования и контроля доступа) SD- и USB-накопителей. Ранее была информация о разработках настольного (2,4 Тфлопс) и портативного (150 Тфлопс) суперкомпьютеров, плат ускорителей (80 и 300 Тфлопс) и криптотелефоне (чип R1) с шифрованием по ГОСТ. Теперь же заговорили о добыче криптовалют, для которой готовится версия чипа MultiClet S1. Сейчас компания предлагает несколько вариантов своих мультиклеточных ядер различных производительности и исполнения: P1, P2, C1, R1, L1. Сравнение производительности "Мультиклет" и других продуктов приведено здесь. В презентации также есть данные по CoreMark для P1 и R1 — лучшие результаты равны 0,31 и 0,56 CoreMark/МГц. MALT (Manycore Architecture with Lightweight Threads) – относительно молодой российский проект по созданию многопроцессорных кристаллов, хотя их хочется назвать всё же ускорителями, сопроцессорами или как-то ещё, а не просто CPU. Первые образцы 96-ядерной версии кристалла MALT-C 9Mb96G были получены в конце прошлого года. Данный кристалл содержит 9 RISC-ядер общего назначения (ранее разработчики говорили, что выбрали MB-Lite) и три SIMD-кластера по 32 ядра MALT. Энергопотребление кристалла с частотой 800 МГц равно 1 Вт, изготовлен он был по 28-нм техпроцессу на TSMC, хотя адаптировать производство можно и для отечественных фабрик с более «толстым» техпроцессом. Второе поколение MALT «в кремнии» рассчитано уже на 16 нм TSMC. Впрочем, ранее сами создатели использовали ПЛИС для прототипирования систем, включающих до 210 ядер, и, что самое главное, активно занимались созданием программной инфраструктуры для проекта. Разработчики предлагают инструменты для работы с C++, OpenCL и собственный пакет MALTCC, по духу близкий к CUDA.  Компания предлагает три версии MALT. Модификация MALT-C ориентирована на работу с блокчейном и шифрованием. Вариант MALT-D нужен для работы с большими массивами данных, БД и графами, а MALT-F создаётся для расчётов задач математической физики. Сравнение эффективности приведено здесь. В планах есть разработка GPU на базе архитектуры MALT. В брошюре также приведены данные об общих характеристиках возможной SoC: частота до 1,2 ГГц, до 256 ядер общего назначения, до 1024 ядер MALT, до 96 Гбайт DDR3, интерфейсы PCI-E/1GbE/SATA, TDP до 50 Вт. На сайте компании можно подробнее ознакомиться с разработками, да и вообще очень отрадно, что создатели открыто рассказывают о своих продуктах, в отличие от некоторых других отечественных компаний. Буквально пару слов стоит сказать о проекте Leonhard МГТУ им. Н. Э. Баумана — принципиально новом процессоре с собственным набором команд DISC (Discrete Mathematics Instruction Set computer, операции дискретной математики). Утверждается, что он сравним по производительности с Intel Pentium (2 ГГц) при работе уже на 100 МГц благодаря параллелизму. Причём концепция работы отличается — вместо привычных SIMD предлагается MISD (много инструкций, одни данные). Однако универсальным его назвать всё-таки нельзя, но он может дополнять имеющиеся процессоры или блоки в них. Leonhard нужен «для обработки множеств, структур данных и графов». В презентации приведены следующие области применения новинки: ускорение работы с графами, анализ больших данных, компьютерное зрение, работа с финансово-экономическими моделями, машинное обучение, программно-определяемые сети (SDN) и так далее. Естественно, на таких задачах он намного более энергоэффективен обычных CPU, так что может быть использован во встраиваемых и ультракомпактных решениях или SoC. Впервые прототип Leonhard был представлен в прошлом году, а сейчас ведётся разработка второй версии. До реализации где-то, кроме FPGA, пока далеко. В целом же по чисто внешним признакам и области задач Leonhard чем-то напоминает умерший проект Micron Automata, который в массовое коммерческое производство так и не попал (это не значит, что он вообще не производился для конкретных заказчиков). Цифровые сигнальные процессоры (DSP) не являются CPU общего назначения, но от этого они не менее важны. DSP могут быть очень эффективными, но только в узком диапазоне задач (типов вычислений и данных), так что ко всем данным о флопсах надо подходить с осторожностью. Архитектурно они очень различаются и между собой, и в сравнении с обычными CPU — часто встречается модифицированный гарвардский подход. Наиболее удачные варианты могут лицензироваться или реимплементироваться другими компаниями. Впрочем, в России есть и свои собственные решения. ⇡#NeuroMatrixЭто разработка НТЦ «Модуль», ориентированная на векторно-матричые операции над данными и сочетающая подход VLIW и SIMD. Разрабатывается и производится с 90-х годов. Современные модули имеют частоту 500 МГц, производятся по 65-нм техпроцессу и потребляют 2,6 Вт. Разработчик также предлагает готовые SoC с ядрами общего назначения ARM/PowerPC и ядрами NeuroMatrix. Также несколько лет назад был выпущен микрокомпьютер MB77.07 на базе одной из таких SoC. Его почему-то многие называли «отечественными Raspberry Pi», хотя он был полезен именно для изучения и программирования ядер NeuroMatrix. Та же платформа используется при создании ТВ-приставок, а для прочих решений есть свои комплекты разработчиков. DSP NeuroMatrix подходят для обработки/фильтрации/анализа цифровых сигналов, (де-) кодирования мультимедиа, цифровой радиосвязи, навигации, компьютерного зрения, ну и собственно нейронных сетей. ⇡#"Мультикор""Мультикор" (Multicore) — разработка АО НПЦ «ЭЛВИС». DSP основываются на собственной архитектуре, сочетающей, упрощённо, VLIW- и SIMD/MIMD-подходы. Именуются как ELcore-xx. Производятся как простые чипы с ELcore + MIPS32 RISCore32 (видимо, это вариация MIPS R3000) собственной разработки, так и более сложные SoC — с ARM-ядрами общего назначения (опционально доступны FPU-блоки), GPU и прочей обвязкой. Вариантов микросхем не так уж мало, к тому же DSP-блоки могут использоваться и в сторонних решения. Например, четыре ядра ELcore9 входят в состав "Эльбрус-2С+". Разброс частот, техпроцессов и производительности велик. К примеру, микросхема 1892ВМ10Я с двумя ядрами ELcore-30M (130 нм) на частоте 250 МГц потребляет 1,5 Вт и имеет производительность 4 Гфлопс (FP32?, см. выше замечание про флопсы). А вот для SoC «Мультиком-02» (МСom-02, 1892ВМ14Я) или VIP-1 (ВИП-1) штатная частота DSP равна уже 672 МГц (в пике 912 МГц), а потребляет она 3 Вт (ТП 40 нм).  Этот чип также отличается богатым набором интерфейсов и отдельным видеокодеком VELcore-01, обеспечивающим (де-) кодирование H.264 CBP Full HD-видео в стерео при 30 кадрах/с. На основе этой же микросхемы в прошлом году был представлен отладочный модуль в формате микро-ПК «Салют-ЭЛ24Д2», а в этом году модуль «Салют-ЭЛ24ПМ». Грядущая SoC ELISE на 28-нм техпроцессе будет иметь уже второе поколение кодека VELcore-2. Области применения у ELcore, в общем, те же, что и у NeuroMatrix. Родственная компания «ЭЛВИС-НеоТек» занимается разработкой и продажей готовых решений на базе продукции «ЭЛВИС». В частности, в серию с говорящим названием Orwell входят системы интеллектуального наблюдения, обнаружения и отслеживания объектов в видимом, ИК- и радиодиапазонах. Частный случай — система «Перекрёсток» (Travio) для автоматической фиксации нарушений ПДД. Компания занимается и созданием камер. В конце мая была представлена модель VisorJet 720: 24 Мп, обзор 360° × 360°. Эти камеры будут снабжаться SoC ELISE.  В статье приведён далеко не полный перечень современных отечественных разработок в области микроэлектроники. Если эта тема интересна, то можно начать более глубокое знакомство с каталогов и сайтов наиболее заметных производителей, таких как "Ангстрем", "Микрон", "Модуль", "Миландр", "Мультиклет", "Элвис", НИИЭТ, "Прогресс", НИИСИ РАН, МВЦ, МЦСТ, ИНЭУМ, ВЗПП-С. Также можно посмотреть на перечень испытанных ЭНПО СПЭЛС компонентов. Есть и специализированный сервис «Справочник ЭКБ ОП», но доступ к нему платный. Всю остальную информацию придётся искать самостоятельно в Сети, а лучше — в специализированных журналах, в том числе научных. Если повезёт, конечно, потому что иногда можно встретить вскользь брошенные упоминания об очередной разработке, жалобы на забюрократизированность, обсуждения несовместимости и так далее, но только не детальную информацию. В целом же можно сказать, что процессоростроение в России не умерло. Да, оно находится, пожалуй, далеко не в лучшем состоянии, но точно не умерло. Флагманом остаётся серия "Эльбрус", которая продолжает развиваться и внедряться. Ряды МЦСТ R-xxxx совсем недавно пополнились новой моделью, так что эта серия тоже не заброшена. Обе серии создаются для госнужд, так что за безопасность готовы платить и дальше — это к постоянным негодованиям по поводу их цены. Для задач попроще, но в той же области есть серии "КОМДИВ-32/64", а также "КВАРК". В переходной, так сказать, области находятся "Байкалы" — они не создавались строго для госзаказчиков, но из-за этого компании придётся приложить усилия по продвижению своих продуктов для гражданского сектора, и не только отечественного. В ещё большей степени это касается наших разработчиков изделий на базе RISC-V. Из неклассических отечественных архитектур производятся изделия "Мультиклет", но они ожидаемо весьма специфичны. Разработка MALT доросла до стадии прототипов в «кремнии», а проект Leonhard пока слишком молод, чтобы его реально оценивать. Наконец, DSP "Мультикор" и NeuroMatrix давно разрабатываются и производятся. Впрочем, как уже говорилось в самом начале, реально оценить и сравнить масштабы и конкуретоспособность российской микроэлектроники непросто. Остаётся только надеяться, что планировавшаяся когда-то стратегия Минпромторга по развитию отечественной радиоэлектроники до 2030 года, в которой говорилось о возможности занять 2 % мирового рынка этой продукции, не останется очередным примером необоснованных амбиций.

⇣ Содержание

Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|