|

Опрос

|

реклама

Быстрый переход

TSMC запланировала начать опытный выпуск чипов по субнанометровому техпроцессу A10 к 2029 году

18.04.2026 [15:37],

Павел Котов

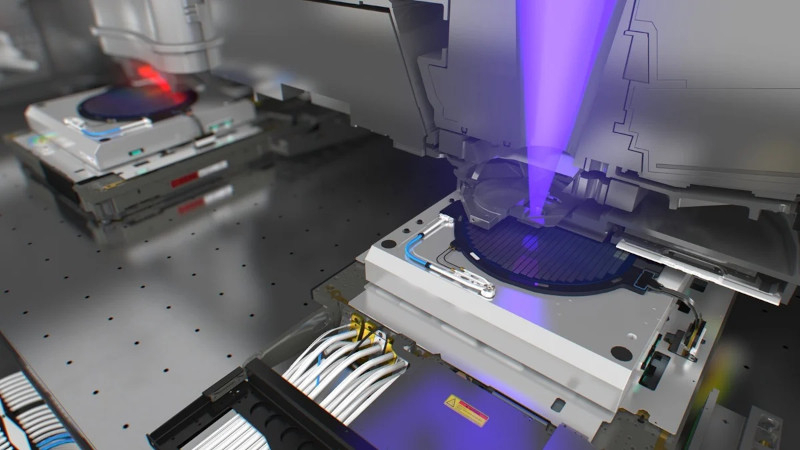

На техпроцесс 3 нм за I квартал пришлись 25 % выручки, рассказал в ходе брифинга, посвящённого финансовым показателям TSMC по итогам финансового года, глава компании Си Си Вэй (C.C. Wei). Он рассказал о планах компании на ввод новых производственных мощностей по выпуску чипов по нормам 3 нм на Тайване, в США и Японии в период с 2027 по 2028 годы, а также поведал о планах внедрения технологии CoPoS, передаёт Digitimes.

Источник изображений: tsmc В Научном парке Южного Тайваня TSMC планирует построить новый завод по производству чипов с использованием техпроцесса 3 нм; массовый выпуск начнётся в первой половине 2027 года. Второй завод в американской Аризоне также будет использовать технологию 3 нм; начало производства намечено на вторую половину 2027 года. На техпроцесс 3 нм будет переведён второй завод в японском Кумамото; здесь начало производства запланировано на 2028 год. На Тайване существующее оборудование для выпуска продукции по нормам 5 нм будет переоснащено под 3 нм. Заводы P1 и P2 комплекса F20 в городке Баошан (уезд Синьчу) будут специализироваться на техпроцессе 2 нм; P3 сможет работать как с 2 нм, так и с A14. Завершение строительства запланировано на середину 2026 года. Заводы P1 и P2 комплекса F22 в Гаосюне ориентированы на техпроцесс 2 нм; P3 и P4 будут работать с 2 нм и A16. Установка оборудования на P3 начнётся во II квартале 2026 года; завершение строительства P4 намечено на январь 2027 года. P5 и P6 находятся на стадии планирования; все предприятия будут иметь мощность от 20 000 до 25 000 пластин. В Тайнане запланировано строительство комплекса A10, где на заводах P1–P4 будут разрабатываться передовые техпроцессы по нормам менее 1 нм; в 2029 году стартует опытное производство объёмом около 5000 пластин в месяц. Сейчас завод P1 площадки F21 в Аризоне производит чипы по нормам 4 нм с мощностью 20 000–25 000 пластин в месяц. На заводе P2 будет использоваться техпроцесс 3 нм; оборудование будет установлено в III квартале этого года. Предприятия P3, P4 и P5 будут специализироваться на технологиях 2 нм, A16 и A14 соответственно. Запланированы ещё шесть производственных площадок и в общей сложности 11 заводов.  Запуск строительства первого современного завода по производству корпусов запланирован на вторую половину 2026 года, ввод в эксплуатацию — к 2028 году. Спрос на упаковку CoWoS остаётся высоким: завод AP8 P1 в Тайнане к концу года рассчитывает увеличить мощность до более чем 40 000 единиц продукции в месяц. Завод AP7 P1 в Чиайи специализируется на WMCM и в основном обслуживает Apple; предприятие P2 займётся выпуском SoIC. Установка оборудования на P2 начнётся в июне 2026 года при целевой ежемесячной мощности 12 000 единиц, ещё 10 000 единиц в месяц обеспечит завод AP6 в Чжунане. Первоначально планировалось, что массовое производство CoPoS стартует в 2028 году, но сроки пришлось перенести. Установка оборудования для исследований и разработки начнётся только в III квартале 2026 года; ещё год займёт строительство опытной линии, к III кварталу 2027 TSMC планирует разместить заказы на оборудование. Оборудование для опытной линии поступит на завод P7 в Чиайи ко II кварталу 2028 года, далее около года уйдёт на проверки и доработку. Заказы на оборудование для серийного производства будут размещаться к середине 2029 года; поставят его к I кварталу 2030 года; а готовая продукция начнёт выходить, вероятно, лишь в IV квартале 2030 года. Проект CoWoP при сотрудничестве Nvidia и Siliconware Precision Industries (SPIL) могут отложить из-за высоких технической сложности и стоимости — SPIL и тайваньские производители печатных плат проявляют к нему низкий интерес, и поддерживают проект в основном китайские компании. Intel намерена заполучить миллиардные заказы Google и Amazon на упаковку чипов

07.04.2026 [10:03],

Алексей Разин

Уже около полутора лет Intel пытается поднять привлекательность собственных контрактных услуг, и одним из направлений развития сделала упаковку чипов сторонней разработки. Сейчас она пытается обзавестись крупными заказами Google и Amazon, чтобы начать для них упаковку чипов на своих предприятиях в штате Нью-Мексико.

Источник изображения: Intel По крайней мере, на это ссылается издание Wired. До появления на этом участке площадью более 80 га предприятий Intel в восьмидесятых годах прошлого века, здесь функционировала ферма по выращиванию дёрна. В 2007 году Intel пришлось остановить работу предприятия Fab 9 в Нью-Мексико, местные жители даже рассказывали о заселении пустующих корпусов енотами и барсуками, но в 2024 году площадка вернулась к жизни после свежих капитальных вложений. По так называемому «Закону о чипах» Intel было получено около $500 млн целевых субсидий на развитие данной площадки. Теперь Fab 9 и соседняя F11X сосредоточились на услугах по упаковке полупроводниковых чипов. Руководство Intel рассчитывает, что в ближайшие пару лет выручка компании от оказания услуг по упаковке чипов сможет измеряться многими сотнями миллионов долларов в год, а в идеале вырастет и до $1 млрд. По имеющимся данным, сейчас Intel ведёт переговоры о предоставлении таких услуг как минимум с двумя потенциальными крупными клиентами. Ими могут стать Google и Amazon, которые разрабатывают собственные ИИ-чипы, но поручают их выпуск специализированным подрядчикам. Даже если Intel не сможет обрабатывать для них кремниевые пластины, она планирует получить заказы на упаковку чипов Google и Amazon. Представители всех трёх компаний комментировать что-либо Wired отказались. Intel одновременно расширяет свои мощности по тестированию и упаковке чипов в Малайзии, которые существуют там с семидесятых годов прошлого века. С 2017 года Intel продвигает технологию упаковки многокристальных чипов EMIB, которая подразумевает наличие общей подложки. Двумя годами позже появилась технология интеграции чипов Foveros, а новейшей версией метода объединения разнородных чипов Intel может считать EMIB-T. Его массовое применение на предприятиях компании начнётся в этом году, причём именно в штате Нью-Мексико. По словам представителей Intel, в новых рыночных условиях компания готова принимать обработанные кремниевые пластины от заказчиков, чтобы заниматься их частичной упаковкой, а затем на нужном этапе возвращать клиентам. Потенциальные клиенты, по мнению некоторых бывших сотрудников Intel, стесняются заявлять о сотрудничестве с нею в силу ряда причин. Во-первых, это может быть неуверенность в способности Intel развернуть соответствующий бизнес в нужных масштабах. Во-вторых, они могут опасаться реакции конкурирующей с Intel компании TSMC. Кроме того, у контрактных производителей не принято говорить о контрактах с клиентами без их согласия, поэтому об использовании услуг Intel первыми должны рассказывать заказчики, а не сама компания. О появлении у Intel крупных заказчиков на контрактном направлении можно будет также судить по росту капитальных затрат со стороны компании. Заключенные контракты позволят оправдать будущие вложения в профильные производственные мощности. ASML расширит ассортимент продукции: к литографам добавится оборудование для передовой упаковки чипов

02.03.2026 [19:44],

Сергей Сурабекянц

ASML является единственным производителем литографического оборудования с экстремальным ультрафиолетовым излучением (EUV), которое имеет решающее значение для производства самых передовых в мире микросхем для ИИ. Тем не менее, компания не останавливается на достигнутом и собирается существенно расширить свою производственную линейку, включив в неё оборудование для сборки, упаковки и корпусирования микросхем.

Источник изображений: ASML ASML активизирует планы по созданию оборудования для упаковки микросхем и начинает разработку инструментов для производства микросхем, которые могут помочь в создании новых поколений передовых процессоров с искусственным интеллектом. «Мы смотрим не только на следующие пять лет, но и на следующие 10, может быть, 15 лет, — заявил главный технический директор ASML Марко Питерс (Marco Pieters). — [Мы рассматриваем] потенциальные направления развития отрасли и то, что ей потребуется с точки зрения упаковки, склеивания и т. д.» В октябре компания повысила Питерса до должности главного технического директора, заменив Мартина ван ден Бринка (Martin van den Brink), который возглавлял технологическое подразделение около 40 лет. ASML также заявила о реорганизации своего технологического бизнеса с целью приоритетного развития инженерных, а не управленческих должностей. Инвесторы уже учли в цене акций доминирование компании в области EUV-литографии и возлагают большие надежды на Питерса и генерального директора Кристофа Фуке (Christophe Fouquet), назначенного в 2024 году. Акции компании с рыночной капитализацией в $560 млрд выросли в этом году более чем на 30 %. Они торгуются примерно по 40-кратному показателю прогнозируемой прибыли, в то время как акции Nvidia торгуются примерно по 22-кратному показателю прибыли.  Использование многослойной компоновки чипов позволяет разработчикам преодолеть ограничения по размеру и увеличить скорость выполнения сложных вычислений. Сложность и точность, необходимые для создания многослойных чипов, сделали некогда низкорентабельный бизнес по упаковке микросхем значительно более прибыльным. Размеры микросхем для ИИ значительно увеличились, поэтому ASML разрабатывает новые системы сканирования и литографические инструменты для создания ещё более крупных чипов. В прошлом году ASML представила сканирующий инструмент XT:260, специально разработанный для производства передовых микросхем памяти, используемых в ИИ, и самих процессоров для ИИ. По словам Питерса, инженеры компании изучают возможности использования дополнительного оборудования «прямо сейчас». Intel представила EMIB-T — технологию упаковки многокристальных чипов с поддержкой HBM4 и UCIe

01.06.2025 [01:48],

Вячеслав Ким

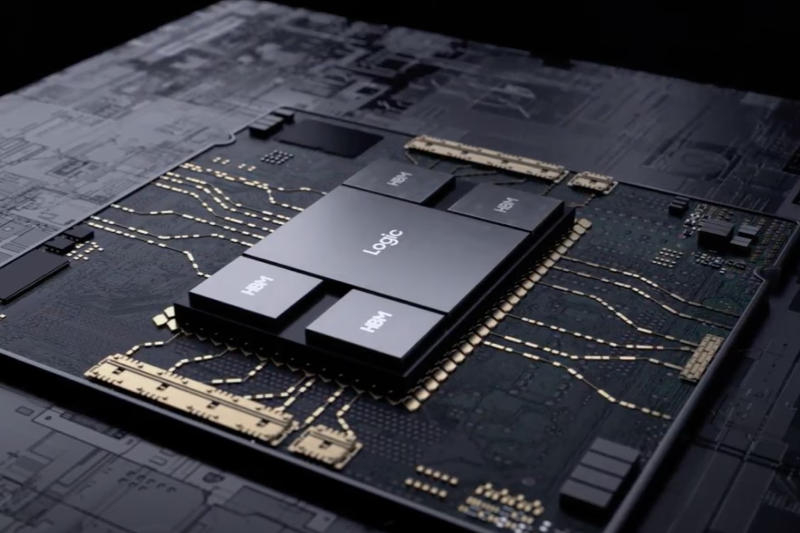

На конференции IEEE ECTC 2025, прошедшей в конце мая в Далласе, Intel анонсировала EMIB-T — усовершенствованную версию своей технологии межкристальных соединений, предназначенную для поддержки высокоскоростной памяти HBM4 и интерфейса UCIe. EMIB-T сочетает в себе элементы 2.5D и 3D-упаковки, обеспечивая улучшенную подачу питания и увеличенную пропускную способность между кристаллами.

Источник изображения: Intel EMIB-T (Embedded Multi-die Interconnect Bridge с TSV) представляет собой развитие существующей технологии EMIB, в которую добавлены сквозные кремниевые переходы (TSV). Это позволяет подавать питание непосредственно через нижнюю часть упаковки, снижая сопротивление и устраняя проблемы с падением напряжения, характерные для предыдущих версий. В результате достигается более эффективная интеграция памяти HBM4 или HBM4e и поддержка интерфейса UCIe-A с пропускной способностью до 32 Гбит/с и выше. Новая технология также позволяет создавать упаковки размером до 120 × 180 мм, содержащие более 38 мостов и более 12 кристаллов. Шаг соединений уменьшен с 55 до 45 микрон, с перспективой снижения до 35 и даже 25 микрон в будущем. EMIB-T совместима как с органическими, так и со стеклянными подложками, что открывает новые возможности для масштабирования и повышения плотности интеграции. Помимо EMIB-T, Intel представила новую конструкцию теплового распределителя, разделённого на плоскую пластину и усиливающий элемент. Это улучшает контакт с теплопроводящим материалом и снижает вероятность образования пустот на 25%. Также была продемонстрирована новая технология термокомпрессионного соединения, повышающая надёжность и выход годных изделий при производстве крупных упаковок. Intel активно сотрудничает с ведущими разработчиками программного обеспечения для проектирования электронных устройств (EDA, Electronic Design Automation), включая Cadence, Siemens и Synopsys, для создания стандартных решений, поддерживающих EMIB-T. Кроме того, компания Keysight объявила о партнёрстве с Intel Foundry для поддержки EMIB-T в своих решениях для проектирования чиплетов, включая поддержку стандартов UCIe 2.0 и BoW. EMIB-T становится ключевым элементом стратегии Intel по объединению различных компонентов, таких как процессоры, графические ускорители и память, в одном корпусе. Это особенно важно в условиях растущих требований к производительности и энергоэффективности в сегментах искусственного интеллекта и центров обработки данных. Новая технология также открывает возможности для более гибкой интеграции компонентов от разных производителей, что соответствует тенденциям развития открытых стандартов в полупроводниковой отрасли. Intel расширит мощности по упаковке чипов в Китае

28.10.2024 [12:04],

Алексей Разин

На фоне отсрочки строительства предприятий по производству чипов в Германии и их упаковке в Польше компания Intel продолжает верить в потенциал китайского рынка, поскольку её местное подразделение сообщило со страниц WeChat о намерениях расширить мощности по упаковке и тестированию чипов в китайском Чэнду. Попутно будет построен новый центр работы с клиентами, который поможет адаптировать продукты Intel под нужды китайских заказчиков.

Источник изображения: Intel Первое предприятие Intel по упаковке чипов появилось в Чэнду ещё в 2004 году, к концу 2005 года оно начало выдавать продукцию. К 2007 году была введена в строй его вторая очередь, которая начала тестировать и упаковывать самые современные процессоры Intel. Сейчас данная площадка входит в тройку самых крупных в составе компании по всему миру. В частности, местное предприятие обрабатывает до половины всех мобильных процессоров, поставляемых компанией Intel. Планы по расширению предприятия Intel в Чэнду сосредоточены на увеличении мощностей, позволяющих тестировать и упаковывать серверные процессоры. Чтобы их можно было адаптировать под нужды конкретных китайских клиентов, рядом с предприятием появится центр работы с клиентами. Компания начала работы по подготовке к строительству запланированных новых зданий в Чэнду, подтверждая тем самым важность китайского рынка для своего бизнеса. Коробки настольных процессоров Intel Core Ultra 200K показались на изображениях в непривычном чёрном цвете

20.09.2024 [16:01],

Павел Котов

Процессоры новой серии Intel Core Ultra 200K будут поставляться в упаковке чёрного цвета, а не привычного синего. Ранее компания Intel выпускала в чёрных коробках только специальные серии чипов для настольных ПК, например, отборные образцы Extreme Edition.

Источник изображений: videocardz.com Накануне в Сеть попала фотография упаковки процессора Intel Core Ultra 9 285K, и инсайдеры поспешили опубликовать изображения упаковок процессоров Core Ultra 7 и Core Ultra 5. На коробках значится маркировка «Unlocked» и «Series 2», то есть речь идёт о процессорах Arrow Lake-S серии Core Ultra 200K, которые предложат разблокированный множитель и соответственно возможность разгона, а их TDP составит 125 Вт.  Ранее компания комплектовала чёрной упаковкой процессоры для энтузиастов серии Extreme Edition, а в последние годы чёрная упаковка применялась для специальных моделей китайского рынка — за пределами Поднебесной такие чипы не продавались. Intel пока воздерживается от публикации подробностей о процессорах нового поколения, и дата их выхода тоже не оглашается.  Если верить неофициальной информации, Core Ultra 200K появятся 24 октября вместе с материнскими платами на новом чипсете Z890. На начальном этапе ожидается дебют лишь пяти моделей, а за ними последуют и другие, включая вариант с TDP 65 Вт и без разблокированного множителя. Десять японских и американских компаний вместе разработают технологии упаковки чипов будущего

11.07.2024 [13:17],

Алексей Разин

Давняя заинтересованность японских производителей чипов в совершенствовании своих технологических возможностей нашла отклик в намерениях американских компаний, которые заинтересованы в доступе к материалам и оборудованию японского происхождения. Десять компаний из обеих стран сформировали консорциум для совместного совершенствования технологий упаковки чипов.

Источник изображения: Resonac Как сообщает являющаяся членом нового объединения японская компания Resonac, альянс получил наименование US-JOINT, а с японской стороны в него вошли несколько компаний, которые Resonac объединила в рамках инициатив JOINT и JOINT2 соответственно. С американской стороны в деятельности консорциума будут задействованы пять компаний, в Калифорнии на нужды этого объединения будет работать специальной созданный исследовательский центр. Строительство центра начнётся уже в этом году, в следующем он уже будет оснащён оборудованием и приступит к работе. Посол США в Японии Рам Эмануель (Rahm Emanuel) подчеркнул, что в условиях высокой зависимости человечества от полупроводниковых компонентов важно укреплять цепочки поставок за счёт международного сотрудничества в соответствующих секторах. US-JOINT будет заниматься разработкой новых материалов и оборудования, необходимых для внедрения прогрессивных методов упаковки чипов, руководствуясь принципом постоянной и оперативной обратной связи с клиентами. Сложные пространственные методы упаковки чипов тоже останутся в фокусе внимания разработчиков. Помимо Resonac, в консорциум US-JOINT вошли Azimuth, KLA, Kulicke & Soffa, Moses Lake Industries, MEC, ULVAC, NAMICS, TOK и TOWA. Власти США выделили $1,6 млрд на разработки передовых технологий упаковки чипов

10.07.2024 [07:43],

Алексей Разин

Принятый ещё в конце 2022 года «Закон о чипах» подразумевает выделение не только $39 млрд на субсидирование строительства новых предприятий по производству полупроводниковых компонентов, но и $11 млрд на исследования и разработки. Из этой суммы $1,6 млрд будут направлены на субсидирование разработок в сфере совершенствования технологий упаковки чипов.

Источник изображения: IBM Об этом сообщает Bloomberg со ссылкой на заместителя министра торговли США Лори Локасцио (Laurie Locascio). Именно это ведомство занимается распределением целевых субсидий по «Закону о чипах». Указанную сумму планируется распределить между пятью направлениями исследований в разных областях, так или иначе имеющих отношение к технологии упаковки чипов. Соответственно, на каждое из направлений исследований может быть выделено до $150 млн субсидирования. Помимо прочего, государственные средства помогут разработчикам создать прототипы изделий, использующие новые технологии упаковки чипов. К одной из категорий относятся оборудования и оснастка, другая объединяет энергоснабжение и методы отвода тепла, третья имеет отношение к соединениям в оборудовании, четвёртая покрывает средства автоматизированного проектирования, а пятая относится к так называемым чиплетам. На территории США осуществляется не более 3 % операций по тестированию и упаковке чипов, основная часть профильных производственных мощностей сконцентрирована в Азии, поэтому власти страны пытаются диверсифицировать соответствующие риски по географическому признаку. Предприятия по тестированию и упаковке чипов на территории США собираются строить Intel, SK hynix, Amkor Technology и Samsung Electronics. В следующем году Apple начнёт использовать 2-нм чипы, созданные TSMC — у них будет передовая упаковка SoIC-X

09.07.2024 [15:04],

Павел Котов

Во второй половине 2025 года Apple намеревается использовать в своей продукции чипы, выполненные по новейшему 2-нм техпроцессу N2 от TSMC, а также использующие разработанную тайваньским подрядчиком передовую технологию упаковки чипов SoIC-X (System on Integrated Chip).

Источник изображения: tsmc.com AMD стала первой из заказчиков TSMC, кто применил в своей продукции упаковку SoIC-X — она используется при производстве ускорителей искусственного интеллекта Instinct MI300 и высокопроизводительных игровых видеокарт. Сейчас это самая сложная технология упаковки чипов в ассортименте TSMC. Она была представлена в 2018 году, а массовое производство стартовало в 2022 году — тогда выход годной продукции быль лишь 50 %. К настоящему времени данный показатель удалось повысить до 90 % — таков он при производстве новой продукции AMD. Интеграция технологии SoIC и существующих InFO/CoWoS позволит объединять однородные или гетерогенные компоненты в один SoC-подобный чип, то позволит уменьшить размеры готового продукта. TSMC намеревается интенсивно развивать технологию SoIC-X, в рамках которой тайваньский полупроводниковый подрядчик к 2027 году сможет обеспечивать соединение пластин при помощи сквозных соединений с шагом 3 мкм — сегодня этот показатель составляет 9 мкм. Intel и японские компании будут совместно совершенствовать технологии упаковки чипов

07.05.2024 [08:28],

Алексей Разин

Японские поставщики контролируют около 30 % мирового рынка оборудования для производства полупроводниковых компонентов и до 50 % рынка сопутствующих расходных материалов, но в сфере тестирования и упаковки чипов 38 % рынка принадлежат китайским предприятиям. Снизить зависимость от Китая призвана новая инициатива Intel, которая подразумевает разработку на территории Японии технологий автоматической упаковки чипов.

Источник изображения: Intel Доминирование Китая на рынке подобных услуг объясняется высокой долей ручного труда на данном этапе изготовления чипов, а он в Китае исторически был дешевле, чем в тех же Японии или США. В новых геополитических условиях необходимость отправлять кристаллы чипов для тестирования и упаковки в Китай начинает тяготить производителей, которые намереваются наладить обработку кремниевых пластин на территории США и Японии, но чтобы не зависеть от специфики местного рынка труда, компаниям нужно развивать автоматизацию в этой сфере, как поясняет Nikkei Asian Review. Изданию стало известно о запуске Intel инициативы на территории Японии, где у компании имеется исследовательский центр, подразумевающей привлечение 14 местных поставщиков оборудования для тестирования и упаковки чипов к повышению уровня автоматизации подобных операций. Власти Японии готовы поддержать данные разработки, выделив десятки, если не сотни миллионов долларов США в виде субсидий. Работоспособные решения планируется получить к 2028 году. К тому времени Япония и США рассчитывают наладить на своей территории выпуск передовых чипов, которые нужно будет тестировать и упаковывать, а потому соответствующие технологии как раз пригодятся. К слову, автоматизация данных процессов в случае с Японией поможет решить и нехватку рабочего персонала, которая за счёт экспансии производства чипов на территории страны только усугубится к тому времени. Компании Samsung Electronics и TSMC тоже располагают исследовательскими центрами в Японии, которые специализируются на технологиях упаковки и тестирования чипов. По мере усложнения компоновки современных вычислительных решений актуальность инвестиций в эту сферу растёт. Сам по себе рынок услуг по тестированию и упаковке чипов по итогам текущего года должен вырасти на 13 % до $12,5 млрд, как считают аналитики TechInsights. Южная Корея одобрила амбициозный нацпроект по развитию передовой упаковки чипов

01.05.2024 [17:50],

Павел Котов

Власти Южной Кореи одобрили инициативу национального уровня, нацеленную на активное содействие развитию передовых технологий упаковки чипов, передаёт местное издание The Elec со ссылкой на анонимные источники. План уже прошёл предварительную экспертизу — её провёл Корейский институт оценки и планирования науки и технологий (KISTEP).

Источник изображения: samsung.com Эксперты изучили национальные проекты с бюджетом более 50 млрд вон ($36,16 млн) при прямой государственной поддержке, превышающей 30 млрд вон ($21,7 млн). Подобные проекты редко проходят экспертизу с первого раза, но технологии упаковки чипов оказались исключением. Большинство рецензентов в KISTEP пришло к консенсусу и признало необходимость программы, чтобы догнать мирового лидера в лице TSMC.

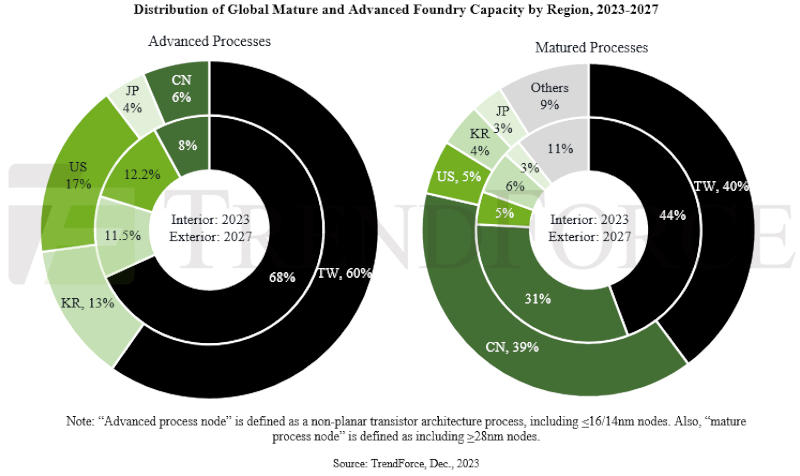

Распределение передовых (слева) и зрелых (справа) полупроводниковых производств по регионам. Источник изображения: trendforce.com К 2027 году доля Южной Кореи в мощностях передовых технологических процессов достигнет 11,5 % с возможностью дальнейшего роста, считают аналитики TrendForce. Бюджет семилетней программы был сокращён с первоначальных 500 млрд вон ($361,59) до 206,8 млрд вон ($149,55). После прохождения технико-экономического обоснования о программе, как ожидается, будет официально объявлено в этом году, а её реализация начнётся в следующем. Сокращение бюджета было ожидаемым, но утверждение инициативы с первого раза указывает на глубокое понимание властями важности упаковки чипов, отмечает источник TheElec. Предприятия по тестированию и упаковке чипов будут расширяться за пределы Тайваня

22.04.2024 [17:50],

Алексей Разин

Призывы к тайваньским компаниям создавать предприятия по выпуску чипов за пределами острова часто звучат от крупных клиентов и целых государств, но растущее значение в наше время обретает и сфера тестирования и упаковки чипов, которая должна развиваться синхронно. Эксперты считают, что экспансия профильных предприятий за пределами Тайваня будет неизбежной.

Источник изображения: ASE Technology Как поясняет DigiTimes, возможности компании TSMC по тестированию и упаковке чипов с использованием передовой технологии CoWoS в текущем году должны удвоиться, но даже с учётом мощностей подрядчиков они не смогут покрыть потребности рынка. Компания ASE Technology обладает необходимым оборудованием и компетенциями, чтобы обеспечивать полный цикл тестирования и упаковки чипов по методу CoWoS 2.5D. Компания Amkor способна содействовать им лишь на определённых этапах технологического процесса, но в нынешней ситуации любая помощь очень важна. При этом для всей отрасли по упаковке чипов прошедший 2023 год характеризовался двузначным спадом показателей, а востребованным методом упаковки CoWoS владеют лишь немногие участники рынка, перечисленные в этом абзаце выше. Помимо высокого спроса на определённый вид услуг, участников рынка толкает к международной экспансии суровая геополитическая реальность, которая заставляет критически оценивать высокую степень концентрации профильных предприятий на Тайване. Поставщики оборудования считают, что основными направлениями экспансии станут Сингапур, Малайзия и Япония. Для тайваньских компаний, которые решатся на такую миграцию, при выборе её направления будет важен целый ряд факторов: поддержка правительства в виде субсидий, наличие квалифицированной рабочей силы, развитость цепочек поставок и логистики, наличие спроса со стороны местных клиентов, а главное — готовность инженерной инфраструктуры к появлению новых предприятий. Стабильность энерго- и водоснабжения будет иметь первостепенную важность в этом вопросе. Генеральный директор TSMC Си-Си Вэй (C.C. Wei) на недавнем отчётном квартальном мероприятии заявил, что занимающаяся упаковкой чипов компания Amkor намеревается построить своё предприятие в Аризоне в непосредственной близости от производственной площадки TSMC. Обеим компаниям предстоит вести работу по приведению своих операций в регионе в соответствие с требованиями местных клиентов. |