|

Опрос

|

реклама

Быстрый переход

TSMC уже получила заказы на выпуск 2-нм чипов от AMD, Apple и более десятка других клиентов

23.09.2025 [04:48],

Алексей Разин

Тайваньская компания TSMC, занимающаяся контрактным производством полупроводниковых компонентов, не очень охотно говорит о специфике своих взаимоотношений с клиентами, но из сторонних источников стало известно, что её услугами по выпуску 2-нм чипов воспользуются почти 15 клиентов.

Источник изображения: AMD Как поясняет Tom’s Hardware со ссылкой на стенограмму со страниц Seeking Alpha, о планах TSMC невольно проболтался президент компании KLA Ахмад Хан (Ahmad Khan) на минувшей конференции Goldman Sachs. Дело в том, что TSMC сама является клиентом этого поставщика оборудования для производства чипов, поэтому она делится с ним своими запросами и потребностями. «Техпроцесс N2 уже набрал около 15 клиентов, разрабатывающих дизайн своих чипов», — пояснил глава KLA. Не менее важно то, что около 10 из них относятся к сегменту высокопроизводительных решений — чипов, которые будут применяться в широком спектре продукции, от серверных систем до игровых консолей, а также ПК. По мнению Хана, 2-нм техпроцесс будет крупнейшим с точки зрения разработки чипов за первые три года своего активного внедрения. Напомним, к выпуску 2-нм чипов в массовых количествах TSMC приступает в этом году. Сами представители TSMC ранее отмечали, что техпроцесс N2 набирает популярность быстрее, чем N3 и N5 на сопоставимых фазах жизненного цикла. Это выразилось в том, что клиенты TSMC подготовили гораздо больше цифровых проектов с 2-нм продуктами в течение двух первых лет его доступности, чем в случае с предыдущими техпроцессами. TSMC исторически опирается на количество разрабатываемых продуктов при описании популярности своих технологий, но не перечисляет клиентов, а тем более — не раскрывает их имён без их ведома. Впрочем, в случае с 2-нм техпроцессом соответствующие признания уже сделали AMD и MediaTek, как минимум. Apple при выпуске своих новейших процессоров A19 сделала ставку на проверенный и при этом достаточно продвинутый N3E, но и она должна оказаться в числе крупных заказчиков 2-нм чипов у TSMC в следующем году. В семействе техпроцессов N2 будет как минимум три разновидности (N2, N2P и N2X), которые будут внедряться поэтапно. В случае с Intel ожидается, что некоторые кристаллы в составе процессоров Nova Lake будут выпускаться компанией TSMC по техпроцессам данного семейства в следующем году. Со временем получать от TSMC свои 2-нм чипы начнут компании Qualcomm и Broadcom. За выпуск 2-нм продукции TSMC будут отвечать как минимум три предприятия на Тайване, позже к ним присоединится и Fab 21 в американском штате Аризона. Rapidus запустит самое быстрое в мире производство 2-нм чипов — от проекта до кристалла всего за две недели

27.08.2025 [17:35],

Геннадий Детинич

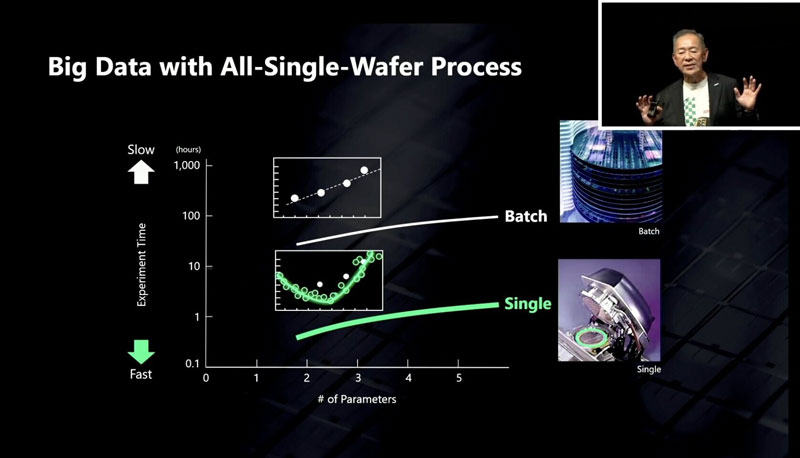

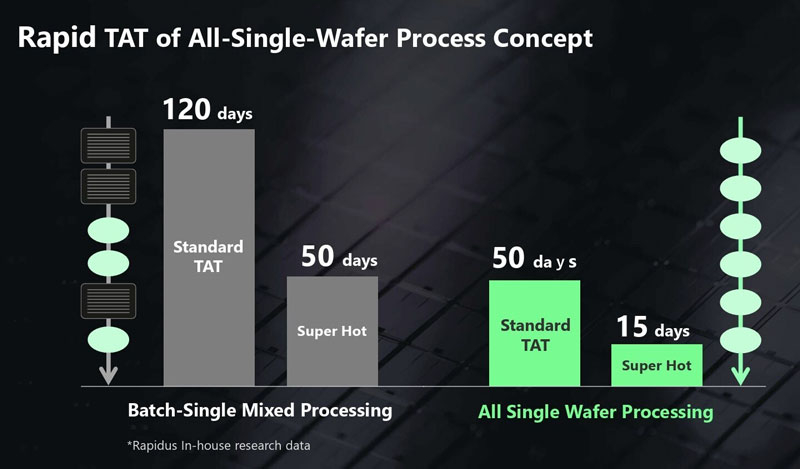

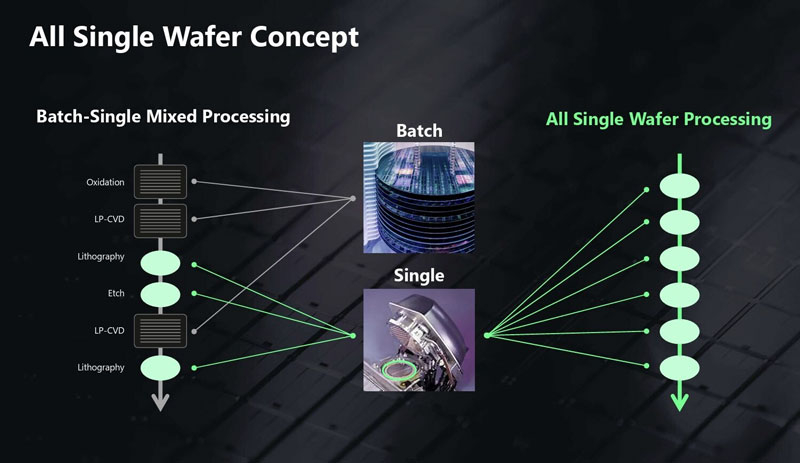

На конференции Hot Chips 2025, которая прошла с 24 по 26 августа в Пало-Альто, глава японской компании Rapidus похвалился успехами по подготовке предприятия к выпуску передовых полупроводников. К июню 2025 года Rapidus смогла запустить свыше 200 единиц оборудования, настроив линии менее чем за год. Через два года компания будет готова к массовому выпуску 2-нм чипов в объёме 25 тыс. 300-мм пластин в месяц и станет самой быстрой при выполнении заказов.

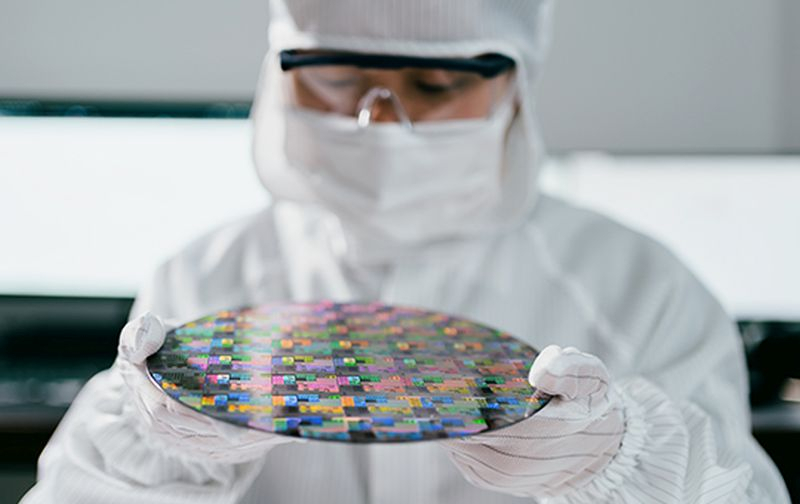

Источник изображений: Rapidus Строительство фабрики IIM-1 компании на Хоккайдо началось в сентябре 2023 года и закончилось примерно год спустя. После этого началась установка и наладка передового оборудования ASML, включая сканеры EUV-диапазона. Согласно ранее обнародованным данным, компания уже в июле начала выпускать экспериментальную продукцию, в частности, первые в Японии 2-нм транзисторы.  На Hot Chips 2025 глава Rapidus уточнил, что транзисторы GAA с круговым затвором в 2-нм исполнении представлены пока только в виде цифрового проекта (Tapes out). Но это не мешает узнать их будущие характеристики, поскольку современные инструменты проектирования предоставляют усреднённые данные по проекту и элементам любой сложности. Из проекта следует, что 2-нм транзисторы GAA «достигли всех требуемых электрических характеристик, которые были заданы с самого начала».  Важным моментом доклада стало заявление об инновационном подходе к обработке пластин с чипами. Вместо пакетной обработки нескольких пластин за один раз будет реализован процесс индивидуальной обработки пластин. Возможно это будет только одним из многих предложений компании для особенно спешащих клиентов. Очевидно, что обработка каждой пластины по отдельности будет стоить дороже, но зато от получения цифрового проекта до изготовления кристаллов пройдёт всего 15 дней. В обычном режиме выпуск кристаллов на линиях компании при индивидуальной обработке пластин потребует 50 дней. Для сравнения, пакетная обработка пластин, например, на мощностях TSMC, обеспечивает выпуск готовой продукции только через 120 дней и через 50 дней, если это нужно сделать максимально быстро. Компания Rapidus считает, что станет самой востребованной на рынке для быстрого получения самой передовой продукции, что поможет ей найти свою нишу на рынке. В истории с кражей 2-нм технологий TSMC подтвердился японский след: Tokyo Electron уволила подозреваемого

07.08.2025 [09:00],

Алексей Разин

На этой неделе стало известно, что тайваньские власти задержали нескольких человек, подозреваемых в неправомерном сборе информации о 2-нм технологии TSMC, которая считается критически важной для национальной безопасности. Наличие в истории японского следа подтвердилось сегодня, поскольку компания Tokyo Electron заявила об увольнении подозреваемого.

Источник изображения: Tokyo Electron Речь идёт о сотруднике тайваньского подразделения Tokyo Electron, который подозревается в неправомерном доступе к важной технологии партнёра. Компания Tokyo Electron является поставщиком литографического оборудования, поэтому её сотрудники на Тайване могли иметь формальные основания для взаимодействия с TSMC по данным вопросам. Поставщик оборудования лишь подтвердил своё сотрудничество со следствием, но отказался комментировать, какого рода информация могла быть похищена и в чьих интересах использована. Tokyo Electron ограничилась заявлением о том, что никакой конфиденциальной информации похищено не было. Компания считает соблюдение законов и этических норм одним из высших приоритетов в своей деятельности, а потому готова активно сотрудничать со следствием. Издание Nikkei Asian Review добавило, что подозреваемый теперь уже бывший сотрудник тайваньского представительства Tokyo Electron ранее успел поработать в TSMC. Представители правоохранительных органов острова посетили местное подразделение японской компании на прошлой неделе. С подачи сайта Tom's Hardware, который ссылается на тайваньские СМИ, стало известно о вероятной связи подозреваемого бывшего сотрудника Tokyo Electron с японской компанией Rapidus, которая рассчитывает к 2027 году наладить на своих мощностях выпуск 2-нм чипов на контрактной основе. Подозреваемый якобы передал Rapidus серию фотоснимков, имеющих отношение к технологическим процессам производства чипов по данным литографическим нормам. В этом ему, как предполагает следствие, содействовал сотрудник TSMC. TSMC уволила нескольких сотрудников, получивших неправомерный доступ к 2-нм технологии производства чипов

05.08.2025 [08:30],

Алексей Разин

В «гонке литографических технологий» ставки очень высоки, поскольку освоение современных методов производства передовых чипов требует колоссальных инвестиций и обеспечивает конкурентное преимущество не только для отдельных компаний, но и целых стран. Тайваньская TSMC в этом смысле старается оберегать свои секреты, и недавно её пришлось уволить нескольких сотрудников, получивших неправомерный доступ к 2-нм технологии.

Источник изображения: ASML Как сообщает Nikkei Asian Review, пока сложно судить, с какой целью сотрудники стремились получить данную информацию, в каком объёме им удалось это сделать, и был ли в итоге нанесён ущерб TSMC. Известно лишь, что несколько теперь уже бывших сотрудников компании получили доступ к данной информации, хотя это не предполагалось их должностными обязанностями. Утекли ли эти данные за пределы TSMC, должно показать следствие. Обвиняемые могут понести уголовную ответственность, особенно если суд докажет, что их действия причинили вред национальной безопасности Тайваня. Представители TSMC подтвердили, что компания ведёт расследование в отношении неопределённого количества сотрудников, нарушивших правила доступа к чувствительной служебной информации, но отказалась от дополнительных комментариев до конца следствия. Правоохранительные органы Тайваня тоже воздержались от предоставления дополнительной информации. С 2022 года на острове действуют более строгие нормы законодательства, предусматривающие серьёзную ответственность за неправомерное распространение информации, имеющей важное значение для национальной безопасности Тайваня. Особое внимание уделяется защите технологических секретов в полупроводниковой отрасли, поскольку она имеет важнейшее значение для экономики острова. Все технологии «тоньше» 14 нм оберегаются этим законодательством. Сейчас 2-нм технология считается самой продвинутой из тех, что будут освоены в массовом производстве до конца текущего года. Во всём мире только четыре компании выразили готовность начать выпуск чипов по 2-нм технологии: это собственно TSMC, южнокорейская Samsung Electronics, японская Rapidus и американская Intel. В последнем случае, как стало известно недавно, существует некоторая неопределённость в отношении дальнейшего курса компании, но техпроцесс 18A она готова использовать долго и плодотворно. Представители TSMC добавили в комментариях Nikkei, что компания категорически не приемлет попытки нарушить защиту своих торговых секретов, а потому подобные действия преследуются самым строжайшим образом в соответствии с буквой закона. При этом компания выражает заинтересованность в сохранении стабильности своей деятельности и укреплении мер безопасности. Первым 2-нм чипом Samsung станет мобильный процессор Exynos 2600

02.08.2025 [05:34],

Алексей Разин

В отличие от американских акционерных компаний, южнокорейская Samsung Electronics содержание своих квартальных отчётных конференций раскрывает не так широко, но представителю IDC удалось обнаружить откровения руководства Samsung по поводу принадлежности мобильного процессора Exynos 2600 к первой волне 2-нм чипов.

Источник изображения: Samsung Electronics Как отмечает аналитик Брайан Ма (Bryan Ma) на страницах социальной сети X, во время сессии вопросов и ответов представители Samsung сделали важное признание: «Exynos 2600 будет первым флагманским чипсетом, изготовленным по 2-нм технологии с применением GAA (пространственной структуры транзисторов с окружающим затвором — прим. автора), этот чип обеспечивает существенное улучшение в работе нейронного сопроцессора по сравнению с предыдущей версией, предлагая более развитую поддержку ИИ-функциональности на стороне конечного устройства». Если учесть, что и долгосрочный контракт с Tesla до 2033 года подразумевает выпуск 2-нм чипов AI6 для бортовых систем автопилота, то в совокупности можно говорить как минимум о двух изделиях, которые Samsung будет производить с применением этой передовой технологии. Правда, если чипы для Tesla должны будут выпускаться с 2026 года на строящемся новом предприятии в Техасе, то производство 2-нм процессора Exynos 2600 компания будет вынуждена освоить ранее этого срока на своих южнокорейских предприятиях. Семейство смартфонов Galaxy S26, в случае своего дебюта в начале 2026 года, должно будет примерить эти самые 2-нм чипы. О самом процессоре Exynos 2600 на данный момент известно не так много. Ему приписывается сложная 10-ядерная компоновка по схеме «1 + 3 + 6». Первое наиболее крупное ядро будет отвечать за самые ресурсоёмкие вычисления, ему будут помогать три более компактных, а оставшиеся шесть будут использоваться при необходимости обеспечить энергоэффективную работу. Графическая подсистема Xclipse 960 должна на 15 % превзойти по быстродействию Adreno 830 компании Qualcomm. Кроме того, Samsung открыто обещает прирост эффективности Exynos 2600 в задачах ИИ по сравнению с предшественником. Выход этого 2-нм процессора, по всей видимости, будет символизировать для Samsung возвращение чипов собственного производства в смартфоны флагманской линейки Galaxy S. Японская Rapidus заручилась поддержкой Siemens в сфере выпуска 2-нм чипов

05.07.2025 [07:39],

Алексей Разин

Основанная в августе 2022 года японская компания Rapidus ставит перед собой амбициозные задачи к 2027 году освоить на территории страны массовый выпуск 2-нм чипов для сторонних заказчиков. Для достижения цели ей приходится обращаться к разным партнёрам, поставщик ПО для разработки чипов Siemens стала одним из них.

Источник изображения: Siemens Самым известным партнёром Rapidus по освоению 2-нм технологии «с нуля» является американская корпорация IBM, которая первой в мире изготовила прототипы ячеек памяти на своей опытной линии в штате Нью-Йорк, используя 2-нм техпроцесс. Между тем, по мере приближения к моменту начала серийного выпуска 2-нм продукции Rapidus обрастает новыми партнёрами. Одним из них стала Siemens — крупный поставщик программного обеспечения для проектирования интегральных микросхем. Сама Rapidus разработкой чипов заниматься не будет, но профильное программное обеспечение потребуется ей для адаптации разработок клиентов к специфике своих производственных процессов. Rapidus получит доступ к платформе Calibre компании Siemens. Представители японского контрактного производителя в очередной раз заявили, что намерены существенно опередить конкурентов по сокращении времени, требуемого для постановки на конвейер вновь разработанных чипов. Профильное ПО компании Siemens будет использоваться Rapidus на всех этапах подготовки и непосредственно при производстве полупроводниковых компонентов. О конкретных клиентах Rapidus пока известно не так много, но стартап Tenstorrent может оказаться в их числе. Кроме того, японский производитель ведёт переговоры с LG и BOS Semiconductor — последняя поставляет чипы с высокой степенью интеграции в автомобильном сегменте. Сама IBM надеется со временем воспользоваться услугами Rapidus для производства своих процессоров, поскольку после «предательства» GlobalFoundries она вынуждена полагаться на Samsung. Samsung начнёт выпускать 2-нм чипы до конца года — это последний шанс вернуть доверие Nvidia и Qualcomm и спасти полупроводниковый бизнес

17.06.2025 [10:35],

Сергей Сурабекянц

Samsung возлагает большие надежды на 2-нанометровый производственный процесс. Оба предприятия компании должны освоить массовое производство по этому техпроцессу до конца года. В случае успеха Samsung рассчитывает перехватить часть заказов у TSMC и переломить негативное развитие событий для своего полупроводникового подразделения. Источник изображения: Samsung Предыдущий опыт Samsung с транзисторами GAA (Gate-all-Around) должен помочь ей быстрее отладить 2-нанометровый техпроцесс. В 2024 году Samsung стала первой компанией в мире, которая смогла массово применять технологию GAA-транзисторов для производства чипов. Samsung приступила к исследованию технологии GAA ещё в начале 2000-х годов и впервые внедрила её для своего 3-нм техпроцесса в 2022 году. Однако из-за мировой экономической нестабильности, высокой стоимости производства, а также ограниченной клиентской базы в таких секторах, как мобильные устройства, спрос на 3-нм техпроцесс Samsung оказался несущественным. Как результат, лидерство в производстве 3-нм чипов перешло к тайваньскому контрактному производителю чипов TSMC, который использует более традиционные (и дешёвые) методы производства транзисторов. Теперь Samsung вынуждена сделать ставку на 2-нанометровый техпроцесс после того, как 3-нанометровая технология не получила должной популярности у заказчиков. Компания на протяжении последнего времени пытается получить достаточно значимые заказы от крупных разработчиков микросхем на фоне практически абсолютного доминирования TSMC. На данный момент Samsung, в дополнение к производству собственного чипа Exynos 2600, удалось заключить договор на производство 2-нм чипов для японской компании Preferred Networks. TSMC, в свою очередь, планирует начать массовое производство по 2-нанометровому техпроцессу на своих заводах в Баошане и Гаосюне на Тайване в конце этого года. Предприятия TSMC станут первыми фабриками, на которых будет применена технология GAA к узлу 2-нм. Похоже, что Samsung не удалось сохранить лидерство в этой сфере. Судя по многочисленным сообщениям, выход годных чипов по 2-нанометровой технологии TSMC уже достиг 70 %, что ставит её в очень выгодное положение для начала массового производства. Неудивительно, что такие крупные компании, как Apple, Nvidia, Qualcomm и AMD, рассматривают TSMC в качестве основного поставщика чипов. Ближайшие полгода покажут, сможет ли Samsung возродить доверие к своему полупроводниковому производству для возвращения таких заказчиков, как Nvidia и Qualcomm. С каждым нанометром — дороже: себестоимость 2-нм пластин вырастет на 50 % по сравнению с 3-нм

02.06.2025 [11:39],

Алексей Разин

Переход на более «тонкие» техпроцессы сам по себе уже не способен снижать себестоимость полупроводниковой продукции прежними темпами. TSMC в следующем полугодии приступит к массовому производству 2-нм чипов, и одна кремниевая пластина с ними будет обходиться в $30 000. Дальнейшая миграция на новую литографию поднимет стоимость пластины до $45 000.

Источник изображения: ASML Для сравнения, себестоимость одной 300-мм пластины с 3-нм чипами TSMC составляет примерно $20 000. А более старые 5-нм чипы обходились примерно в $16 000 за пластину. То есть можно заметить, что рост стоимости ускорился при переходе от одного поколения техпроцессов к другому. Прогноза касательно себестоимости в $30 000 за 2-нм пластину придерживается тайваньский ресурс Commercial Times. Разработка 2-нм чипа в среднем будет обходиться клиентам TSMC в $725 млн. Но даже рост сопутствующих затрат не заставит компании отказаться от перехода на 2-нм техпроцесс. Ещё в апреле AMD заявила, что компоненты серверных процессоров EPYC семейства Venice будут выпускаться TSMC по 2-нм технологии. В декабре, как ожидается, MediaTek представит свои 2-нм процессоры семейства Dimensity 9600. Apple и Qualcomm в следующем году должны представить свои флагманские чипы (A20/M6 и Snapdragon 8 Elite Gen 3 соответственно), которые также будут выпускаться по 2-нм технологии. Облачные гиганты последуют их примеру, к 2027 году предложив свои 2-нм процессоры: Google представит новый Trillium v8, AWS (Amazon) — Trainium 4, а Microsoft ещё во второй половине 2026 года — свои процессоры Maia 300. Облачным провайдерам важно выпускать современные процессоры собственной разработки, чтобы снизить зависимость от AMD и Nvidia, а также оптимизировать затраты. В текущем году лидером по приросту поставок собственных процессоров станет AWS. Китайцы выпустили первую видеокарту на суверенном 6-нм GPU — Lisuan G100, которую сравнивают с RTX 4060

30.05.2025 [16:29],

Николай Хижняк

Китайская компания Lisuan Technology заявила, что успешно запустила первый образец будущей видеокарты G100, в основе которой используется первый для Китая полностью суверенный графический процессор, произведённый с использованием 6-нм техпроцесса.

Источник изображения: Lisuan Technology Китай стремится к технологической независимости от западных компаний. На этом фоне к китайским компаниям присоединилось множество опытных разработчиков и инженеров. Lisuan Technology, основанная в 2021 году, является одним из самых молодых стартапов в сегменте разработки и производства видеокарт. Другими аналогичными стартапами являются Moore Threads (основана в 2020 году) и Biren (создана в 2019 году). В числе основателей Lisuan Technology — ветераны индустрии, проработавшие в Кремниевой долине более 25 лет. То же самое можно сказать и о Moore Threads, которая была основана Чжан Цзяньчжуном (Zhang Jianzhong), бывшим вице-президентом и директором китайского подразделения Nvidia. О видеокарте G100 пока мало информации. Известно, что в её основе используется проприетарная архитектура TrueGPU, разработанная Lisuan Technology. В отличие от некоторых других китайских производителей, которые нередко лицензируют технологии таких компаний, как Imagination, для разработки на их основе собственных продуктов, TrueGPU является действительно суверенной архитектурой, разработанной с нуля. Lisuan Technology не сообщает, на мощностях какого производителя выпущен 6-нм графический процессор, используемый в основе G100. Из-за американских санкций Китай не имеет доступа к иностранным 6-нм техпроцессам, что исключает Samsung и TSMC в качестве возможных производителей этого чипа. Весьма вероятно, что за выпуск GPU отвечает китайский производитель полупроводников SMIC, который также занимается выпуском графических процессоров Ascend 920 AI для компании Huawei. Слухи приписывают G100 производительность на уровне GeForce RTX 4060, хотя сама компания Lisuan Technology эту информацию не подтверждала. Также ускорителю приписывают поддержку графических API DirectX 12, Vulkan 1.3, OpenGL 4.6 и OpenGL 3.0. Это может говорить о том, что G100 можно будет использовать не только для профессиональных задач, но и для игр. Разработка G100 началась в 2021 году. Изначально компания планировала выпустить этот ускоритель в 2023 году, однако финансовые трудности (дело чуть не дошло до банкротства), с которыми столкнулся разработчик, сдвинули срок выпуска на 2024 год. В конечном итоге родительская компания Dongxin Semiconductor поддержала стартап и выделила ему финансирование в размере $27,7 млн, что позволило продолжить разработку G100. Lisuan Technology успешно произвела первые чипы G100, они работают и, судя по всему, результаты соответствуют ожиданиям разработчика. Сейчас компания занимается разработкой программного обеспечения, проверками аппаратной части, а также оптимизацией графического драйвера. Lisuan Technology рассчитывает выпустить небольшое количество видеокарт G100 в третьем квартале этого года, однако массовое производство ускорителя, вероятно, стартует не раньше 2026 года. Разработка видеокарты с нуля требует больших усилий и времени. Опыт той же Moore Threads показал, что разработка программного обеспечения так же важна, как и разработка «железа», поскольку правильно оптимизированные драйверы способны значительно повысить производительность GPU. По пятам Apple: 2-нм чипы MediaTek будут готовы к производству уже к сентябрю

21.05.2025 [13:32],

Алексей Разин

Для компании MediaTek выставку Computex можно считать домашним мероприятием, поскольку она проходит на Тайване, и имя этого разработчика Arm-совместимых процессоров уже упоминалось в контексте сотрудничества с Nvidia. Как выясняется, MediaTek уже к сентябрю будет располагать цифровыми проектами первых 2-нм чипов, желая не отставать от Apple и Qualcomm.

Источник изображения: MediaTek Разумеется, подобный прогресс будет возможен благодаря сотрудничеству с TSMC, поэтому MediaTek нужно лишь своевременно завершить разработку своих первых 2-нм процессоров. По словам генерального директора Рика Цая (Rick Tsai), компания будет использовать 2-нм техпроцесс при изготовлении массовых изделий. «Мы совершенно точно будем двигаться по этому пути в долгосрочной перспективе. Два нанометра, A14, A16, всё, что будет после этого — MediaTek будет вовлечена», — пояснил глава компании на Computex 2025. Сама TSMC должна начать выпуск 2-нм чипов для клиентов во второй половине текущего года, поэтому MediaTek окажется в числе первых в очереди на использование данной технологии. Для хромбуков Google компания намерена поставлять специальные процессоры, выпускаемые по 3-нм технологии компанией TSMC. Есть у MediaTek и намерение представить собственный чип для серверных систем искусственного интеллекта. Первый опыт в этой сфере компания получит благодаря сотрудничеству с Nvidia в сфере разработки процессоров GB10 для вычислительных систем DGX Spark. По слухам, партнёры также стремятся создать N1X — совместно разработанный процессор для ноутбуков. Кроме того, MediaTek готова предложить свои процессорные ядра для использования совместно с графической подсистемой GeForce RTX в автомобильном сегменте. Предполагается, что соответствующий чип будет выпущен довольно скоро. Сотрудничество с Nvidia в рамках использования интерфейса NVLink Fusion, который был представлен на днях, наверняка материализуется в серийных изделиях MediaTek не ранее 2027 года, как считают отдельные источники. TSMC уже вовсю выпускает чипы по улучшенному 3-нм техпроцессу N3P — на очереди N3X

24.04.2025 [06:43],

Дмитрий Федоров

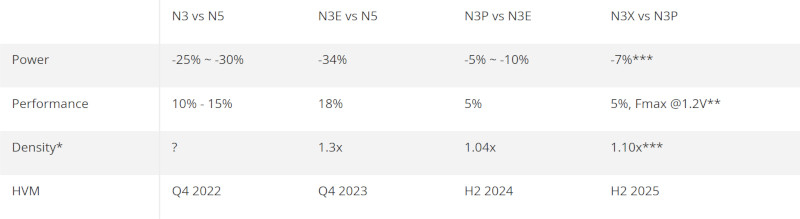

В апреле 2025 года на технологическом симпозиуме в Северной Америке компания TSMC объявила, что начала серийное производство чипов по техпроцессу N3P ещё в IV квартале 2024 года. Эта 3-нм платформа третьего поколения сохраняет полную совместимость с дизайнами чипов для прежней версии 3-нм техпроцесса и ориентирована на задачи, где критичны высокая производительность и экономичное энергопотребление — от пользовательских устройств до центров обработки данных.

Источник изображения: TSMC Технология N3P представляет собой оптическое сжатие предыдущего техпроцесса N3E. Сохраняя прежние правила проектирования и совместимость с блоками чипов, она обеспечивает прирост производительности до 5 % при неизменном уровне утечки токов либо снижение энергопотребления на 5–10 % при тех же частотах. Кроме того, в схемах со стандартной пропорцией логических, SRAM и аналоговых элементов (50 %, 30 % и 20 % соответственно), N3P даёт прирост плотности транзисторов на 4 %. Повышение плотности интеграции в N3P достигнуто за счёт улучшения оптических параметров литографического процесса, а не изменений в проектных нормах, что способствует более эффективному масштабированию всех функциональных структур микросхемы. Это преимущество особенно проявляется в проектах с преобладанием памяти SRAM, где критична высокая плотность интеграции. В настоящее время техпроцесс применяется для выполнения производственных заказов ключевых клиентов компании. TSMC уточняет, что развитие 3-нм линейки техпроцессов не ограничивается узлом N3P. Следующим этапом станет 3-нм техпроцесс N3X, массовое производство которого запланировано на II полугодие 2025 года. Эта версия ориентирована на достижение максимальных тактовых частот и, согласно внутренним оценкам компании, обеспечивает увеличение максимальной производительности на 5 % при фиксированном энергопотреблении либо позволяет снизить энергопотребление на 7 % при неизменной частоте по сравнению с N3P.

* Плотность чипа, опубликованная TSMC, отражает «смешанную» структуру чипа, состоящую из 50 % логических элементов, 30 % памяти SRAM и 20 % аналоговых блоков. ** При одинаковой площади. *** При одинаковой тактовой частоте. Источник изображения: Tom's Hardware Ключевое отличие техпроцесса N3X — поддержка напряжения питания до 1,2 вольт, что является аномально высоким значением для 3-нм технологического узла. Это позволяет микросхемам достигать максимальной тактовой частоты (Fmax), что особенно важно для процессоров клиентского сегмента. Однако такая возможность сопряжена с серьёзными технологическими ограничениями: мощность, обусловленная токами утечки, может возрасти до 250 %. Поэтому при проектировании микросхем на базе N3X требуется инженерный компромисс между производительностью и тепловыми параметрами устройства. Старший вице-президент по развитию бизнеса и глобальным продажам, а также заместитель операционного директора TSMC Кевин Чжан (Kevin Zhang) отметил, что компания продолжает оптимизировать свои техпроцессы даже после их перехода к массовому производству. По его словам, переход на новый технологический узел требует от клиентов значительных инвестиций, включая разработку чипов в рамках экосистемы. Поэтому стратегия TSMC направлена на непрерывную оптимизацию уже внедрённых техпроцессов, чтобы клиенты могли дольше сохранять эффективность ранее сделанных вложений. TSMC традиционно выпускает несколько итераций одного технологического узла в рамках единого комплекта разработки — Process Development Kit (PDK). Примером служат серии техпроцессов N5 и N4, включающие, соответственно, N5P и версии N4P и N4C. Такой подход позволяет компании максимально эффективно использовать дорогостоящее технологическое оборудование, а клиентам — снижать затраты за счёт повторного использования IP-блоков. Узлы N3P и N3X органично продолжают эту стратегию в рамках 3-нм семейства техпроцессов. Несмотря на активное внимание к перспективным 2-нм техпроцессам, основанным на транзисторах с полным затвором (GAA), основная масса процессоров для клиентских устройств, которые выйдут на рынок в ближайшие кварталы, будет производиться с использованием техпроцессов семейства N3. К числу таких решений относятся смартфоны, планшеты и компьютеры новых поколений, запуск которых ожидается в 2025 году и позднее. Индия станет производителем полупроводников в этом году — её первые чипы будут 28-нм

24.01.2025 [19:37],

Сергей Сурабекянц

Индийский рынок полупроводников готов к быстрому росту — по прогнозам, его ёмкость достигнет $63 млрд к 2026 году. Индия готовится совершить резкий скачок на мировой технологической арене, а первые чипы индийского производства дебютируют уже в этом году. Хотя они будут выпускаться по далеко не самому современному 28-нм техпроцессу, это будет значительный шаг вперёд, ведь такие чипы широко используются в автомобилестроении, бытовой электронике и интернете вещей.

Источник изображения: Micron Первые чипы с маркировкой «Сделано в Индии» изначально планировалось выпустить в декабре 2024 года, но затем срок начала производства был передвинут на август–сентябрь 2025 года. На полную мощность завод по производству полупроводников выйдет в 2026 году при поддержке тайваньской компании Powerchip и индийской промышленной группы Tata. Первые индийские чипы будет выпускаться по 28-нанометровому техпроцессу. Конечно, этот техпроцесс крайне далёк от передовых 2-нм техпроцессов ведущих мировых производителей чипов. Тем не менее, 28-нм чипы широко используются и весьма востребованы в различных отраслях, включая автомобилестроение, бытовую и промышленную электронику и не только. «Наш первый чип будет выпущен в этом году, и теперь мы смотрим на следующий этап, когда мы сможем получить производителей оборудования, производителей материалов и проектировщиков в Индии. Что касается материалов, то от чистоты в частях на миллион нам нужно перейти к уровням чистоты в частях на миллиард. Это требует огромных преобразующих изменений в процессе, и отрасль работает над достижением этого», — заявил на Всемирном экономическом форуме в Давосе министр железных дорог, связи, электроники и информационных технологий Ашвини Вайшнау (Ashwini Vaishnaw). Индия активно работает над развитием своей полупроводниковой промышленности, что обусловлено растущим мировым спросом на чипы и стремлением правительства позиционировать страну как надёжную альтернативу китайским и тайваньским производителям. В частности, в составе Digital India Corporation запущено независимое бизнес-подразделение India Semiconductor Mission. Обладая административной и финансовой автономией, компания будет реализовывать долгосрочные стратегии производства полупроводников и дисплеев, а также содействовать созданию экосистемы проектирования чипов. Индия планирует привлечь значительные иностранные инвестиции. NXP Semiconductors собирается инвестировать в НИОКР полупроводников более $1 млрд. Analog Devices совместно с Tata Group изучает возможности производства чипов. Micron Technology строит в Индии сборочный и испытательный завод стоимостью $2,75 млрд. «Последний рубеж транзисторной архитектуры»: TSMC и Intel рассказали о нанолистовых транзисторах

13.12.2024 [13:02],

Геннадий Детинич

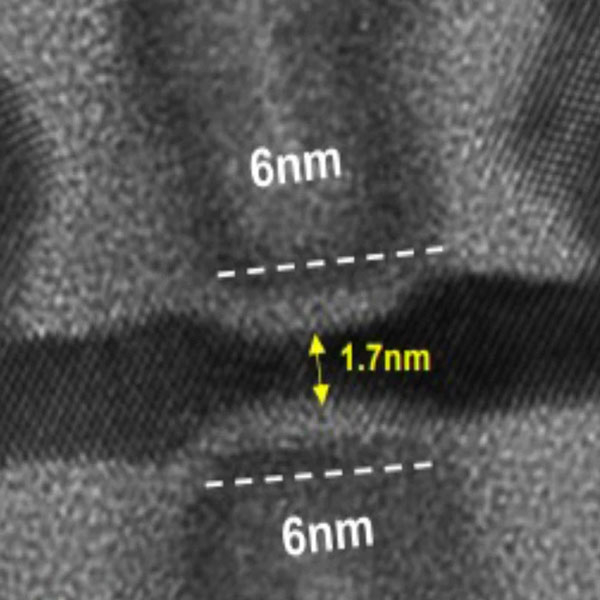

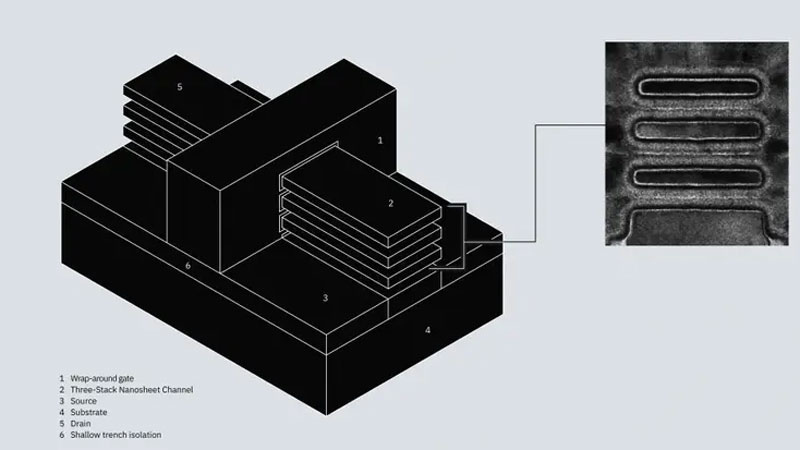

На днях на конференции IEDM 2024 в Сан-Франциско компания TSMC впервые официально рассказала о преимуществах перехода на 2-нм транзисторы с круговым затвором Gate-All-Around и нанолистовыми каналами. К выпуску чипов по технологии N2 тайваньский чипмейкер приступит в наступающем году. По сути, нанолисты — это финальная архитектура транзисторов в привычном понимании и она останется актуальной надолго.

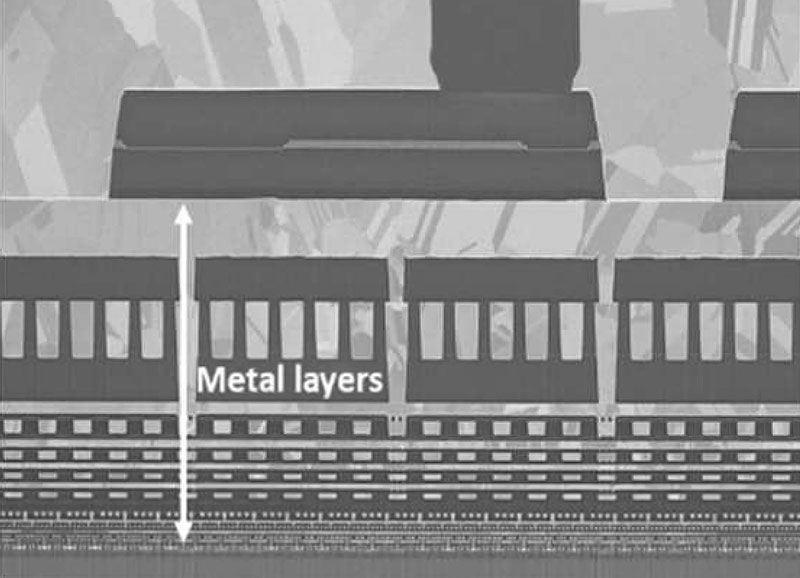

Не видите внизу 2-нм транзисторы? А они есть! Источник изображения: TSMC В 2025 году производить чипы на основе 2-нм техпроцесса с наностраничными каналами и круговым затвором начнут также Samsung и Intel. Подобные структуры первой начала выпускать компания Samsung в рамках 3-нм техпроцесса в 2022 году. Для TSMC это станет первым опытом и плодом «более чем четырёхлетнего труда», как признался глава отдела разработчиков компании. Современные транзисторы FinFET представляют собой набор вертикально расположенных транзисторных каналов — рёбер или плавников. Характеристики такого транзистора зависят от количества рёбер у каждого — одного, двух или трёх. Чем больше каналов, тем больше площадь, занимаемая транзистором. Это особенно остро сказывается в случае массивов памяти SRAM. Каждая ячейка такой памяти состоит из шести транзисторов и поэтому плохо поддаётся масштабированию. Между тем, без SRAM не обходятся ни простенькие контроллеры, ни мощные процессоры и ускорители. Перевод транзисторных каналов в горизонтальную плоскость в виде тонких наностраниц сразу улучшает плотность, так как каналы располагаются друг над другом, и неважно, сколько их. От этого занимаемое транзистором место не увеличивается. В частности, переход TSMC от выпуска 3-нм FinFET транзисторов к 2-нм наностраничным увеличивает плотность размещения транзисторов на 15 %, независимо от того, используются ли производительные схемы или энергоэффективные. Выигрыш произойдёт в обоих случаях. Между производительностью и энергоэффективностью придётся выбирать. Если делать ставку на скорость вычислений, прирост от перехода на 2-нм наностраничные транзисторы составит 15 %, а если выбрать низкое потребление, то выигрыш достигнет впечатляющих 30 %. Но это не вся польза от наностраничных каналов. Для FinFET транзисторов нельзя создать транзисторы с 1,5 рёбрами — это как полтора землекопа из известной сказки. Зато в случае наностраничных каналов можно менять их ширину, не говоря о количестве, и проектировать схемы с разнообразными и точно требуемыми параметрами. В компании TSMC технологию изменения ширины наностраниц назвали Nanoflex. Это позволит выпускать на одном кристалле логику с узкими наностраницами, что ограничит их потребление, и вычислительное ядро с транзисторами с широкими наностраницами для пропускания больших токов, что обеспечит производительность, несмотря ни на что. Но особенно заметно от перехода на наностраничные транзисторные каналы выиграет SRAM. При переходе с 4-нм на 3-нм техпроцесс плотность ячеек памяти SRAM выросла всего на 6 %. В случае технологии Nanoflex при переходе от 3-нм на 2-нм техпроцесс плотность ячеек SRAM вырастет на 11 %. Это даст повсеместный выигрыш, утверждают в TSMC.

Источник изображения: Intel Интересно добавить, что на этой же конференции прозвучал доклад компании Intel, которая очертила границы будущего для классических транзисторов и, конкретно, в наностраничном исполнении. «Архитектура наностраниц на самом деле является последним рубежом транзисторной архитектуры, — сказал Ашиш Агравал (Ashish Agrawal), специалист по кремниевым технологиям в исследовательской группе Intel по компонентам схем. — Даже будущие комплементарные FET (CFET) устройства, которые, возможно, появятся в середине 2030-х годов, будут построены из нанолистов. Поэтому важно, чтобы исследователи понимали свои ограничения». Чтобы изучить границы возможного, в Intel создали экспериментальную транзисторную структуру с каналом длиной 6 нм. Чем короче канал, тем выше вероятность утечек через него и тем менее управляемым становится транзистор. Эксперимент показал, что транзисторы с каналами длиной 6 нм и шириной наностраницы 2 нм полностью работоспособны. Это позволит наностраничной транзисторной архитектуре существовать ещё долго, отодвинув переход на двумерные материалы и транзисторы на принципиально иной архитектуре далеко в будущее. Возвращаясь к 2-нм техпроцессу TSMC (а также Samsung и Intel), напомним, что цифра в его названии ничего не говорит о физических размерах транзисторов. В рамках 2-нм техпроцесса транзисторы и транзисторные каналы измеряются десятками нанометров. Поэтому до выставленных Intel границ в эксперименте индустрия будет идти не одну пятилетку. IBM и Rapidus придумали, как сделать 2-нм чипы производительными или энергоэффективными

10.12.2024 [15:07],

Геннадий Детинич

Компании IBM и Rapidus для конференции IEDM 2024 подготовили доклад, в котором сообщили о продвижении к массовому производству 2-нм чипов. Партнёры разработали метод выпуска как высокопроизводительных, так и малопотребляющих модификаций 2-нм чипов. Оба техпроцесса полностью управляемы и до конца десятилетия будут реализованы на практике в Японии на заводе компании Rapidus.

Источник изображения: IBM Компания IBM начала разрабатывать транзисторы с круговым затвором (GAA, Gate-All-Around) на основе стопки транзисторных каналов из наностраниц более 10 лет назад совместно с компанией Samsung. Затем их пути разошлись. Компания Samsung начала самостоятельно развивать идею GAA-транзисторов, а компания IBM два года назад взяла в партнёры японскую компанию Rapidus, которую создали в качестве японского ответа TSMC. Партнёры стремятся к тому, что с 2027 года Rapidus станет центром мирового контрактного производства полупроводников. Такое вполне возможно, если с TSMC вдруг случится что-то непоправимое, а в Тихоокеанском регионе в ближайшие пять лет может произойти много изменений. При переходе на выпуск 2-нм транзисторов все производители, включая IBM и Rapidus, отказались от «плавниковых» транзисторов FinFET. Каналы транзисторов вернули из вертикального положения в горизонтальное и представили их в виде нескольких уровней нанопроводов или наностраниц, расположенных друг над другом в рамках одного транзистора. Каналы получились в виде наноструктур, полностью окружённых затворами. Это позволило сохранить рабочие токи, хотя сами транзисторы стали ещё мельче. Перед компаниями стояла задача массового производства маленьких транзисторов, так, чтобы отдельные компоненты не загрязнялись материалами, предназначенными для других. Компании IBM и Rapidus во многом справились с этой проблемой, а также показали возможность выпускать GAA-транзисторы с несколькими пороговыми напряжениями в каналах: с высокими для малопотребляющей электроники и с низкими для высокопроизводительной. На конференции IEDM 2024 IBM и Rapidus представили технологию выборочного уменьшения слоя (selective layer reductions) — пространства между полупроводниковыми каналами n-типа и p-типа. В зависимости от толщины этого пространства пороговое напряжение будет изменяться от большего к меньшему. Толщина задаётся на этапе производства транзисторов и определяет, каким будет чип — производительным или энергоэффективным. Партнёры представили два варианта техпроцесса: SLR1 и SLR2. Техпроцесс SLR1 обеспечивает высокое значение порогового напряжения, а SLR2 — низкое. Также компании IBM и Rapidus смогли значительно снизить загрязнение изолирующей подложки под транзисторами ионами в процессе плазменной обработки чипов в процессе производства — травления. Кадзуюки Томида (Kazuyuki Tomida), генеральный менеджер Rapidus US, также отметил: «Технология Multi-Vt [мультипороговых напряжений] является важнейшим компонентом нашей архитектуры наностраниц. Совместная публикация этого исследовательского документа с IBM Research на конференции IEDM представляет собой важную веху для Rapidus. Это достижение укрепляет нашу уверенность в реализации нашей цели — производстве на Хоккайдо на нашем передовом полупроводниковом заводе IIM». В Зеленограде начнут выпускать чипы для SIM-карт и паспортов — на этом планируется заработать триллионы рублей

22.11.2024 [13:45],

Павел Котов

В следующем году предприятие «НМ-Тех» из Зеленограда начнёт запускать проекты, посвящённые производству чипов для SIM-карт, токенов электронных подписей, загранпаспортов, банковских и транспортных карт. До 2030 года компания рассчитывает на совокупную прибыль от реализации этой продукции выше 3 трлн рублей — опрошенные «Коммерсантом» эксперты считают эту цель достижимой.

Источник изображения: JERO SenneGs / unsplash.com На сайте подмосковного завода «НМ-Тех» появилось описание четырёх новых проектов. Это производство микросхем для UHF-меток, которые используются в транспортных и других картах — научно-исследовательские и опытно-конструкторские работы (НИОКР) по нему стартуют в 2025 году, реализация стартует в 2027 году; ожидаемые продажи — 4,8 млрд руб. Защищённые микросхемы для SIM-карт и M2M-чипов для устройств интернета вещей: НИОКР в 2026 году, реализация в 2028 году, продажи — 7,3 млрд руб. Проект по производству U-чип-микросхем, которые используются в загранпаспортах: НИОКР в 2027 году, реализация в 2029 году, продажи — 3,9 млрд руб. Серийное производство чипов для USB-токенов с поддержкой электронной подписи: НИОКР в 2028 году, реализация в 2030 году, объём реализации — почти 3 трлн руб. ООО «НМ-Тех» было зарегистрировано в мае 2019 года; доступ к сведениям о его владельцах и руководителях в ЕГРЮЛ закрыт. В 2022 году организация заключила соглашение с ГК «Элемент» на отладку производства чипов для паспортов и банковских карт на предприятии «Ангстрем-Т» (принадлежит «НМ-Тех»). По итогам 2023 года компания получила 231 млн руб. дохода при чистом убытке 3,3 млрд руб. В начале августа компания зарегистрировала два патента на топологию микросхем для SIM-карт и UHF-меток; уставный капитал летом был увеличен вдвое до 238 млрд руб. Завод «Ангстрем-Т» выпускал всю эту продукцию до 2022 года, но из-за санкций производство пришлось приостановить. Оно возобновится в связи с требованием локализации выпуска банковских и SIM-карт, пропусков и других компонентов с 2026 года. Ежегодный оборот SIM-карт в России оценивается в 100–150 млн штук — их стоимость с начала 2022 года растёт. Сейчас они закупаются преимущественно в Китае, но небольшие партии заказываются и у российских поставщиков, рассказали опрошенные «Коммерсантом» эксперты. Запуск их отечественного производства будет способствовать росту конкуренции на рынке и снижению зависимости от импорта, хотя нельзя пренебрегать такими аспектами как технические требования и финансовые условия поставок. Финансовые ожидания «НМ-Тех» от реализации проектов реалистичны, потому что в России есть спрос на эту продукцию. До начала украинских событий чипы для этой продукции закупались преимущественно у нидерландской NXP Semiconductors, а сейчас Россия сможет их экспортировать — потенциальными покупателями являются государства, находящиеся «под санкционным давлением» и страны Глобального Юга. Поначалу российская продукция будет дороже китайской, но по мере наращивания производства цены будут выравниваться. |