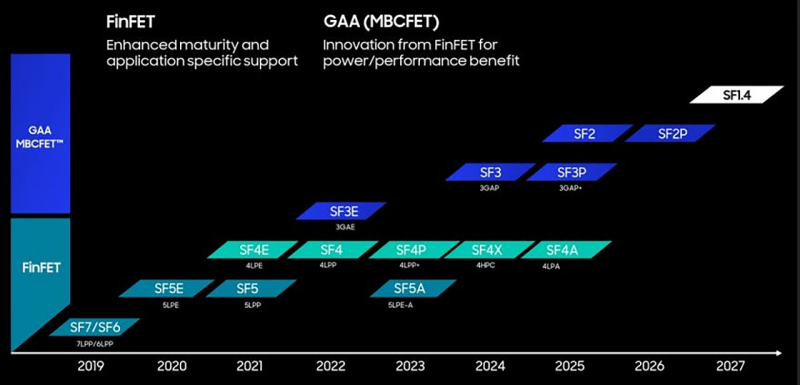

Хотя Samsung начала массовое производство чипов на базе техпроцесса SF3E (3 нм, транзисторы GAA) примерно год назад, к настоящему моменту мало кто из производителей электроники подтвердил его использование в своих продуктах. Недавно аналитики TechInsights выяснили, что одним из первых заказчиков 3-нм чипов у Samsung стала компания MicroBT, выпускающая ASIC-майнеры. Выполненный по технологии SF3E чип применяется в её криптомайнере Whatsminer M56S++.

Источник изображения: Arm

Специализированные интегральные схемы ASIC для добычи криптовалюты представляют собой небольшие чипы с относительно малым количеством входящих в их состав транзисторов и повторяющимися логическими структурами, похожими на простые битовые ячейки памяти SRAM. В целом за счёт простоты производства таких чипов это делает их весьма подходящей платформой для тестирования передовых технологически процессов. Поэтому совсем неудивительно, что техпроцесс SF3E нашёл своё первое практическое применение именно в среде криптомайнинга.

К сожалению, в открытом доступе о ASIC-майнере Whatsminer M56S++ не так много информации. Известно лишь, что система компании MictoBT на основе этого чипа обеспечивает хешрейт на уровне 240–256 Тхеш/с и обладает энергоэффективностью 22 джоуля на терахэш.

На данный момент неизвестно, используется ли 3-нм технология SF3E компании Samsung в каких-либо других коммерческих решениях помимо оборудования для майнига. Однако сама Samsung заявляет, что «использует этот техпроцесс в своих продуктах».

«Мы массово производим чипы на основе первого поколения 3-нм техпроцесса со стабильным уровнем выхода годных микросхем. С учётом этого опыта мы уже ведём разработку второго поколения техпроцесса, который обеспечит ещё более высокий выход годных чипов», — цитирует портал Tom’s Hardware одно из недавних заявлений компании.

По сравнению с техпроцессами 5-нм класса Samsung второго поколения (SF5, 5LPP), SF3E обещает снижение энергопотребления микросхем до 45 % при сохранении той же частоты работы, либо повышение производительности до 23 % при сохранении количества транзисторов и мощности. Кроме того, чипы с использованием SF3E занимают на 16 % меньшую площадь.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018