|

Опрос

|

реклама

Быстрый переход

Слухи: Microsoft одобрила новую игру Ninja Theory даже до релиза Senua's Saga: Hellblade II

21.05.2024 [17:33],

Михаил Романов

Вышедший сегодня, 21 мая, приключенческий боевик Senua's Saga: Hellblade II не станет последней игрой принадлежащей Microsoft британской студии Ninja Theory. Об этом со ссылкой на свои источники сообщает портал Windows Central. Вслед за внезапным закрытием руководством Microsoft трёх студий Bethesda, включая разработчиков Hi-Fi Rush из Tango Gameworks, игроки начали переживать, что следующей в очереди на ликвидацию может оказаться Ninja Theory. Опубликованное накануне релиза Senua's Saga: Hellblade II главой Ninja Theory Домом Мэттьюсом (Dom Matthews) душевное обращение к игрокам некоторые восприняли как своеобразное прощание. По данным же Windows Central, хоронить студию рано. Как передают «проверенные» информаторы Windows Central, Microsoft не только не собирается закрывать Ninja Theory в обозримом будущем, но даже одобрила студии разработку следующей игры. Зелёный свет на новый проект Ninja Theory получила до релиза Senua's Saga: Hellblade II. Если верить Windows Central, речь идёт не об экспериментальной Project: Mara (анонсирована в 2020 году), а о некой другой игре. Стоит отметить, что прошлым летом руководство Microsoft Gaming тоже обещало не закрывать Arkane Austin (Prey) после провала Redfall, но спустя чуть меньше года всё-таки это сделало. Что касается Senua's Saga: Hellblade II, то она вышла сегодня, 21 мая, на PC (Steam, Microsoft Store), Xbox Series X, S и в Game Pass. В день релиза игра получила первые оценки — средний рейтинг на Metacritic составил 81 %. «Аквариус» запустил производство отечественного ноутбука Cmp NE355 на чипе AMD Ryzen 6000

21.05.2024 [16:57],

Павел Котов

Группа компаний «Аквариус» сообщила о запуске производства ноутбука Aquarius Cmp NE355. Компьютер отличают совместимость с российскими платформами Astra Linux, «Альт», «РЕД ОС» и «РОСА Linux», качественные веб-камера и аудиосистема. Кроме того, он внесён в реестр отечественной радиоэлектронной продукции Минпромторга России.

Источник изображений: aq.ru Aquarius Cmp NE355 создавался в собственном центре разработок компании, а его выпуск осуществляется на её предприятиях. Пайка системной платы производится на заводе в Шуе, а сборка происходит на предприятии в Твери. Высокую производительность компьютера обеспечивают процессор AMD Ryzen 5 6000-й серии с интегрированной графикой и до 64 Гбайт оперативной памяти DDR5; объём SSD M.2 составляет 256 или 512 Гбайт — этого хватит для большинства рабочих задач.  Ноутбук оснащён 15,6-дюймовым экраном с разрешением Full HD, частотой обновления 60 Гц и антибликовым покрытием. На корпусе расположены по четыре порта USB Type-A и USB Type-С — один из последних предлагает передачу изображения и возможность зарядки, есть по одному DisplayPort 1.4 и HDMI 1.4, сетевой порт, слот для карт microSD, а также аппаратные выключатели веб-камеры и Wi-Fi. Присутствуют четыре динамика, блок микрофонов и камера разрешения Full HD. До конца года компания намеревается выпустить несколько десятков тысяч Aquarius Cmp NE355 — заказчики уже получили первые партии. Core42 и Cerebras построят в Техасе ИИ-суперкомпьютер с 173 млн ядер

21.05.2024 [16:36],

Руслан Авдеев

Базирующаяся в ОАЭ компания Core42 занялась строительством ИИ-суперкомпьютера, в эксплуатацию объект должны ввести до конца текущего года. HPC Wire сообщает, что компьютер Condor Galaxy 3 (CG-3) получит 192 узла с 5-нм мегачипами Cerebras WSE-3 и 172,8 млн ИИ-ядер. WSE-3 в 50 раз крупнее актуальных ИИ-ускорителей NVIDIA и, конечно, гораздо производительнее. По данным Core42, развёртывание CG-3 в Далласе (Техас) начнётся в июне и завершится в сентябре–октябре. Core42 уже считается значимым игроком на рынке ЦОД, HPC- и ИИ-систем. Машины G42 уже попадали в TOP500 — это системы Artemis (NVIDIA) и POD3 (Huawei). Последняя покинула рейтинг в 2023 году. Суперкомпьютер CG-3, как теперь сообщается, получит 192 узла CS-3. Каждый узел с чипом WSE-3 обеспечивает до 125 Пфлопс (FP16 с разрежением), так что общая производительность Condor Galaxy 3 составит 24 Эфлопс. Всего же Cerebras намеревается построить девять суперкомпьютеров семейства Condor Galaxy. Машины GC-1 и GC-2 на базе чипов WSE-2 также созданы при участии G42. Core42 появилась в 2023 году в результате слияния G42 Cloud и G42 Inception AI. Родительская компания G42, основанная в 2018 году, также сотрудничает с NVIDIA, AMD, OpenAI и другими компаниями. G42 не так давно попала под пристальное внимание американских властей. Её подозревали в том, что она помогала Китаю получать доступ к новейшим ускорителям NVIDIA и другому ИИ-оборудованию американских компаний. В результате, как считается, она была вынуждена отказать от сотрудничества с Huawei. Также сообщалось, что G42 заключила с американским правительством взаимовыгодное секретное соглашение — компания обязалась лишить КНР доступа к ускорителям, а в ответ ей самой разрешали сохранить доступ к продукции NVIDIA. Не исключено, что были оговорены и иные пункты. По некоторым данным, именно в то же время, когда было заключено соглашение с руководством США, Microsoft инвестировала в G42 около $1,5 млрд. AMD представила настольные процессоры EPYC 4004 — Socket AM5, до 16 ядер Zen 4 и встроенная графика

21.05.2024 [16:36],

Николай Хижняк

Компания AMD представила серию процессоров EPYC 4004 на архитектуре Zen 4, которые предназначены для малого и среднего бизнеса. Интересной особенностью чипов EPYC 4004 является то, что в отличие от остальных процессоров EPYC, предназначенных для серверного сегмента, новинки требуют для работы обычные материнские платы с процессорным разъёмом Socket AM5, что значительно упрощает их интеграцию.

Источник изображений: AMD В серию EPYC 4004 вошли чипы с количеством ядер от 4 до 16, поддерживающие от 8 до 32 виртуальных потоков, обладающие базовой частотой от 3,7 до 4,5 ГГц, максимальной частотой от 5,1 до 5,7 ГГц и номинальным TDP от 65 до 170 Вт. Два чипа (12-ядерный 4484PX и 16-ядерный 4584PX) из новой серии оснащены дополнительной кеш-памятью 3D V-Cache, благодаря чему общий объём кеш-памяти L3 доходит до 128 Мбайт. Объём кеш-памяти L3 других моделей варьируется от 16 до 64 Мбайт. Также процессоры EPYC 4004 оснащены встроенной графикой на архитектуре RDNA 2. Для EPYC 4004 заявляется поддержка до 192 Гбайт двухканальной оперативной памяти DDR5-5200 с функцией коррекции ошибок ECC, до 28 линий PCI Express 5.0, а также технологий AMD RAIDXpert2 для создания RAID-массивов и шифрования TSME. Сравнение с Intel Xeon E-2400

AMD сравнивает серию процессоров EPYC 4004 с чипами Intel Xeon E-2400. Процессоры AMD предлагают вдвое больше ядер, дешевле в расчёте на одно ядро, обладают более высокой базовой и максимальной частотами, поддерживают более быструю и ёмкую оперативную память. Чипы AMD также выигрывают в производительность в разных сценариях использования, в чём можно убедиться, взглянув на графики в галерее выше. Стоимость процессоров EPYC 4004 варьируется от $149 за четырёхъядерную модель 4124P до $699 за 16-ядерные модели EPYC 4564P и EPYC 4584X (c 3D V-Cache). В продаже новые процессоры доступны с сегодняшнего дня. Noctua вышла за рамки ПК: представлены вентиляторы и аксессуары Home для дома и офиса

21.05.2024 [16:32],

Анжелла Марина

Компания Noctua анонсировала запуск новой линейки продуктов Home, предназначенных для охлаждения домашней и офисной техники, а также других вариантов применения. Можно даже собрать необычный настольный вентилятор. В линейку входят два вентилятора и девять модульных аксессуаров, которые позволят эффективно решать типовые проблемы охлаждения различных устройств в доме и офисе.

Источник изображения: Noctua По словам генерального директора компании Роланда Моссига (Roland Mossig), технологии Noctua изначально создавались для охлаждения ПК. Однако производительность, бесшумность и надежность вентиляторов Noctua оказались востребованы и в других сферах. Промышленные клиенты и технически подкованные пользователи уже несколько лет используют эти вентиляторы не только для охлаждения компьютеров. Поэтому выпуск отдельной линейки для домашних и офисных нужд является логичным следующим шагом в расширении областей применения технологий компании. Стартовая линейка Noctua Home представляет из себя два укомплектованных, готовых к использованию вентилятора, а также девять модульных аксессуаров, каждый из которых позволяет использовать вентиляторы Noctua для типичных домашних, офисных или многоцелевых задач вентиляции.  Например, NV-FM1 — это универсальное крепление для вентиляторов диаметром 120 и 140 мм, которое можно использовать не только в качестве простой подставки на столах или других ровных поверхностях, но также можно прикрепить к стенам, потолку, мебели или другим объектам. Для применений, требующих сильного и сфокусированного воздушного потока, его можно использовать вместе со специальным усилителем NV-AA1-12. Оба вышеописанных продукта входят в комплект NV-FS1, включающий удостоенный наград вентилятор NF-A12x25, контроллер вентилятора NA-FC1, блок питания NV-PS1, который позволяет питать 12-В вентилятор от сети переменного тока 230/115 В, а также решетку вентилятора и удлинитель. Фактически, NV-FS1 — это прочный и бесшумный вентилятор премиум-класса, который можно установить практически в любом месте с помощью винтов, застежек-молний или встроенных магнитов. С охлаждением аудио- и видеотехники помогут универсальные прокладки NV-MPG1, которые позволяют установить на устройство вентилятор сверху (для устройств с вентиляционными отверстиями сверху). А вот NV-MPP1 крепятся снизу и подойдут для техники с нижними вентиляционными отверстиями. В универсальный же комплект NV-FS2 входят прокладки NV-MPG1, вентилятор NF-A12x25, контроллер NA-FC1, блок питания NV-PS1, контроллер вентилятора NA-FC1, решетка вентилятора и удлинительный кабель, что в итоге создает систему охлаждения для различных устройств, в том числе игровых консолей и мультимедийных систем. Наконец, Noctua представила хаб NV-FH2 является, по сути, улучшенной версией популярной модели NA-FH1. Он рассчитан на подключением и управления восемью вентиляторами. В отличие от предшественника, использует 12-вольтовый цилиндрический разъем питания и имеет съемную крышку, бесшумен и производителен. В сочетании с уже существующей линейкой вентиляторов Noctua диаметром от 40 до 200 мм новые аксессуары Home создают гибкий модульный инструментарий, который позволит клиентам решать типовые задачи охлаждения в домашних и офисных условиях. Китайские техногиганты снизили цены на доступ к своим моделям ИИ

21.05.2024 [16:16],

Павел Котов

Китайские технологические гиганты Alibaba и Baidu сообщили о снижении цен на большие языковые модели, составляющие основу продуктов с генеративным искусственным интеллектом. В секторе облачных вычислений Китая обостряется ценовая война, передаёт Reuters.

Источник изображения: baidu.com Облачное подразделение Alibaba сообщило о снижении цен на значение до 97 % на большие языковые модели семейства Tongyi Qwen. Так, доступ к модели Qwen-Long будет обходиться всего 0,0005 юаня ($0,000069) за 1000 токенов — единиц данных, обрабатываемых платформой. До этого цена за те же 1000 токенов была 0,02 юаня ($0,002768). Примеру конкурента последовала Baidu, которая через несколько часов объявила, что её модели Ernie Speed и Ernie Lite станут бесплатными для всех бизнес-пользователей. Ценовая война в сфере облачных вычислений в Китае продолжается уже несколько месяцев: недавно цены на работу с облачными ресурсами снизили Alibaba и Tencent. В конце 2022 года на волне успеха OpenAI ChatGPT в Китае началась волна инвестиций в проекты больших языковых моделей, после чего местные поставщики облачных решений начали предлагать услуги чат-ботов с ИИ для увеличения продаж. На текущем этапе ценовая война грозит снижением прибыли компаний: выпущенные в марте модели Ernie Speed и Ernie Lite от Baidu до сегодняшнего дня были платными для корпоративных клиентов. На прошлой неделе компания ByteDance объявила, что её основная большая языковая модель Doubao будет обходиться бизнес-пользователям на 99,3 % дешевле, чем в среднем по отрасли. Китайские компании монетизируют свои проекты в области ИИ преимущественно за счёт корпоративных пользователей, но в отдельных случаях платные услуги предлагаются и потребителям. К примеру, стартап Moonshot ввёл плату за приоритетный доступ к своему чат-боту для обеих категорий пользователей; а Baidu взимает с потребителей 59 юаней ($8,16) в месяц за доступ к своей самой мощной модели Ernie 4. Объём производства российского оптоволокна сократился

21.05.2024 [15:59],

Сергей Карасёв

В I квартале 2024 года объём производства российских оптоволоконных кабелей в натуральном выражении составил приблизительно 842 тыс. км. Это на 11 % меньше по сравнению с прошлогодним результатом, о чём сообщает газета «Коммерсантъ», ссылаясь на данные профильной ассоциации «Электрокабель». Говорится, что спрос на оптоволокно в России в годовом исчислении упал на 1 % — до 855 тыс. км. При этом в деньгах продажи уменьшились на примерно на 4 %, составив 2,7 млрд руб. Эксперты объясняют ситуацию несколькими причинами. Объём производства в РФ упал из-за сокращения числа государственных проектов, связанных с использованием оптоволоконного кабеля. Кроме того, увеличились поставки китайской продукции — на 5 % в 2023-м. Плюс к этому закупки оптоволокна телекоммуникационными компаниями в целом в I квартале снизились на 15–20 %. По оценкам, в 2023 году общий объём производства оптоволоконных кабелей в России составил 4,45 млн км, что на 2 % больше результата за предыдущий год. В деньгах рынок вырос на 25 % — до 13,8 млрд руб. В 2022 году на фоне сложившейся геополитической обстановки объём потребления оптоволокна снизился на 30 % из-за санкций и задержек с поставками оборудования. В 2023-м проблемы удалось частично решить, но достигнуть уровня 2021 года (около 4,7 млн км) всё равно не получилось. В «МегаФоне» и МТС отмечают, что работают только с поставщиками из России и Белоруссии, в «ВымпелКоме» — «преимущественно с отечественными производителями». Однако эксперты подчёркивают, что частные операторы, хотя и покупают отечественный кабель, но тот, который произведён из зарубежного волокна. Дело в том, что российское волокно дороже импортного, а участники рынка в сложной макроэкономической обстановке вынуждены экономить. Ранее говорилось, что на импортозамещение оптоволокна в РФ понадобится 20 млрд руб. В частности, Минпромторг объявил тендер на сумму от 1,09 млрд руб. на проведение опытно-конструкторских работ по созданию отечественной технологии выпуска кварцевых заготовок (преформ) для оптоволокна. Вместе с тем Федеральная антимонопольная служба (ФАС) России предлагает организовать в стране запуск полного цикла производства оптоволокна. «Джеймс Уэбб» приблизил учёных к разгадке тайны пухлой экзопланеты с плотностью хлопка

21.05.2024 [15:54],

Геннадий Детинич

Из более чем 5000 экзопланет учёные открыли единицы объектов с крайне низкой плотностью, которые стали называть пухлыми планетами (puffy planet). Загадку одной из таких планет, похоже, помог разгадать космический телескоп им. Джеймса Уэбба. Вчера в журнале Nature одновременно вышли две статьи, которые объясняют, как могла образоваться планета с плотностью хлопка.

Художественное представление экзопланеты WASP-107b. Источник изображения: NASA «Данные "Уэбба" говорят нам, что планеты, подобные WASP-107b, не должны были формироваться каким-то странным образом со сверхмалым ядром и огромной газовой оболочкой, — пояснил Майкл Лайн (Michael Line), экзопланетолог из Университета штата Аризона. — Вместо этого мы можем взять что-то более похожее на Нептун, с большим количеством камня и не таким большим количеством газа, просто увеличить температуру и это придаст ему тот вид, который мы наблюдаем [в случае WASP-107b]». Экзопланета WASP-107b была обнаружена в 2017 году у звезды на удалении 200 световых лет в созвездии Девы. Размеры WASP-107b примерно соответствуют размерам Юпитера, но её масса составляет всего 12 % от массы этого газового гиганта. Это делает экзопланету такой же пухлой, как разогретый в микроволновке зефир. Исходя из этих данных, экзопланета WASP-107b должна обладать экстремально небольшим каменистым ядром. Наблюдения показали, что атмосфера экзопланеты раздута сильнее, чем показывает моделирование. Хотя планета вращается очень близко к своей звезде (на расстоянии примерно равном 1/7 от Меркурия до Солнца), энергии звезды не хватило бы, чтобы нагреть и раздуть атмосферу экзопланеты до фиксируемых размеров. Будь ядро у экзопланеты больше, за время её существования атмосфера бы стала меньше за счёт остывания, но этого тоже нет. Больше ясности внёс космический телескоп «Уэбб», который дополнил предыдущие наблюдения «Хаббла» и одно прежнее собственное наблюдение. В спектре атмосферы экзопланеты учёные не обнаружили метан, хотя другие углеродсодержащие газы легко и обильно в ней распознавались. Это заставило сделать предположение, что ядро экзопланеты нагрето намного сильнее ожидаемого. Если это так, тот метан ещё в ядре планеты распадается на монооксид углерода и углекислый газ. Но откуда же берётся избыточное тепло, если энергии звезды недостаточно для нагрева? Как заявляют учёные, экзопланета WASP-107b вращается вокруг своей звезды по вытянутой орбите. Благодаря этому недра экзопланеты подвергаются приливной деформации. Именно эти процессы дают избыточное тепло, которое сильнее разогревает газы в ядре и нижние слои атмосферы. Внизу метан быстро распадается, а интенсивное перемешивание газа в атмосфере вымывает метан также из верхних её слоёв. Тем самым учёные объяснили сразу две загадки экзопланеты, почему она такая рыхлая и почему в её атмосфере нет метана. А ещё на этой экзопланете идут дожди из песка. Но это уже другая история. Microsoft добавила в Paint ИИ-генератор изображений по текстовому описанию или наброскам

21.05.2024 [15:24],

Владимир Фетисов

Компания Microsoft расширила возможности по созданию изображений с помощью своего графического редактора Paint. Для этого в приложение добавили инструмент на основе искусственного интеллекта Cocreator, который может генерировать изображения на основе текстовых подсказок или набросков пользователя.

Источник изображения: Devindra Hardawar / Engadget Софтверный гигант уже некоторое время экспериментирует с генерацией картинок с помощью нейросетей в Paint. Ранние версии инструмента Cocreator стали доступны разработчикам и участникам программы предварительной оценки Windows Insider ещё осенью прошлого года. Однако вместе со вчерашним анонсом Copilot Plus PC, компьютеров на Windows с аппаратным обеспечением для работы искусственного интеллекта, функция генерации изображений в Paint стала официальной. Во время упомянутого мероприятия представитель Microsoft продемонстрировал, как Cocreator объединяет наброски пользователя Paint с дополнительными текстовыми подсказками и создаёт на их основе полноценное изображение. Имеется возможность регулирования уровня вмешательства ИИ-алгоритма в работу пользователя. За счёт этого можно контролировать, насколько сильно Cocreator изменит исходный набросок. Разработчики отметили, что генерация картинок на основе набросок и текстовых подсказок работает быстрее, чем создание изображений только по описанию. Это также позволит добиваться более точного результата, отвечающего требованиям пользователя. «Прямиком из "Чёрного зеркала"»: пользователи раскритиковали функцию записи действий Recall в Windows 11

21.05.2024 [15:09],

Николай Хижняк

Пользователи с опасением восприняли новую ИИ-функцию Recall операционной системы Windows 11, которая будет записывать все действия пользователя для того, чтобы быстро вернуться к какому-либо действию в недавнем прошлом. С критикой новой функции выступил и Илон Маск (Elon Musk), сославшись на видео, в котором глава Microsoft Сатья Наделла (Satya Nadella) объясняет особенность работы Recall.

Источник изображения: Microsoft В видео, вызвавшем резонансную реакцию в социальных сетях, Recall описывается, как мощный ИИ-инструмент, который «постоянно делает скриншоты, запоминает и понимает всё, что происходит на вашем компьютере». Фактически речь идёт о «машине времени», которая следит за каждым вашим движением за ПК и позволяет вернуться обратно к нужному моменту временной шкалы (ранее открытому приложению, файлу, видео, странице в браузере и т.д.). Пример её работы можно увидеть на видео ниже. «Это не поиск по ключевым словам, это семантический поиск по всей вашей истории [использования компьютера]. Речь идёт не только о документах. По сути, мы можем воссоздать моменты из прошлого», — говорит Наделла в видео. В официальном блоге Microsoft указано, что Recall будет добавлена в состав Copilot, ИИ-помощника Windows 11. Илону Маску не понравилась идея того, что его компьютер будет постоянно за ним следить, о чём он сообщил на своей странице в социальной сети X, заявив, что обязательно выключит данную функцию. Маск провёл параллель между функцией Recall и популярным сериалом Netflix «Чёрное зеркало», в котором рассказывается, как передовые технологии оказывают манипулятивное воздействие на личную жизнь и поведение людей. «Это прямиком из Чёрного зеркала. Определённо отключу эту “функцию”», — заявил Маск. Другие пользователи социальной сети с ним согласились: «Нет, спасибо. Не хочу ежемесячно платить Microsoft за то, чтобы они за мной шпионили», — написал один комментатор. «Они даже не могут наладить поиск по меню “Пуск” и мы должны поверить, что эта фигня будет правильно работать», — написал другой комментатор. «Помните время, когда Windows кешировала изображения, что в итоге приводило к заполнению накопителя и невозможности пользоваться системой?», — добавил третий. В Microsoft сообщили, что Recall будет локально хранить записанные данные на устройстве пользователя. «Образы истории только ваши. Они будут храниться на вашем ПК. Можно будет удалять отдельные записи, настраивать и удалять диапазоны времени в настройках или приостанавливать работу в любой момент с помощью значка на панели задач. Также можно будет фильтровать приложения и веб-сайты, чтобы они не сохранялись в Recall. Вы всегда сами сможете контролировать свой уровень конфиденциальности», — говорится в блоге Microsoft. Спустя девять лет после релиза The Witcher 3: Wild Hunt на ПК получила редактор модов REDkit и поддержку «Мастерской Steam»

21.05.2024 [14:44],

Михаил Романов

Разработчики из польской студии CD Projekt Red сообщили о выходе для ПК-версии своего фэнтезийного ролевого экшена The Witcher 3: Wild Hunt обновления, обеспечивающего поддержку редактора модов REDkit. Упомянутый патч, судя по первым отзывам, занимает в районе 3 Гбайт и, по словам CD Projekt Red, вносит ряд изменений, призванных облегчить работу с пользовательскими модификациями. В частности, CD Projekt Red снабдила The Witcher 3 поддержкой «Мастерской Steam» — любую доступную модификацию теперь можно установить из Steam Workshop, нажав на кнопку «Подписаться». Разработчики подчеркнули, что пользователи и дальше смогут загружать моды для The Witcher 3: Wild Hunt через Nexus Mods и другие подобные платформы — интеграция «Мастерской Steam» эту возможность не отнимает. С выходом обновления в «Мастерской Steam» также появилась поддержка DLC-модов (то есть внедряющих в игру дополнительный контент), а добавлять новые ID мира в модификации стало проще. REDkit базируется на инструментах разработки The Witcher 3, поэтому «призван дать авторам модов почти безграничную свободу». Редактор дебютировал сегодня, 21 мая, и доступен покупателям игры на ПК бесплатно (Steam, GOG, EGS). The Witcher 3: Wild Hunt вышла на PC, PS4, PS5, Xbox One, Xbox Series X, S и Nintendo Switch, но REDkit будет эксклюзивом ПК-версии. В прошедшее воскресенье, 19 мая, игра отпраздновала своё девятилетие. Китайские SMIC и CXMT активизировали работу по импортозамещению расходных материалов для выпуска чипов

21.05.2024 [14:15],

Алексей Разин

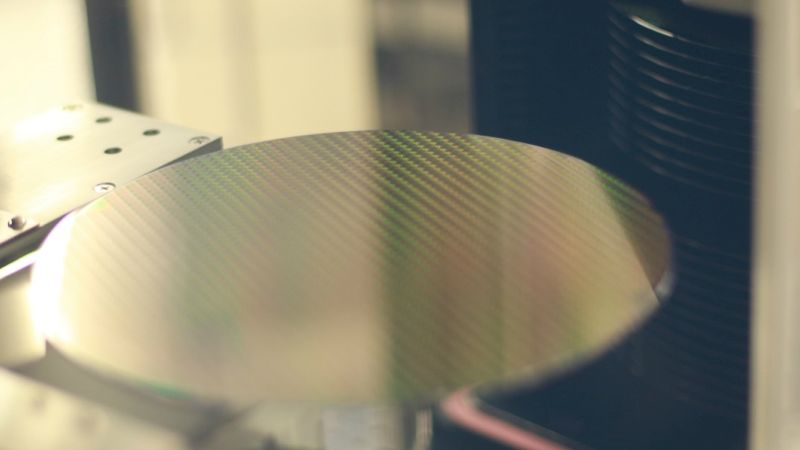

Новейшая история полупроводниковой отрасли уже знает примеры недружественных действий некоторых стран, которые подорвали способность других получать необходимые для выпуска чипов химикаты — достаточно вспомнить санкции на поставку технических газов в Южную Корею, которые ввели в 2019 году власти Японии. Китай в такой ситуации оказаться не желает, а потому местные компании активно ищут поставщиков сырья и материалов среди соотечественников.

Источник изображения: SMIC Об этом сообщает издание Nikkei Asian Review со ссылкой на собственные информированные источники. Находящаяся с конца 2020 года под американскими санкциями китайская компания SMIC сейчас обратилась к своим клиентам с просьбой помочь в поиске китайских поставщиков кремниевых пластин, химикатов и технических газов, которые позволили бы снизить зависимость от импорта в своей деятельности по контрактному выпуску полупроводниковых компонентов. Инициатива зародилась ещё в прошлом году и постепенно набирает обороты. Крупнейший в Китае производитель оперативной памяти CXMT также активно ищет локальные альтернативы поставщикам материалов и сырья из-за границы, по данным источника. При этом компания ссылается на некие положения национальной политики в данном вопросе. Полномасштабные санкции США против компании CXMT ещё не развёрнуты, но с учётом наличия у неё амбиций по освоению выпуска современной памяти HBM, которая нужна для ускорения работы систем искусственного интеллекта, это лишь вопрос времени. Запрет на поставку в Китай передового оборудования для производства чипов введён США, Японией и Нидерландами уже давно, а вот поставщики сырья и материалов пока таких ограничений не чувствуют. Впрочем, взятый китайскими производителями чипов курс на импортозамещение даже без специфических санкций уже начал бить по бизнесу зарубежных поставщиков материалов и сырья, которые имели локальные предприятия в Китае. Отказ от их продукции в пользу аналогов китайского происхождения вынудил многие зарубежные компании продать предприятия и уйти с китайского рынка полностью. Оставшиеся ищут возможность создать с китайскими партнёрами совместные предприятия, если это будет допускать политическая конъюнктура. Пока китайские производители чипов активнее всего переходят на отечественные материалы в сегменте техпроцессов от 55 до 40 нм, поскольку в этом случае проще найти аналоги китайского происхождения сносного качества, но постепенно тенденция перекинется на техпроцессы 28 нм и более тонкие. Кстати, в сфере услуг по тестированию и упаковке чипов усилия китайских компаний по импортозамещению уже привели к тому, что многие компании с мировым именем были вынуждены покинуть местный рынок, а профильная отрасль КНР стала второй по величине после Тайваня. По словам представителей зарубежного бизнеса, как только китайские производители получают доступ к китайскому сырью адекватного качества, от услуг зарубежных поставщиков они сразу же отказываются. Первый в мире коммерческий космический самолет Dream Chaser прибыл во Флориду для последних тестов перед полётом на МКС

21.05.2024 [14:13],

Геннадий Детинич

Первый в мире коммерческий космический самолет Dream Chaser прибыл в Космический центр NASA им. Кеннеди во Флориде, откуда путь ему только в космос. Отправка самолёта в полёт ожидается в конце текущего года на ракете Vulcan компании ULA. В центре NASA самолёт (космоплан) пройдёт завершающие проверки, получит тепловую защиту и в комплекте с одноразовым грузовым контейнером будет установлен на ракету для запуска.

Художественное представление космоплана Tenacity. Источник изображений: NASA Проекту космического самолёта Dream Chaser DC-100 Tenacity в этом году исполняется 20 лет. Изначально он задумывался как лёгкая альтернатива «Шаттлам». В 2014 году проект отвергли в пользу кораблей компании Boeing и SpaceX, которые поделили контракт NASA общей стоимостью $7 млрд по доставке экипажей на МКС на коммерческой основе. К проекту коммерческого многоразового космоплана NASA вернулось в 2016 году, вновь заключив договор на его разработку с компанией Sierra Space (ранее этим занималась Sierra Nevada Corporation).  Согласно предварительной договорённости, многоразовый космический самолёт Tenacity совершит минимум 7 грузовых рейсов к МКС. В свой первый рейс, как сказано выше, самолёт будет отправлен в конце текущего года. Основной грузовой отсек самолёта одноразовый, за что он получил название «Падающая звезда». Он крепится к задней части самолёта и может вмещать в себя свыше 3,5 т полезной нагрузки: провизии, оборудования, наборов для экспериментов и другое. После освобождения от груза в отсек закладывается мусор с МКС для сжигания в верхних слоях атмосферы вместе с контейнером. Сам самолёт садится на своих крыльях и двигателях на фактически любую взлётно-посадочную полосу и будет использован повторно. Навесные грузовые контейнеры, конечно же, каждый раз нужно будет изготавливать новые и их объём со временем будет расти, благо этот груз в космос поднимает ракета, а самолёт только корректирует орбиту и проводит стыковку с МКС.

Самолёт в конфигурации с внешним грузовым контейнером В свой первый полёт в состоянии стыковки с МКС самолёт проведёт 45 суток. В последующем время стоянки будет увеличено до 75 суток. Во внутреннем контейнере самолёт способен доставить на Землю 2,5 т полезной нагрузки со станции: результаты экспериментов и другое. Правда, посадка будет жёсткая — со скоростью около 1,5 g, поэтому о надёжной упаковке хрупких образцов придётся побеспокоиться особенно хорошо. Авторы Norco выпустят «микроприключение» Silenus про андроида на населённом ИИ заводе — в Steam вышло необычное демо

21.05.2024 [14:11],

Михаил Романов

Творческое объединение Geography of Robots, в 2022 году подарившее игрокам сюрреалистическое приключение Norco, готовит к релизу новый проект — он называется Silenus и уже получил «экспериментальное» демо в Steam. События Silenus вертятся вокруг нефтеперерабатывающего завода Gulf Flow, который перешёл под контроль загадочной корпорации Rubens Link. Официально речь идёт о внедрении новых технологий автоматизации, но на деле всё куда запутаннее. Игрокам достанется роль флагманского андроида Rubens Link под названием «Титан» (Titan). В роли упомянутого робота пользователям предстоит разобраться в происходящем и с головой углубиться в кроличью нору Gulf Flow. Скриншоты Silenus

Геймеры будут исследовать трёхмерное окружение завода, расшифровывать подсказки из компьютерных записей, выброшенных дневников и останков пропавших рабочих, решать головоломки и взаимодействовать с уникальными персонажами. В рамках Silenus разработчики вновь скооперировались с луизианской сладж-группой Thou (см. Norco). Музыканты сейчас готовятся к выходу альбома Umbilical (31 мая), и экспериментальным характером демо игры обязано именно ему. Демо Silenus предлагает разблокировать все треки из Umbilical и прослушать их во внутриигровом плеере (доступен в главном меню и на экране паузы). Разработчики предупреждают, что к релизу полной версии проект существенно изменится. Silenus позиционируется в качестве «микроприключения» на два с половиной часа и пока не имеет сроков выхода, а демо будет доступно до 31 мая. Тем временем Norco до 23-го числа продаётся в Steam со скидкой 60 % (220 рублей). Ethereum взлетел более чем на 20 % и продолжает расти на фоне слухов об одобрении спотовых Ethereum-ETF

21.05.2024 [13:53],

Владимир Мироненко

Во вторник криптовалютный рынок продолжил свой рост на фоне слухов о скором одобрении Комиссией по ценным бумагам и биржам США (SEC) спотовых ETF на Ethereum. Как стало известно, комиссия запросила обновлённую документацию у потенциальных эмитентов ETF и бирж, что укрепило надежды на положительное решение по этому вопросу.

Источник изображения: Kanchanara/unsplash.com После резкого скачка в понедельник на 20 % цена Ethereum (ETH) выросла по данным Coin Metrics во вторник ещё на 9 % до $3680,98. «ETH резко вырос вскоре после того, как начали распространяться слухи о том, что SEC может все-таки одобрить спотовые ETH ETF на этой неделе», — сообщил Бартош Липиньски (Bartosz Lipiński), генеральный директор Cube Exchange. Окончательные решения по заявкам VanEck и Ark Invest на создание спотовых Ethereum-ETF будут приняты в этот четверг и пятницу соответственно. По заявкам BlackRock, Fidelity, Invesco, Grayscale и Bitwise Asset Management решения должны быть приняты позже в этом году. На фоне роста криптовалютного рынка биткоин прибавил во вторник в цене 2 % до $71 350, а вчера он вырос на 8 % по сравнению с предыдущим днём, и снова стал дороже $70 000. Это позитивно отразилась на позициях на бирже ряда компаний, занимающихся майнингом биткоинов, включая Marathon Digital, чьи акции выросли на 3 %. Акции компаний, связанных с криптовалютой, тоже выросли в цене — у Coinbase и Microstrategy на 2 % в ходе расширенных торгов, а у Robinhood — на 3 %. HP перестанет выпускать компьютеры Spectre, Envy и Pavilion — их заменят Omni и Elite

21.05.2024 [13:45],

Павел Котов

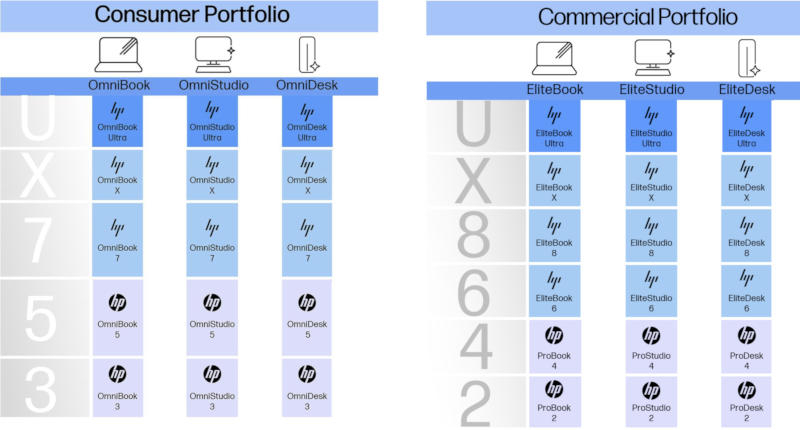

Компания HP решила кардинально поменять схему наименования своей продукции — компания откажется от таких названий ноутбуков как Pavilion, Spectre или Envy. На смену им придут серии OmniBook и EliteBook. Что интересно, бренд OmniBook компания уже использовала, но очень давно — под ним выпускались ноутбуки с 1993 по 2002 год. Марка EliteBook также не является новой — под ней бизнес-ноутбуки выпускаются с 2008 года.

Источник изображений: HP Решение было принято на фоне запуска корпорацией Microsoft концепции ноутбуков нового поколения Copilot Plus PC. Компания HP оказалась в числе первых производителей компьютеров нового поколения, представив ноутбуки OmniBook X AI и EliteBook Ultra G1q AI. Оба дебютировали в рамках новой системы наименования. Теперь HP будет использовать бренд Omni для потребительской продукции и Elite для корпоративной. Каждое направление будет подразделяться на Book (для ноутбуков), Studio (для моноблоков) и Desk (для десктопов). Кроме того, потребительские продукты будут выпускаться в сериях 3, 5, 7, X и U (Ultra), а коммерческие — в сериях 2, 4, 6, 8, X и Z.  Компания решилась на эти перемены, «поскольку компьютеры с искусственным интеллектом быстро трансформируют среду персональных компьютеров, [и] мы увидели возможность использовать сложные технологии и передавать их удивительно простым способом». На начальном этапе новые названия получили ноутбуки на процессорах Qualcomm Snapdragon X — за ними последуют компьютеры на чипах AMD и Intel. HP откажется от существующих серий компьютеров: полупрофессиональных Spectre, премиальных Envy, бюджетных Pavilion и передовых бизнес-продуктов Dragonfly. Суббренд HP Omen, под которым компания выпускает игровую продукцию, перемены не затронут. Операционный директор Apple провёл тайные переговоры с TSMC по поводу выпуска ИИ-чипов

21.05.2024 [13:39],

Алексей Разин

Решение Apple начать использование процессоров M2 Ultra собственной разработки в составе своей серверной инфраструктуры, о котором стало известно недавно, может оказаться лишь первым шагом на пути создания специализированных чипов для ускорения искусственного интеллекта. По слухам, представитель руководства Apple недавно посетил Тайвань для проведения переговоров с TSMC о перспективе выпуска ИИ-чипов.

Источник изображения: TSMC Как отмечает издание Economic Daily News, во время своей поездки на Тайвань операционный директор Джефф Уильямс (Jeff Williams) встретился с генеральным директором TSMC Си-Си Вэем (C.C. Wei). Встреча не предавалась широкой огласке и была, как считается, посвящена обсуждению возможности TSMC наладить контрактный выпуск чипов Apple собственной разработки для серверных систем искусственного интеллекта. Руководители также обсуждали возможности TSMC в сфере упаковки и тестирования чипов со сложной пространственной компоновкой. Последние, как известно, в последние месяцы почти полностью направлены на удовлетворение спроса Nvidia на чипы для ускорителей вычислений. Перспективные чипы серверного назначения Apple будет использовать в собственной вычислительной инфраструктуре, но из-за высокой себестоимости не станет продвигать в сегмент потребительских устройств. По сути, на открытом рынке они так и не появятся. Apple остаётся одним из крупнейших клиентов TSMC, она традиционно получает доступ к новым техпроцессам этого подрядчика первой. В текущем году выручка TSMC от оказания услуг Apple приблизится к рекордным $19 млрд, как считают некоторые эксперты. Senua's Saga: Hellblade II не оставила критиков равнодушными — первые оценки одного из главных эксклюзивов Xbox в 2024 году

21.05.2024 [13:12],

Михаил Романов

Главный эксклюзив Xbox весны 2024 года — приключенческий боевик Senua's Saga: Hellblade II от студии Ninja Theory — удостоился первых оценок от западной прессы. К единому мнению критики насчёт игры не пришли. На Metacritic накопилось уже больше сотни обзоров Senua's Saga: Hellblade II со средним рейтингом 81 %. На OpenCritic картина схожая — 84 % при 70 рецензиях (игру рекомендуют 86 % критиков). Стоит отметить, что разброс оценок в случае с Senua's Saga: Hellblade II оказался на редкость высок: с «десятками» и «девятками» соседствуют «семёрки» и «шестёрки» (в том числе от крупных изданий вроде GameSpot, VGC и PC Gamer). Рецензенты остались в восторге от аудиовизуальной стороны Senua's Saga: Hellblade II и актёрской игры главных звёзд. Похвалы также удостоилась сюжетная составляющая и геймплейные улучшения по сравнению с Hellblade: Senua’s Sacrifice. В минусы проекту записали проседающий темп повествования, слишком простые загадки, однотипные сражения и локации, низкую вариативность врагов. По мнению некоторых критиков, сиквел вышел чересчур консервативным. Senua's Saga: Hellblade II оказалась одним из самых впечатляющих визуально эксклюзивов Microsoft, который, как и первая часть (те же 80 % на релизе), нашёл отклик далеко не во всех критиках. Senua's Saga: Hellblade II вышла сегодня, 21 мая, на PC (Steam, Microsoft Store), Xbox Series X и S, а также в Game Pass (PC и Xbox). Игра получила русские субтитры и до сих пор продаётся в российском Steam (3119 рублей). Neuralink разрешили вживить мозговой имплант в мозг второму пациенту

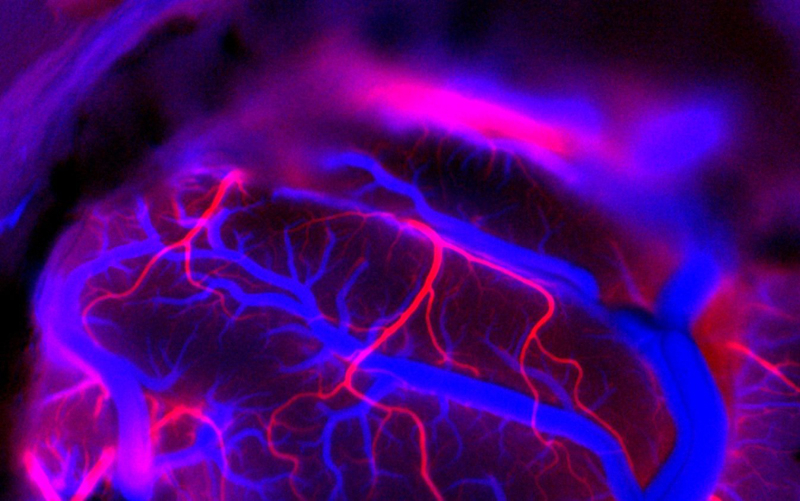

21.05.2024 [13:11],

Владимир Фетисов

Компания Neuralink, основателем и владельцем которой является американский бизнесмен Илон Маск (Elon Musk), получила разрешение американского регулятора на вживление мозгового имплантата второму пациенту. Это случилось после того, как разработчики сумели найти решение проблемы с задержками в работе устройства, которые возникают у первого пациента.

Источник изображения: Neuralink Разрешение выдало Управление по контролю качества пищевых продуктов и лекарственных средств, являющееся подразделением Министерства здравоохранения и социальных служб США. Ранее в этом месяце Neuralink сообщила, что ультратонкие электроды, помещённые в кору головного мозга первого пациента, сместились. В СМИ также появлялась информация о том, что компания знала о возможности возникновения такой ситуации, поскольку аналогичные проблемы случались во время тестирования имплантатов на животных. Для решения этой проблемы Neuralink намерена размещать ультратонкие электроды глубже в коре головного мозга. Согласно имеющимся данным, Neuralink планирует вживить имплантат второму пациенту в июне, а всего в этом году провести 10 таких операций. В настоящее время более 1000 парализованных людей зарегистрировались в реестре пациентов компании и ожидают своей очереди на операцию. В ближайшие несколько месяцев компания также планирует подать заявки регулирующим органам Канады и Великобритании, чтобы получить разрешение на проведение операций по вживлению мозговых имплантатов в этих странах. Скарлетт Йоханссон запретила использовать свой голос для ChatGPT — OpenAI не послушалась и пытается договориться

21.05.2024 [13:06],

Павел Котов

Скарлетт Йоханссон (Scarlett Johansson) заявила, что OpenAI обращалась к ней с просьбой стать голосом ChatGPT, а после отказа компания продолжила работать в этом направлении и запустила систему с голосом, очень похожим на её. В этой связи, сообщила актриса, она была «вынуждена нанять адвоката»; она также направила в OpenAI два письма с просьбой разъяснить ситуацию. В OpenAI рассказали, что пытаются договориться с актрисой.

Источник изображения: Growtika / unsplash.com «В сентябре прошлого года мне поступило предложение от Сэма Альтмана (Sam Altman), который хотел нанять меня для озвучения актуальной системы ChatGPT 4.0», — рассказала Йоханссон. По её словам, Альтман связался с её агентом всего за два дня до того, как OpenAI дополнила ChatGPT голосовыми технологиями — тогда актриса призвала компанию пересмотреть своё решение. Альтман признавался, что восхищается работой Йоханссон. Он называл фильм «Она», в котором актриса озвучила голосового помощника с искусственным интеллектом, своей любимой картиной. А на минувшей неделе, когда было представлено очередное обновление ChatGPT, гендиректор OpenAI разместил в соцсети X публикацию с одним лишь словом «Она». Вместе с тем, он отверг связь между голосом Sky в ChatGPT и голосом актрисы. «Голос Sky не принадлежит Скарлетт Йоханссон, и никогда не существовало задумки, чтобы он напоминал её голос. Прежде чем обращаться к мисс Йоханссон, мы выбрали актрису для озвучения Sky. Из уважения к мисс Йоханссон мы приостановили работу голоса Sky в наших продуктах. Жаль, что у нас не получилось пообщаться с мисс Йоханссон лучше», — заявил Альтман ресурсу The Verge. Вариант голоса Sky стал доступен в ChatGPT с сентября прошлого года, но его сходство с голосом Скарлетт Йоханссон стало очевидным лишь с последним обновлениям чат-бота: по словам актрисы, она была «шокирована, разгневана и не поверила тому», насколько «устрашающе похожим» показался голос Sky ей самой. О намерении подать на OpenAI в суд она пока не говорила — пока актриса только хочет объяснений. Она говорит, что ищет «решения в прозрачной форме» и просит компанию «подробно описать точный процесс, с помощью которого они создали» голос Sky. В OpenAI тоже нацелены на мирное разрешение инцидента. Отключив вариант ассистента, напоминающий голос актрисы, компания связалась с представителями актрисы. «Мы ведём обсуждение с командой [Скарлетт Йоханссон] потому что, кажется, возникли некоторые разночтения. Мы хотим серьёзно отнестись к отзывам и выслушать опасения», — заявила руководитель отдела моделирования поведения OpenAI Джоан Джанг (Joanne Jang). Samsung представила Arm-ноутбуки Galaxy Book4 Edge — их покупателям подарят 50" 4К-телевизоры

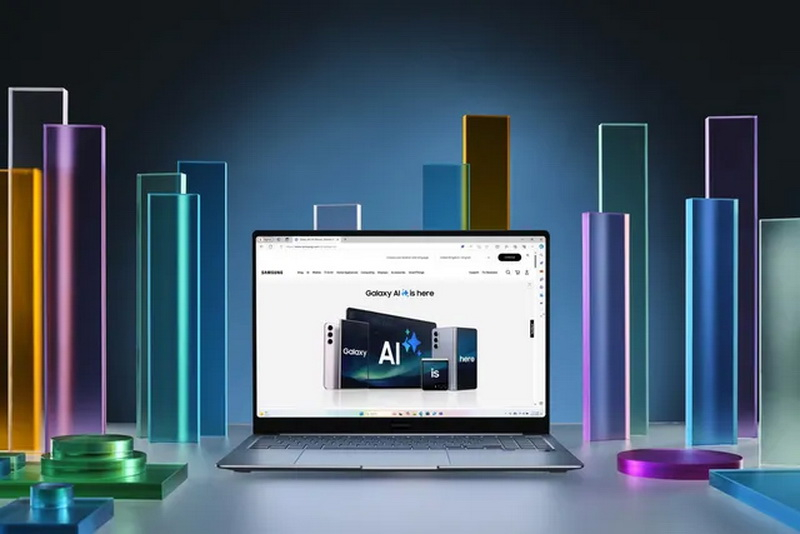

21.05.2024 [12:59],

Николай Хижняк

Компания Samsung вчера представила 14- и 16-дюймовые ноутбуки Galaxy Book4 Edge в рамках новой концепции продуктов Copilot Plus PC компании Microsoft. Что интересно, при предзаказе одного из этих ноутбуков Samsung подарит 50-дюймовый 4K-телевизор.

Источник изображений: Samsung Стоимость 14-дюймового Galaxy Book4 Edge начинается с $1349,99. За эту цену покупатель получит ноутбук с 12-ядерный процессором Qualcomm Snapdragon X Elite, работающим в диапазоне частот от 3,4 до 4,0 ГГц, 16 Гбайт оперативной памяти и SSD объёмом 512 Гбайт, который при желании можно будет заменить накопителем объёмом 1 Тбайт.  Ноутбук оснащён 14-дюймовым AMOLED-дисплеем с разрешением 2880 × 1800 пикселей, частотой обновления 120 Гц, яркостью до 500 кд/м2, поддержкой HDR и VRR, а также 120-процентным охватом цветового пространства DCI-P3. Лэптоп также предлагает два порта USB4 (Type-C), один HDMI 2.1 и комбинированный 3,5-мм аудиовыход.  Шестнадцатидюймовый вариант Galaxy Book4 Edge предлагается в двух версиях. Одна оснащается флагманским процессором Snapdragon X Elite с частотой до 4,2 ГГц и SSD объёмом 1 Тбайт, другая предлагает тот же процессор, что и 14-дюймовая модель и SSD объёмом 512 Гбайт. Стоимость первого варианта составляет $1749,99, а второго — $1449,99. Характеристики дисплея, за исключением диагонали, у 16-дюймового Galaxy Book4 Edge такие же, как у 14-дюймовой модели. В дополнении к двум USB4 (Type-C), одному HDMI 2.1 и комбинированному 3,5-мм аудиовыходу 16-дюймовая модель оснащена портом USB 3.2 Type-A и считывателем карт памяти microSD.  Согласно пресс-релизу Samsung, все три модели Galaxy Book4 Edge готовы предложить только 16 Гбайт оперативной памяти, что является необходимым минимумом для ПК категории Copilot Plus PC. Все ноутбуки Samsung оснащены технологией защиты Knox, а также набором приложений, которые позволяют быстро обмениваться данными со смартфонами серии Galaxy.  Предзаказы на ноутбуки Galaxy Book4 Edge открыты с 20 мая. При покупке каждого, пока длится период предзаказов, компания подарит бюджетный 50-дюймовый телевизор стоимостью $379. Марсоход Perseverance добыл лучший образец Марса для поиска следов древней жизни

21.05.2024 [12:29],

Геннадий Детинич

На днях представитель миссии NASA по управлению марсоходом Perseverance сообщил, что ровер, по всей видимости, смог взять наилучший образец породы Красной планеты, по образцам которой можно будет узнать о существовании на древнем Марсе биологической жизни. Именно в таких породах учёные на Земле находят следы древнейших микроорганизмов. Марс в этом плане ничем не должен отличаться, поэтому впереди нас ждут удивительные открытия. Конечно, собранные Perseverance образцы ещё предстоит вернуть на Землю. Миссия по их возврату во многом уже проработана, но столкнулась с чрезвычайным перерасходом средств и многолетними задержками. Команду марсохода это не смущает. Она продолжает миссию по сбору образцов. Всего должны быть заполнены 38 титановых пробирок. Около 70 % из них уже заполнены образцами пород, поверхности, кернов и даже воздуха планеты. Марсоход берёт два образца в каждой точке. Одну пробирку потом оставляют на поверхности планеты в импровизированных «хранилищах» — фактически просто на песке под открытым небом, а вторая хранится на борту марсохода. Миссия по возврату образцов на Землю либо заберёт контейнер с Perseverance, если марсоход не затеряется в песках Марса, либо подберёт пробирки с поверхности роботизированными вертолётами (ранее для этой цели предлагалось использовать небольшой ровер). В «ключевых» для поиска признаков древней жизни на Марсе образцах, взятых в районе Залива Лефрой (Lefroy Bay) в кратере Езеро, обнаружен гидратированный кремнезём. Его распознали с помощью камеры марсохода. К сожалению, более детальный анализ образца на месте невозможен. Более того, даже грубый анализ вещества стал недоступным для условий Марса. Предназначенный для этого спектральный прибор SHERLOC временно считается нерабочим — у него отказала заслонка. Проблема может быть решена в течение следующих месяцев, но это неточно. Марсоход продолжит собирать образцы, продвигаясь по более сложному участку. Он попытается подняться по внутреннему склону кратера — предполагаемому бывшему склону берега древнего озера. Это наилучшее место для сбора образцов с донными отложениями в разные эпохи. Предварительный анализ собранных образцов всё более явно свидетельствует о существовании воды на древнем Марсе, а если там была вода, значит, существует большая вероятность зарождения на Марсе жизни в древности. Пусть даже микробной. В любом случае, это станет подтверждением того, что в плане появления жизни Земля не уникальна, и во Вселенной точно есть жизнь и не одна. ASML и TSMC придумали, как удалённо испортить EUV-оборудование в случае вторжения Китая

21.05.2024 [12:12],

Алексей Разин

На Тайване производится более 90 % мирового объёма чипов с использованием передовой литографии. Компания ASML поставила своим клиентам с 2016 года более 200 сканеров для работы с EUV-литографией, многие из них сейчас эксплуатируются на Тайване компанией TSMC. Сообщается, что у компаний ASML и TSMC есть способы удалённо вывести из строя самые сложные в мире машины для производства микросхем в случае вторжения Китая на Тайвань.

Источник изображения: ASML Как отмечает Bloomberg, не предаваемые особой огласке консультации американских чиновников с представителями Нидерландов и Тайваня касались обсуждения возможных последствий захвата острова китайскими военными. Представители ASML успокоили американских партнёров, заявив, что могут дистанционно вывести из строя литографическое оборудование класса EUV, эксплуатируемое на Тайване. Это было подтверждено тематическими испытаниями, которые ASML проводила, имитируя в ходе учений действия компании в случае захвата Тайваня. Также возможность удалённо вывести из строя передовое оборудование имеется у эксплуатирующей его TSMC. По всей видимости, ASML сохраняет доступ к своему экспортируемому оборудованию по глобальным каналам связи, поскольку он позволяет ей удалённо диагностировать возникающие технические неполадки и проводить настройку уже после того, как оборудование установлено на предприятии клиента. Соответственно, в случае серьёзной опасности ASML имеет возможность дистанционно нарушить работу программного обеспечения, управляющего оборудованием, сделав его непригодным для использования посторонними. Данная информация не была подтверждена представителями официальных структур США и Нидерландов, либо сотрудниками компаний ASML и TSMC, как отмечает Bloomberg. Готовность прибегнуть к осознанному саботажу в прошлом году подтвердил и председатель совета директоров TSMC Марк Лю (Mark Liu). По его словам, если оккупанты доберутся до предприятий этой компании, они застанут их в неработоспособном состоянии. Как отметил глава правления TSMC, никто не может овладеть компанией силой. Volvo представила тягач с полным автопилотом — он готов к массовому производству

21.05.2024 [12:05],

Павел Котов

Компания Volvo представила свои первый «готовый к производству» беспилотный грузовой тягач, разработанный совместно с Aurora — основанной выходцами из Google, Uber и Tesla компанией, которая занимается созданием технологий автопилота.

Источник изображения: aurora.tech Машина построена на базе модели Volvo VNL, предназначенной для дальних перевозок. Её беспилотная версия оборудована множеством камер и сенсоров, данные с которых обрабатываются системой Aurora с возможностью автономного управления четвёртого уровня — она позволяет обходиться без человека за рулём. Машина была «специально спроектирована и построена» для системы автопилота Aurora. Запуск модели в серийное производство поможет компаниям окупить средства, которые они вложили в разработку беспилотного транспорта. Автотягачи нового поколения будут выпускаться на заводе Volvo в Дублине (США, шт. Вирджиния) — это крупнейшее в мире предприятие компании. Volvo, которая производит около 10 % всех грузовиков класса 8 (с грузоподъёмностью более 15 т) в мире, с 2018 года сотрудничает в Aurora в области решений для беспилотного транспорта. В этом году, сообщила Aurora, будут выпущены около 20 полностью беспилотных машин, а в 2025 году их число увеличится до 100. Компания также работает с немецким автопроизводителем Continental, который планирует начать массовое развёртывание беспилотного транспорта в 2027 году. В отличие от таких разработчиков систем автопилота как Tesla и Cruise, компания Aurora не отметилась громкими происшествиями и не привлекла пристального внимания со стороны властей. По итогам I квартала 2024 года она сообщила о чистом убытке в размере $165 млн — на 16 % больше, чем за аналогичный период годом ранее. SpaceX провела генеральную репетицию заправки Starship перед четвёртым тестовым запуском

21.05.2024 [12:01],

Геннадий Детинич

Компания SpaceX провела 20 мая генеральную репетицию подготовки ускорителя Super Heavy и корабля Starship к четвёртому тестовому запуску. Это была «мокрая репетиция» с полной заправкой криогенным топливом баков ускорителя и корабля. Поскольку, по-видимому, всё прошло успешно, запуск может состояться в ближайшее время — уже через пару недель, о чём в сети X сообщил Илон Маск (Elon Musk).

Источник изображения: SpaceX Гигантская ракета Starship высотой 122 м — самая высокая и самая мощная в истории, совершила три запуска с целью подъёма на орбитальную высоту (задача выйти на орбиту пока не ставится). Все три закончились разного степенью катастрофами, хотя каждый последующий запуск был заметно лучше предыдущего. Так, во время третьего испытательного полёта, который состоялся 14 марта 2024 года, корабль смог отделиться от первой ступени и даже совершить выход в космос и последующий спуск, в ходе которого, правда, он развалился на три больших фрагмента. Уверения Маска о намерении запустить ракету в четвёртый раз через две недели не следует воспринимать как истину в последней инстанции. Расследование Федерального управления гражданской авиации аварии во время третьего старта всё ещё не завершено и новая лицензия на запуск, соответственно, не выдана. Но дело определённо идёт быстрее, чем раньше. Теперь компания SpaceX получает лицензию на новые запуски Starship всё быстрее и быстрее. Поэтому у уверенности Илона Маска в скором старте мегаракеты есть крепкие основания. Ракета Starship в составе многоразового ускорителя Super Heavy с 33 двигателями Raptor и многоразового корабля Starship с 6 двигателями почти в два раза мощнее лунной ракеты Space Launch System NASA, которая доставила корабль «Орион» на орбиту Луны. В планах агентства — использовать корабль Starship для первой за более чем 50 лет высадки астронавтов на лунную поверхность. В перспективе Starship должен стать многоразовой платформой для освоения Луны и колонизации Марса. |