|

Опрос

|

реклама

Быстрый переход

Инженеры улучшили 60-летнюю технологию выпуска чипов — КМОП+ сделает процессоры компактнее и эффективнее

15.08.2025 [10:42],

Геннадий Детинич

Борьба за энергоэффективность классических полупроводников выходит на новый уровень. Стартап NeoLogic из Израиля на пальцах объяснил отсталость техпроцессов КМОП-производства чипов и предложил перейти на техпроцесс КМОП+ (CMOS+), лишённый множества недостатков предшественника. Это тем более важно в условиях повсеместного насаждения искусственного интеллекта и нейросетей, которые пожирают всю свободную энергию, где бы то ни было.

Руководство NeoLogic. Источник изображения: NeoLogic Идеи NeoLogic нашли отклик в сердцах инвесторов. Недавно компания привлекла $10 млн для разработки энергоэффективных серверных процессоров, первую версию которого намерена представить до конца текущего года, а уже в 2027 году разработчик намерен приступить к массовому внедрению новой парадигмы в серверных и других решениях. Так что же предлагает NeoLogic взамен комплементарной структуры металл–оксид–полупроводник, представляющей собой массив элементов из тесно связанных пар транзисторов с разной проводимостью? Схемы КМОП изобретены в начале 60-х годов прошлого века и стали спасением для электроники 90-х и всех последующих лет. За счёт тесного размещения на кристалле множества пар разнополярных транзисторов они обеспечивают высокое быстродействие, обладают меньшими задержками и отличаются минимальным потреблением в статическом режиме. Их главный недостаток — сравнительно большая площадь на кристалле за счёт «удвоения» количества затворов. Инженеры NeoLogic предложили исправить это, явив миру упрощённые затворы, которые они назвали «элементы с пониженной сложностью» (reduced-complexity gates). Компания NeoLogic утверждает, что её подход позволяет уменьшить размер процессоров на 40 % при одновременном снижении вдвое их энергопотребления. Чем меньше транзисторов в чипе, тем меньше энергии он потребляет. Более того, при определённой схемотехнике число транзисторов при использовании технологии CMOS+ можно будет сократить до трёх раз. Но и это ещё не всё. В рукаве NeoLogic есть ещё два туза: «одноуровневые затворы» и новая архитектура буфера обмена. В обычных условиях CMOS-чипы имеют ограниченное число входов для обработки данных. Увеличение таковых для распараллеливания вычислений значительно усложняют схему и увеличивает потребление. NeoLogic заявляет, что её технология CMOS+ позволяет добиться небывалого параллелизма за счёт одноступенчатых затворов транзисторов. По словам компании, эти затворы могут обрабатывать значительно больше данных параллельно, чем стандартная схема CMOS, при меньшем потреблении энергии. Наконец, буферы в схемотехнике CMOS+ оптимизирован для повышения энергоэффективности. В частности, NeoLogic предлагает увеличить площадь под буфер (какая неожиданность!). Компания NeoLogic была основана в 2021 году главным исполнительным директором Ави Мессикой (Avi Messica) и техническим директором Зивом Лешем (Ziv Leshem). Разработчики уверены, что процессоры на базе CMOS+ будут пригодны для работы с моделями искусственного интеллекта. Компания считает, что её технология позволит работать в режиме принятия решений с меньшими энергозатратами, чем видеокарты. Samsung начнёт выпускать 2-нм чипы до конца года — это последний шанс вернуть доверие Nvidia и Qualcomm и спасти полупроводниковый бизнес

17.06.2025 [10:35],

Сергей Сурабекянц

Samsung возлагает большие надежды на 2-нанометровый производственный процесс. Оба предприятия компании должны освоить массовое производство по этому техпроцессу до конца года. В случае успеха Samsung рассчитывает перехватить часть заказов у TSMC и переломить негативное развитие событий для своего полупроводникового подразделения. Источник изображения: Samsung Предыдущий опыт Samsung с транзисторами GAA (Gate-all-Around) должен помочь ей быстрее отладить 2-нанометровый техпроцесс. В 2024 году Samsung стала первой компанией в мире, которая смогла массово применять технологию GAA-транзисторов для производства чипов. Samsung приступила к исследованию технологии GAA ещё в начале 2000-х годов и впервые внедрила её для своего 3-нм техпроцесса в 2022 году. Однако из-за мировой экономической нестабильности, высокой стоимости производства, а также ограниченной клиентской базы в таких секторах, как мобильные устройства, спрос на 3-нм техпроцесс Samsung оказался несущественным. Как результат, лидерство в производстве 3-нм чипов перешло к тайваньскому контрактному производителю чипов TSMC, который использует более традиционные (и дешёвые) методы производства транзисторов. Теперь Samsung вынуждена сделать ставку на 2-нанометровый техпроцесс после того, как 3-нанометровая технология не получила должной популярности у заказчиков. Компания на протяжении последнего времени пытается получить достаточно значимые заказы от крупных разработчиков микросхем на фоне практически абсолютного доминирования TSMC. На данный момент Samsung, в дополнение к производству собственного чипа Exynos 2600, удалось заключить договор на производство 2-нм чипов для японской компании Preferred Networks. TSMC, в свою очередь, планирует начать массовое производство по 2-нанометровому техпроцессу на своих заводах в Баошане и Гаосюне на Тайване в конце этого года. Предприятия TSMC станут первыми фабриками, на которых будет применена технология GAA к узлу 2-нм. Похоже, что Samsung не удалось сохранить лидерство в этой сфере. Судя по многочисленным сообщениям, выход годных чипов по 2-нанометровой технологии TSMC уже достиг 70 %, что ставит её в очень выгодное положение для начала массового производства. Неудивительно, что такие крупные компании, как Apple, Nvidia, Qualcomm и AMD, рассматривают TSMC в качестве основного поставщика чипов. Ближайшие полгода покажут, сможет ли Samsung возродить доверие к своему полупроводниковому производству для возвращения таких заказчиков, как Nvidia и Qualcomm. Micron выпустила первую в мире память LPDDR5X класса 1γ для тонких флагманских смартфонов с ИИ

04.06.2025 [16:23],

Николай Хижняк

Компания Micron сообщила о начале поставок тестовых образцов первых в мире энергоэффективных чипов памяти LPDDR5X, произведённых по передовому техпроцессу 10-нм класса 1γ (гамма). Эти микросхемы ориентированы на повышение ИИ-производительности флагманских смартфонов.

Источник изображения: ZDNet По данным южнокорейского издания ZDNet, техпроцесс 1γ знаменует собой шестое поколение памяти DRAM 10-нм класса, массовое производство которой, как ожидается, будет наращиваться к концу этого года. Узел имеет ширину линии порядка 11–12 нанометров и в полупроводниковой промышленности Южной Кореи обычно обозначается как 1c DRAM. LPDDR5X — это наиболее передовое поколение энергоэффективной DRAM, доступное на сегодняшний день на рынке. Основное применение данной памяти — мобильные устройства и ноутбуки. Согласно пресс-релизу Micron, компания в настоящее время проводит испытания 16-гигабитных чипов LPDDR5X на базе техпроцесса 1γ с избранными партнёрами и планирует предложить полный спектр ёмкостей — от 8 до 32 Гбайт — для использования во флагманских смартфонах 2026 года. В пресс-релизе также говорится, что данная память LPDDR5X обеспечивает самую высокую в отрасли скорость для LPDDR5X — 10,7 Гбит/с — и демонстрирует до 20 % более высокую энергоэффективность по сравнению с другими аналогичными решениями. Память упакована в самый тонкий для LPDDR5X корпус толщиной всего 0,61 мм. По словам Micron, это на 6 % тоньше, чем у конкурирующих продуктов, и на 14 % тоньше по сравнению с её собственной памятью LPDDR5X предыдущего поколения. Компания также подчёркивает, что LPDDR5X на базе техпроцесса 1γ является её первым решением в сегменте мобильной памяти, при производстве которого применяется передовая EUV-литография. В феврале этого года Micron объявила о первых поставках образцов памяти DDR5 на основе техпроцесса 1γ таким клиентам, как Intel и AMD. Согласно пресс-релизу, Micron также остаётся единственной компанией, поставляющей чипы памяти HBM3E и SOCAMM для ИИ-серверов. Производитель отмечает, что его память SOCAMM LPDDR5X, разработанная при поддержке Nvidia, поддерживает специализированный ИИ-чип GB300 Grace Blackwell Ultra. Южнокорейские конкуренты Micron — компании Samsung и SK hynix — также разрабатывают собственные чипы памяти 1c DRAM. В августе прошлого года SK hynix объявила о создании первых в индустрии 16-гигабитных чипов памяти DDR5 на основе узла 1c — шестого поколения 10-нм техпроцесса. По данным MoneyToday от января 2025 года, компания завершила подготовку к массовому производству чипов 1c DDR5. Компания Samsung, в свою очередь, отложила развитие шестого поколения 10-нм техпроцесса DRAM (1c) до июня 2025 года. Intel собралась обогнать TSMC — раскрыты подробности технологии Turbo Cells для 14-ангстремного техпроцесса

01.05.2025 [08:52],

Анжелла Марина

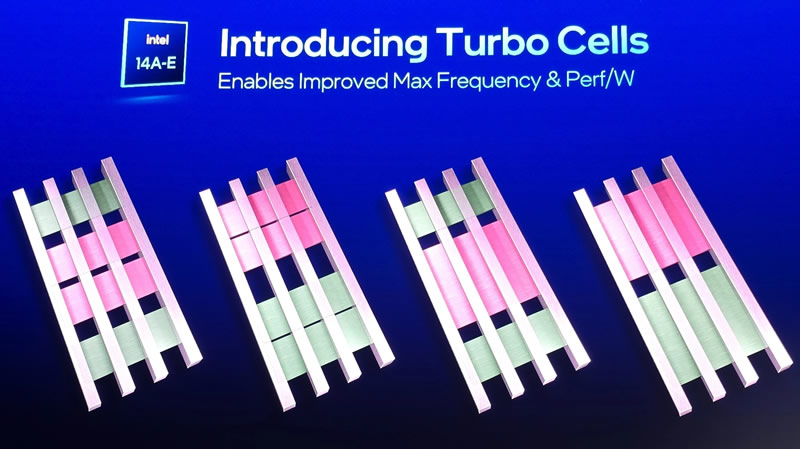

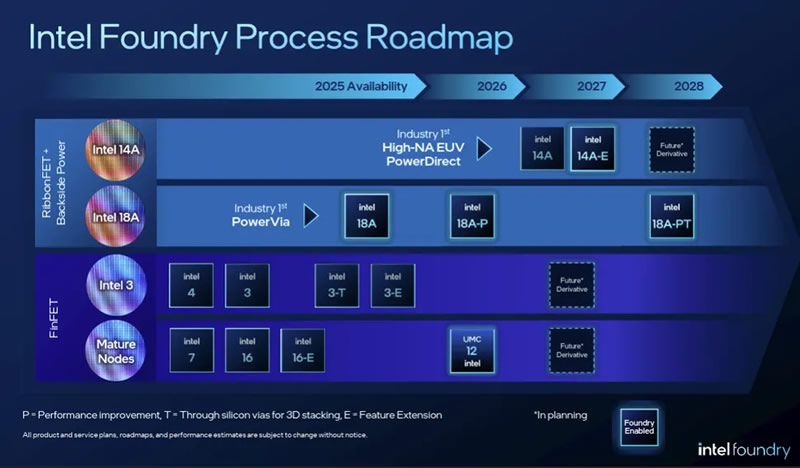

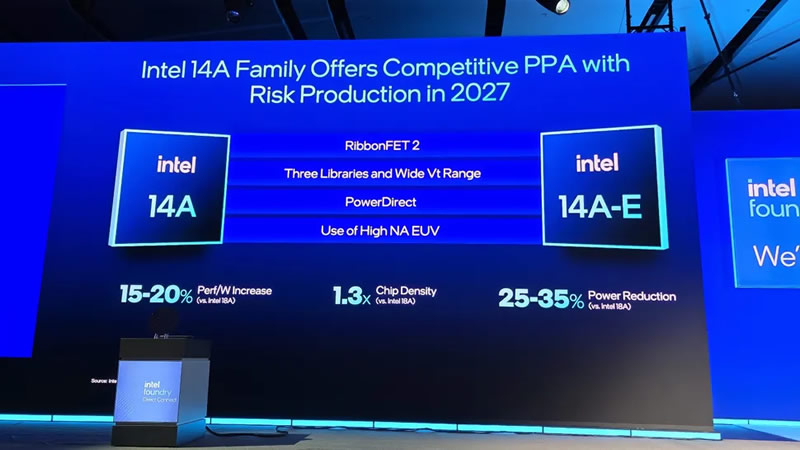

Компания Intel представила технологию Turbo Cells («турбо-ячейки»), позволяющую ускорить критически важные участки логических цепей процессора без увеличения энергопотребления, сообщает Tom's Hardware. Вместе с новым техпроцессом 14A, обеспечивающим на 30 % более высокую плотность транзисторов по сравнению с 18A, и системой питания PowerDirect, это может обеспечить прорыв в производительности чипов будущих поколений.

Источник изображения: Tom's Hardware Intel впервые раскрыла информацию о техпроцессе 14A в прошлом году. Теперь, на своём мероприятии Intel Foundry Direct 2025, компания объявила, что по сравнению с 18A он обеспечит улучшение удельной производительности на ватт на 15–20 % и увеличение плотности транзисторов на кристалле на 30 %. В техпроцессе 14A будут использоваться самые последние достижения Intel: GAA-транзисторы RibbonFET 2 с расширенным пороговым напряжением, второе поколение технологии подвода питания с обратной стороны кристалла PowerDirect и передовая EUV-литография с высокой числовой апертурой (High-NA).

Источник изображения: Intel Принципиально новым моментом в техпроцессе Intel 14A станет поддержка дизайна Turbo Cell. Это позволит дополнительно поднять частоту критических частей CPU и GPU за счёт возможности совмещать «быстрые» и «энергоэффективные» транзисторы внутри одного функционального блока чипа, что позволит значительно повысить общую производительность без серьёзных компромиссов. Intel также представила три типа стандартных библиотек ячеек для 14A. Библиотека tall — для максимальных частот, mid-size оптимизирована под энергоэффективность и short ориентирована на максимальную плотность. Именно последняя активно используется в CPU и GPU, и именно в неё интегрируются Turbo Cells. По словам Intel, в конечном итоге Turbo Cells позволят гибко комбинировать ячейки с разной производительностью и энергопотреблением в одном конструктивном блоке для достижения идеального соотношения трёх ключевых параметров — мощности, производительности и площади кристалла, которые лежат в основе современного чип-дизайна. Сообщается, что освоение техпроцесса 14A идёт по плану. Компания уже готова предоставить партнёрам библиотеки для проектирования чипов под этот техпроцесс и сделать по их проектам тестовые кристаллы. Запустить производство по техпроцессу 14A компания Intel рассчитывает в 2027 году. Одновременно TSMC наметила внедрение похожего техпроцесса A14 на 2028 год, но в нём не будет применяться ни EUV-литография с высокой числовой апертурой, ни подвод питания с обратной стороны кристалла. А значит, Intel имеет возможность перехватить лидерство в гонке техпроцессов. Intel анонсировала техпроцесс 14A с «турбо-ячейками» и 18A-PT с 3D-штабелированием

29.04.2025 [23:30],

Анжелла Марина

Глава Intel Лип Бу Тан (Lip Bu Tan) объявил на мероприятии Intel Foundry Direct 2025 о значительных успехах на направлении контрактного производства полупроводников. В частности, Intel привлекла первых клиентов для своего перспективного техпроцесса 14A (1,4 нм), который станет следующим шагом после 18A. Уже несколько заказчиков готовятся к получению тестовых 1,4-нм чипов.

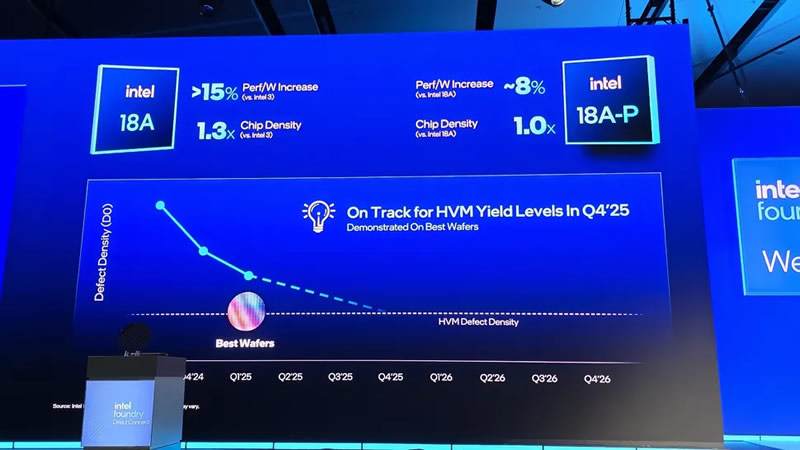

Источник изображения: Tom's Hardware Как стало известно Tom's Hardware, технологический процесс 18A, играющий ключевую роль в стратегии Intel, уже перешёл на этап пробного производства (risk production), при котором осваиваются первые производственные циклы для отладки технологии. Старт серийного выпуска чипов по этому техпроцессу ожидается во второй половине года. Кроме того, компания представила Intel 18A-P — высокопроизводительную версию базового техпроцесса, уже запущенную в пробное производство.

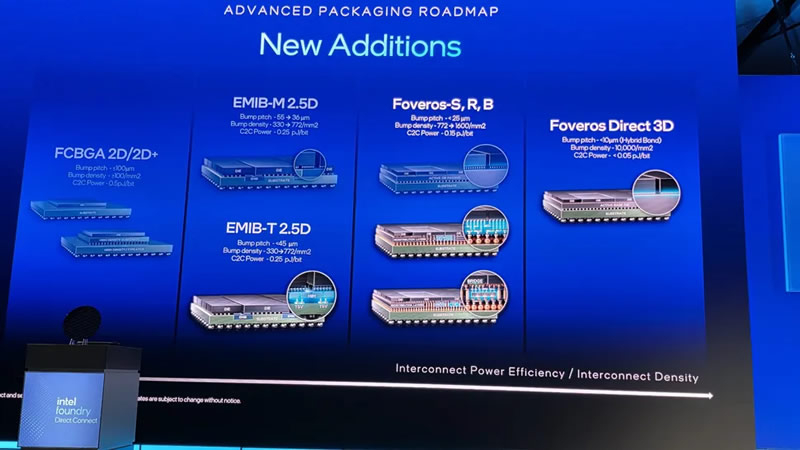

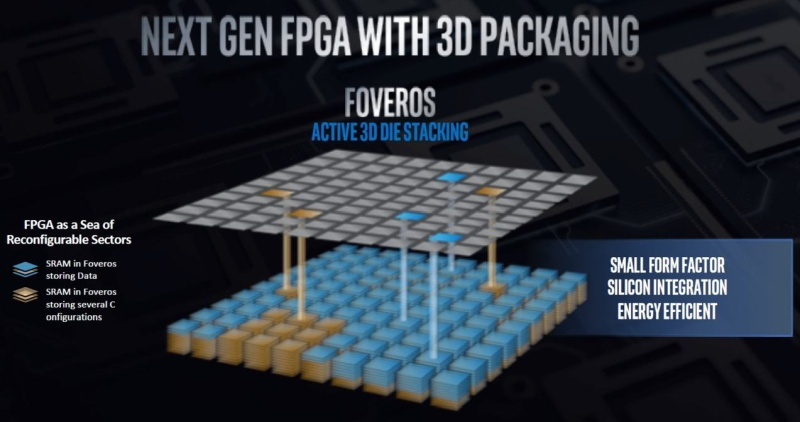

Источник изображения: Tom's Hardware Но ещё больший интерес вызывает версия Intel 18A-PT, предназначенная для применения вместе с технологией Foveros Direct 3D, благодаря которой становится возможной трёхмерная упаковка кристаллов, когда чипы можно будет размещать друг над другом, увеличив тем самым производительность и плотность компоновки. Отметим, аналогичную технологию TSMC уже применяет в чипах AMD с 3D V-Cache.

Источник изображения: Intel В сегменте зрелых техпроцессов Intel также демонстрирует прогресс. Компания уже подготовила проекты чипов сторонних клиентов для массового производства по 16-нм техпроцессу. Также в Intel отметили, что совместно с UMC ведётся разработка 12-нм технологии для сторонних заказчиков. Параллельно компания расширяет сотрудничество с партнёрами в области EDA-инструментов и готовых дизайнов блоков чипов, что упростит разработку новых чипов. При этом в рамках программы Intel Foundry Accelerator Alliance появились подразделения Chiplet Alliance и Value Chain Alliance в целях ускорения внедрения передовых решений. Важно отметить, что на фоне геополитической напряжённости в полупроводниковой отрасли Intel остаётся единственным американским производителем, способным выпускать передовые чипы, предлагая современные методы упаковки. В то время как TSMC наращивает мощности в США, новые законы Тайваня запрещают компании производить самые передовые технологии за пределами острова, что, по мнению экспертов, определённо даёт Intel стратегическое преимущество.  Особый интерес вызывает Intel 14A — первый в отрасли техпроцесс с High-NA EUV-литографией. Данный техпроцесс предложит транзисторы с нанолистами RibbonFET второго поколения. Пока Intel не назвала точные сроки его выхода, обозначив лишь 2027 год. Если всё пойдёт по плану, Intel опередит TSMC, которая планирует выпустить аналог в лице A14 только к 2028 году и без использования High-NA EUV. Также было отмечено, что Intel 14A будет использовать второе поколение технологии подачи питания с тыльной стороны кристалла PowerVia. Она будет представлять собой более совершенную и сложную схему, которая подает питание непосредственно на исток и сток каждого транзистора через специализированные контакты, что минимизирует сопротивление и максимизирует энергоэффективность. Это более прямое и эффективное подключение, чем нынешняя схема PowerVia от Intel, которая подключается к транзисторам на уровне контактов с помощью нано-транзисторов. Однако наиболее интригующая часть анонса Intel касательно техпроцесса 14A заключается в том, что в нём будет реализована новая технология «турбо-ячеек», предназначенная для дальнейшего увеличения скорости чипов, «включая максимальную частоту CPU» и повышение производительности GPU. «Технология Turbo Cells позволит разработчикам оптимизировать сочетание более производительных и более энергоэффективных ячеек в пределах одного вычислительного блока, обеспечивая индивидуальный баланс между мощностью, производительностью и площадью для целевых приложений», — говорится в заявлении Intel, на которое обратило внимание издание PCWorld. Пока что Intel не раскрывает подробности о функции турбо-ячеек.

Источник изображения: Intel Intel намерена продвигаться по намеченному плану, объединяя усилия в области 3D-упаковки и миниатюризации техпроцессов. Как отметил Тан в рамках мероприятия, такие технологии как Foveros Direct 3D, дадут клиентам компании важные конкурентные преимущества. С докладом также выступят ключевые спикеры компании — технический директор Intel Foundry Нага Чандрасекаран (Naga Chandrasekaran) и руководитель подразделения Foundry Services Кевин Бакли (Kevin Buckley), которые подробнее расскажут о планах и технических деталях. TSMC раскрыла, когда начнёт выпускать 1,4-нм чипы с нанолистами — анонсирован техпроцесс A14

24.04.2025 [09:09],

Дмитрий Федоров

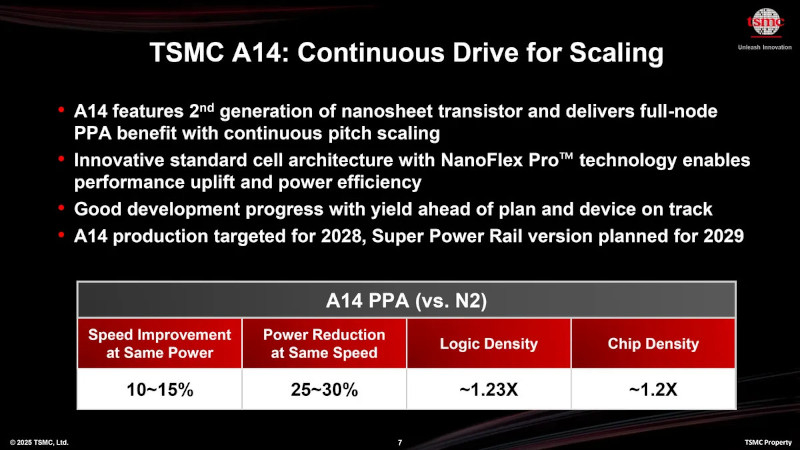

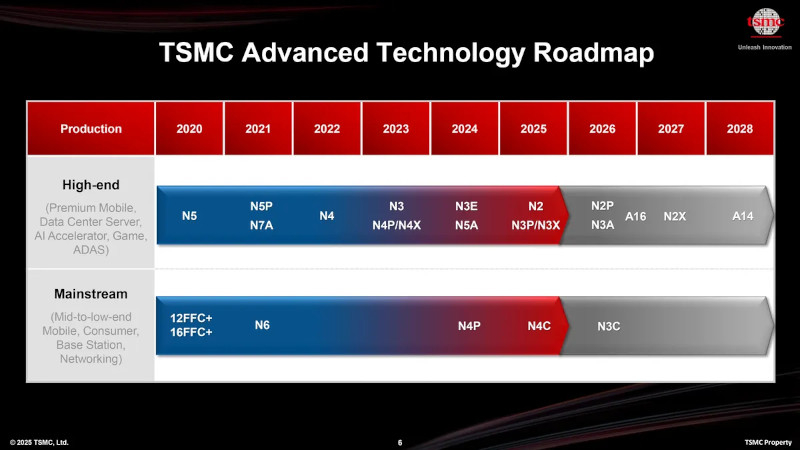

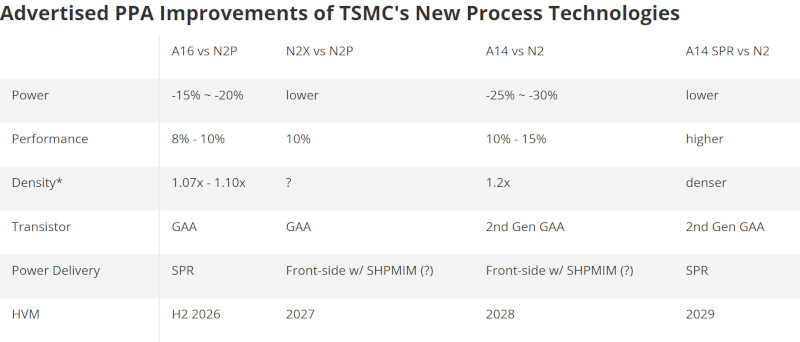

TSMC анонсировала 1,4-нм техпроцесс A14 на транзисторах Gate-All-Around (GAA) второго поколения. Технология обеспечит прирост производительности на 10–15 % при том же энергопотреблении, а также снижение потребляемой мощности на 25–30 % при сохранении частоты и логической сложности по сравнению с 2-нм N2. Плотность логических элементов повысится на 23 %, а общая плотность транзисторов в условиях смешанного проектирования — 20 %. Массовое производство запланировано на 2028 год, а версия с подачей питания с обратной стороны чипа дебютирует в 2029 году.

Источник изображения: TSMC Во время Североамериканского технологического симпозиума, компания TSMC сообщила, что A14 — это новый техпроцесс, разработанный с нуля, так что для него не подойдут дизайны чипов, спроектированные для предыдущих техпроцессов. Новая технология построена на транзисторах с нанолистами (nanosheets) второго поколения, произведённых с использованием новейшей технологии GAA. Это отличает его от техпроцесса N2P, основанного на платформе N2, и от A16, представляющего собой улучшенный N2P с системой подачи питания с обратной стороны (Backside Power Delivery — BSPDN). В отличие от A16, базовая версия A14 не поддерживает архитектуру Super Power Rail. Это снижает стоимость, но ограничивает применение технологии в сценариях, где требуется высокая плотность разводки электропитания. Однако отсутствие BSPDN делает A14 целесообразным выбором для тех приложений, в которых преимущества этой технологии минимальны или не проявляются.

Ключевые характеристики техпроцесса A14 компании TSMC по сравнению с N2. Источник изображения: TSMC Несмотря на отсутствие BSPDN, техпроцесс A14 сохраняет высокую эффективность благодаря использованию транзисторов с нанолистами второго поколения. Одним из ключевых компонентов технологии является NanoFlex Pro — усовершенствованная архитектура стандартных ячеек, предоставляющая разработчикам гибкость при конфигурировании логических блоков с учётом трёх важных метрик: производительности, энергопотребления и площади кристалла (Power, Performance, Area — PPA). Хотя компания не раскрывает технических отличий NanoFlex Pro от предыдущей версии NanoFlex, можно предположить, что речь идёт о расширенных возможностях DTCO — совместной оптимизации проектирования и технологии — а также более точной настройке на уровне ячеек и транзисторов.

Дорожная карта развития технологических узлов TSMC в сегментах High-end и Mainstream на 2020–2028 годы. Источник изображения: TSMC TSMC ожидает, что массовое производство чипов по технологии A14 начнётся в 2028 году. При этом компания пока не уточнила, в каком полугодии начнётся серийный выпуск этих чипов. Учитывая, что массовое производство по техпроцессам N2P и A16 начнётся во второй половине 2026 года, можно предположить, что производство чипов по технологии A14 будет приурочено к первой половине 2028 года. Версия A14 с архитектурой Super Power Rail (SPR) — системой подачи питания с обратной стороны микросхемы (BSPDN) — ожидается в 2029 году. Хотя официальное название этой модификации пока не объявлено, вероятно, оно будет соответствовать принятой номенклатуре TSMC и получит обозначение A14P.

* Плотность транзисторов, опубликованная компанией TSMC, соответствует «смешанному» дизайну кристалла, включающему 50 % логических элементов, 30 % ячеек SRAM и 20 % аналоговых блоков. ** При сравнении на одинаковой площади кристалла. *** При сравнении на одинаковой тактовой частоте. Источник изображения: Tom's Hardware Особенностью A14 остаётся использование системы подачи питания с лицевой стороны, аналогичной применяемой в техпроцессах N2 и N2P. Это делает архитектуру особенно уместной в клиентских и специализированных вычислительных задачах, где не требуется высокоплотная разводка линий питания, но критичны энергоэффективность и масштабируемость. По информации TSMC, техпроцесс A14 ориентирован на широкий спектр применений, включая клиентские устройства и задачи периферийных вычислений, где важна высокая производительность при ограничениях по энергопотреблению и площади кристалла. Благодаря архитектурным особенностям и параметрам, технология A14 обеспечивает сбалансированность по ключевым метрикам PPA в различных сценариях проектирования. Intel рассказала, чем ангстремный техпроцесс 18A лучше Intel 3

21.04.2025 [21:27],

Сергей Сурабекянц

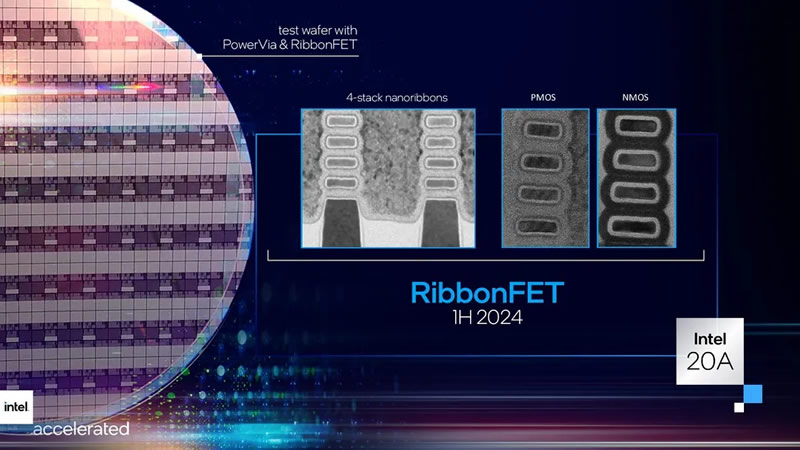

Intel рассказала о преимуществах своего 18-ангстремного техпроцесса Intel 18A по сравнению с актуальным 3-нм Intel 3 в преддверии симпозиума VLSI 2025. Intel 18A является первым техпроцессом компании, в котором используются транзисторы RibbonFET с инновационной архитектурой с круговым расположением затвора (gate-all-around, GAA) и подачей питания с обратной стороны кремниевой пластины — PowerVia (BSPDN).

Источник изображений: Intel Intel утверждает, что её техпроцесс 18A обеспечивает на 25 % большую производительность при том же напряжении (1,1 В) и сложности, а также снижает энергопотребление на 36 % при той же частоте и напряжении (1,1 В) для стандартного субблока ядра Arm по сравнению с тем же блоком, изготовленным по технологии Intel 3. При более низком напряжении (0,75 В) Intel 18A демонстрирует на 18 % более высокую производительность и на 38 % меньшее энергопотребление. Intel отмечает высокую степень физического масштабирования плотности размещения элементов у техпроцесса Intel 18A по сравнению с Intel 3 как для решений с высокой производительностью (High Performance Library, HP), так и для решений с высокой плотностью (High Density Library, HD). В Intel 18A высота ячеек уменьшена с 240CH до 180CH в библиотеках HP и с 210CH до 160CH в библиотеках HD, что составляет примерно 25-процентное сокращение вертикального размера. Более плотная архитектура ячеек позволяет увеличить плотность транзисторов, что напрямую способствует повышению эффективности использования площади. Использование подключения PowerVia обеспечивает более эффективную вертикальную маршрутизацию за счёт переноса линий питания с лицевой стороны на тыльную, освобождая место для маршрутизации сигналов и дополнительно уплотняя компоновку. Кроме того, усовершенствованные структуры затвора, источника/стока и контактов улучшают общую однородность ячеек и плотность интеграции. Эти усовершенствования в совокупности позволяют Intel 18A обеспечивать лучшую производительность на единицу площади и высокую энергоэффективность, поддерживая более продвинутые и компактные конструкции чипов. Сообщается, что Intel находится на пути к началу массового производства вычислительных чиплетов для процессоров Panther Lake для клиентских ПК в конце этого года, а затем чиплетов для процессоров для центров обработки данных Clearwater Forest — в начале 2026 года. Кроме того, в середине 2025 года компания начнёт производство по техпроцессу 18A для коммерческих заказчиков. Intel также планирует представить документ, описывающий передатчик PAM-4 (Pulse-Amplitude Modulation, модуляция импульсно-амплитудного сигнала), реализованный с использованием производственного узла 18A с PowerVia BSPDN. Передатчик разработан совместно инженерами Intel, Alphawave Semi, Apple и Nvidia. Это вовсе не означает, что Apple или Nvidia начнут использовать техпроцесс Intel 18A, однако, по крайней мере, они, как и многие другие компании, заинтересованы в подтверждении его реальных возможностей. По утверждению TSMC, практически все партнёры компании (в первую очередь Apple и Nvidia) планируют использовать её технологический процесс N2 (класс 2 нм), поэтому скорее всего, он будет востребован больше, чем Intel 18A. Тем не менее, для Intel крайне важно показать, что она по-прежнему умеет и может разрабатывать конкурентоспособные технологии и обеспечивать выпуск больших объёмов полупроводниковой продукции. Intel: Panther Lake возьмут всё лучшее от актуальных Core и ангстремного техпроцесса 18A, но выйдут в 2026 году

02.04.2025 [04:34],

Анжелла Марина

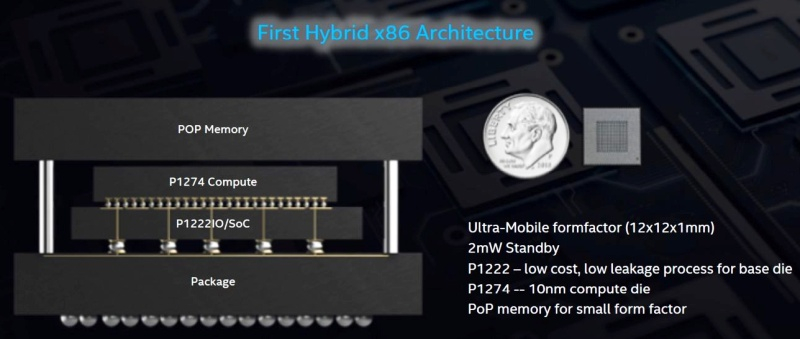

На конференции Intel Vision в Лас-Вегасе компания рассказала о грядущих процессорах Panther Lake, производство которых начнётся в конце этого года, а на рынке они появятся в начале следующего. По словам руководства компании, новые чипы объединят лучшие черты предыдущих поколений Lunar Lake и Arrow Lake — энергоэффективность и производительность, а также станут первым продуктом на новом производственном техпроцессе Intel 18A.

Источник изображения: Intel Panther Lake станет не просто очередной новинкой в линейке процессоров. Они станут первыми чипами, выпущенными по передовому техпроцессу 18A. Этот технологический шаг, как пишет PCWorld, был заложен ещё при прежнем главе компании Патрике Гелсингере (Patrik Gelsinger), который поставил цель внедрить пять технологических процессов за четыре года. Хотя Гелсингер ушёл с поста, достижение этой цели станет частью его наследия. Джим Джонсон (Jim Johnson), старший вице-президент клиентского подразделения Intel, подчеркнул, что Panther Lake сочетает в себе энергоэффективность Lunar Lake и производительность Arrow Lake. «Я лично в восторге от Panther Lake, потому что он объединяет лучшее от наших прошлых архитектур, рассчитан на масштабируемый 18A и готов к выпуску уже в этом году», — заявил он. На данный момент компания вышла на стадию опытного производства с 18A и готовит масштабирование производства для полноценного серийного выпуска.

Источник изображения: Mark Hachman / IDG Технические детали Panther Lake, скорее всего, будут раскрыты ближе к выставке Computex, которая пройдёт в конце мая, а в 2026 году Intel выпустит следующий флагманский чип Nova Lake, о чём сообщил новый генеральный директор компании Лип-Бу Тан (Lip-Bu Tan) в письме акционерам. В рамках Intel Vision был показан слайд, на котором Panther Lake указан как продукт 2026 года. Предполагается, что производство новых чипов действительно начнётся в 2025 году, однако массовый выход на рынок задержится до начала 2026-го.

Источник изображения: Intel Стоит отметить, что Intel активно инвестирует в развитие искусственного интеллекта (ИИ), привлекая разработчиков к своей платформе. В рамках этого направления компания запустила AI Showcase – витрину приложений с оптимизированными под её процессоры решениями. Также представлено новое приложение AI Playground, которое позволит пользователям запускать ИИ-модели и создавать с их помощью произведения искусства прямо на своих ПК. Что касается приоритетов Intel на 2025 год, то компания обозначила три направления, два из которых касаются внедрения искусственного интеллекта в пользовательские компьютеры, рабочие станции и автомобили. Третья задача связана с дальнейшим развитием ИИ-инфраструктуры, обеспечивающим совместимость аппаратного и программного обеспечения, снижение энергопотребления и стоимости для будущих поколений своих продуктов. Imec получит лучшие инструменты ASML для разработки техпроцессов тоньше 2 нм

12.03.2025 [20:45],

Геннадий Детинич

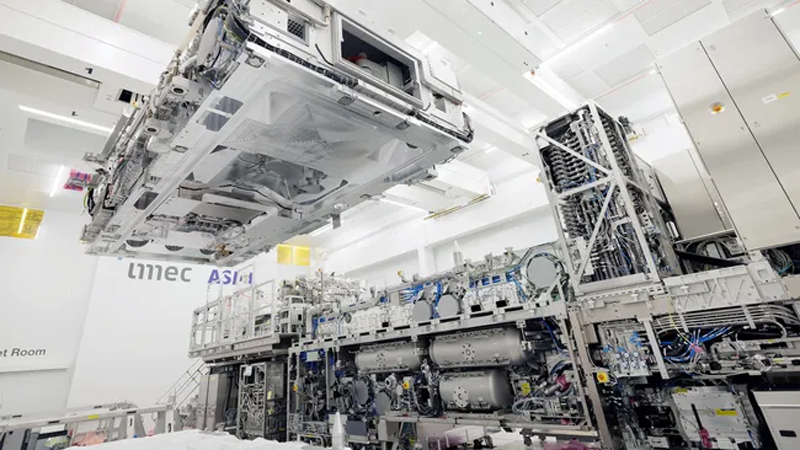

На днях бельгийский исследовательский центр Imec и компания ASML заключили пятилетнее соглашение, в рамках которого нидерландский производитель литографического оборудования предоставит Imec полный комплект самых современных инструментов для выпуска чипов и проверки качества продукции. Партнёрство позволит разработать и внедрить в промышленность техпроцессы с нормами менее 2 нм вплоть до атомарного уровня.

Источник изображения: Imec Ранее исследователи Imec пользовались передовым литографическим оборудованием на родной площадке ASML в Вельдховене, Нидерланды. Подписанное соглашение позволит разместить аналогичное оборудование на площадке Imec, что облегчит и упростит работу сотрудникам центра и их партнёрам из академических и коммерческих кругов. Новейшее оборудование от ASML, включая сканер EUV с высоким значением числовой апертуры (High-NA) стоимостью $350 млн, будет интегрировано в пилотную линию NanoIC по обработке кремниевых пластин в Бельгии. Ранее в линию NanoIC вложились ЕС и власти Фландрии. Собственно, поставка ASML во многом будет оплачена за счёт финансирования из европейских фондов и программ, направленных на разработку передовых полупроводниковых технологий. Вместе со сканером Twinscan EXE (High-NA 0,55) в Imec будут доставлены сканер Twinscan NXE (NA 0,33), Twinscan NXT (DUV, 193 нм), оптические метрологические инструменты ASML YieldStar и одно- и многолучевые инспекционные инструменты HMI. Бельгийцы получат все лучшие «игрушки» ASML, а взамен передадут для внедрения в промышленность технологии литографического производства с технологическими нормами менее 2 нм и будут разрабатывать техпроцессы двух следующих десятилетий. Отличным дополнением к совместной работе над технологическими узлами следующего поколения для логических микросхем с техпроцессом менее 2 нм, станет сотрудничество в области технологий производства DRAM, кремниевой фотоники и передовых решений для упаковки чипов — всего того, что крайне востребовано современной полупроводниковой промышленностью, явно подошедшей к технологическому барьеру классических техпроцессов. Micron первой начала поставлять чипы DDR5, выпущенные по техпроцессу 1γ с EUV-литографией — быстрые, холодные и плотные

26.02.2025 [09:54],

Геннадий Детинич

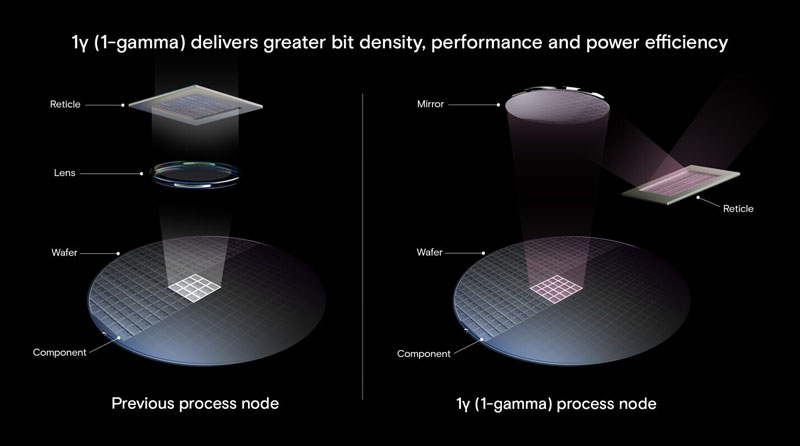

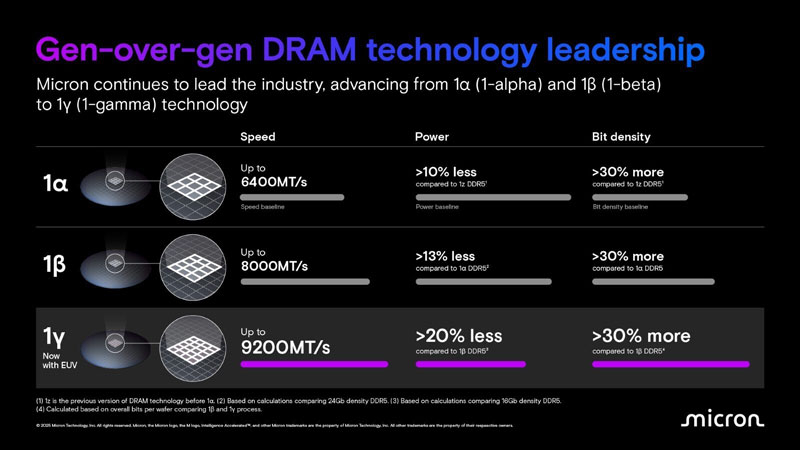

Компания Micron Technology объявила, что первой в отрасли начала поставки чипов памяти DDR5, изготовленных с использованием полупроводниковой EUV-литографии. Память поставляется избранным партнёрам для оценки эффективности самых передовых на сегодня решений. Новые чипы обладают повышенной пропускной способностью, пониженным энергопотреблением и более плотным размещением ячеек — всем, что нужно для развития ИИ, от гаджетов до серверов.

Источник изображений: Micron Новая память Micron продолжает относиться к классу 10-нм продукции. Нет точной информации, насколько цифра техпроцесса близка к 10 нм. Но это уже третье приближение к ней и, что более важно, компания наконец-то перешла к использованию литографических сканеров в экстремальном ультрафиолетовом диапазоне с длиной волны 13,5 нм (EUV). Дальше масштабирование пойдёт легче.  Если верить Micron, избранным партнёрам начали отгружаться 16-Гбит чипы DDR5. Кристаллы памяти выпущены с использованием техпроцесса 1γ (гамма). Предыдущие техпроцессы этого класса — 1α (альфа) и 1β (бета) — реализовывались с использованием сканеров с длиной волны 193 нм. Рассказывая о преимуществах чипов поколения 1γ, компания сравнивает их с чипами DDR5 предыдущего поколения — 1β. По сравнению с ними новинки на 15 % быстрее (до 9200 МТ/с), потребляют более чем на 20 % меньше энергии и обладают на 30 % большей плотностью расположения ячеек на кристалле.  Улучшенные характеристики памяти будут востребованы в периферийных устройствах с поддержкой искусственного интеллекта, в ПК с ИИ-функциями и в серверах, на которых работают большие языковые модели. Тем самым ассортимент памяти с технологическими нормами 1γ не ограничится лишь производством чипов DDR5, но также будет расширен за счёт выпуска других типов памяти, например LPDDR5X. Intel отложила запуск Xeon нового поколения и отменила ускорители Falcon Shores, но потребительские Panther Lake выйдут вовремя

31.01.2025 [18:19],

Сергей Сурабекянц

Компания Intel в рамках квартальной отчётной конференции сообщила о переносе начала поставок процессоров Xeon Clearwater Forest для центров обработки данных на первую половину 2026 года. Также компания заявила, что ИИ-ускорители Falcon Shores не будут выпущены на рынок, а послужат для тестов при разработке преемника под кодовым названием Jaguar Shores. В то же время Intel подтвердила, что поставки чипов Panther Lake для клиентских ПК начнутся по плану во второй половине 2025 года.  Задержка выпуска ключевого серверного процессора с кодовым названием Clearwater Forest произошла на фоне раскрытия компанией удручающих финансовых результатов за четвёртый квартал 2024 года и весь год в целом. В сочетании с объявленной Intel отменой ускорителей Falcon Shores, конкурентная позиция Intel на стремительно растущем рынке ИИ ослабла ещё сильнее. В настоящее время Intel наращивает производство своих энергоэффективных процессоров Xeon 6 Sierra Forest и высокопроизводительных процессоров Xeon 6 Granite Rapids. Компания рассчитывает, что эти процессоры помогут в стабилизации её доли рынка в этом году. Выход в дальнейшем процессоров следующего поколения Xeon 7 Clearwater Forest и Xeon 7 Diamond Rapids должен, по планам Intel, переломить ход событий и вернуть компании потерянную долю рынка. «Мы также добиваемся хорошего прогресса в работе над Clearwater Forest, нашим первым серверным продуктом на Intel 18A, который мы планируем выпустить в первой половине следующего года», — сказала временно исполняющая обязанности соруководителя Intel Мишель Джонстон Холтхаус (Michelle Johnston Holthaus). Она подтвердила возникшие трудности с технологией упаковки Clearwater Forest, заверив при этом, что внедрение техпроцесса 18A идёт по плану.

Источник изображений: Intel Clearwater Forest много значит для Intel, поскольку это первый процессор для центров обработки данных с вычислительными чиплетами, произведёнными по техпроцессу Intel 18A (класс 1,8 нм) и упакованный по технологии Foveros 3D. Если компания сможет добиться массового и экономически эффективного выпуска Clearwater Forest, это станет серьёзным свидетельством успеха 18A, что может привлечь потенциальных клиентов к контрактному производству Intel Foundry.  На данный момент Intel с оптимизмом смотрит на 18A. «18A — это область хорошего прогресса, — уверен финансовый директор Intel Дэвид Цинснер (David Zinsner). — Как и в любом новом процессе, на этом пути были взлёты и падения, но в целом мы уверены, что обеспечиваем конкурентоспособный процесс». Что касается графического процессора Falcon Shores, рассчитанного на рабочие нагрузки ИИ, представитель Intel посоветовал аналитикам и инвесторам умерить свои ожидания, поскольку Falcon Shores в основном будет служить тестовым чипом при разработке аппаратной и программной экосистемы следующих поколений гибридных процессоров, в частности, для своего преемника под кодовым названием Jaguar Shores. Принять такое решение компания была вынуждена в результате провала процессора Intel Gaudi 3, который не смог составить конкуренцию решениям AMD и Nvidia. В этой ситуации запуск в коммерческую эксплуатацию ещё одного неудачного продукта потенциально может похоронить репутацию компании.  «Многие из вас слышали, как я умерила ожидания в отношении Falcon Shores в прошлом месяце, — заметила Хольтхаус во время отчёта о доходах компании в четверг. — Основываясь на отзывах отрасли, мы решили использовать Falcon Shores в качестве внутреннего тестового чипа. Не выводя его на рынок, мы поддержим наши усилия по разработке системного решения в масштабе стойки с Jaguar Shores для более широкого охвата центра обработки данных ИИ». Falcon Shores — первый графический процессор Intel с многочиплетной конструкцией, основанный на ядрах Xe-HPC или Xe3-HPC. Он предназначен для обслуживания высокопараллельных рабочих нагрузок ИИ и высокопроизводительных вычислений. Продукт должен значительно повысить производительность и энергоэффективность, хотя компания воздержалась от предоставления фактических цифр.  Задержка с выпуском процессоров Clearwater Forest и отмена массового производства графических ускорителей Falcon Shores может очень дорого обойтись Intel, которая испытывает серьёзнейшие трудности и продолжает терять доверие инвесторов. США запустили расследование зависимости от олдскульных китайских чипов

23.12.2024 [18:28],

Сергей Сурабекянц

В понедельник Белый дом инициировал новое расследование в отношении китайских полупроводников, выполненных по старым техпроцессам, которые широко используются везде: от автомобилей и умного дома до оборонных систем. По мнению администрации США, Китай «регулярно применяет нерыночную политику и практику», что позволяет китайским компаниям «существенно вредить конкуренции и создавать опасные зависимости в цепочке поставок в основных полупроводниках»

Источник изображения: unsplash.com Новое расследование должно оценить зависимость США от китайских чипов, изготовленных по зрелым техпроцессам, в широком спектре технологических областей: от телекоммуникаций до электросетей. Так называемое расследование по разделу 301 будет так же изучать, по словам представителя администрации США, «действия, политику и практику Китая по производству подложек из карбида кремния или других пластин, используемых в качестве исходных материалов для производства полупроводников». Так называемые устаревшие чипы производятся с использованием менее передовых технологий производства. Китайские производители чипов по-прежнему отстают на несколько поколений от лидеров отрасли, таких как TSMC, но они способны производить устаревшие чипы в больших количествах. Расследование проводится в соответствии с Законом о торговле 1974 года. Одним из потенциальных средств правовой защиты, в соответствии с этим законом, является введение пошлин на рассматриваемую продукцию. Администрация США последовательно оказывает санкционное давление на технологический сектор Китая. Новое расследование знаменует собой эскалацию давления на полупроводниковую промышленность Китая. До сегодняшнего дня большинство действий, предпринятых США, были связаны с передовыми чипами, в частности с применяемыми в бурно развивающемся секторе искусственного интеллекта. Найден рецепт продления закона Мура: кремний «приправили» графеном и запекли при 300 °C

12.12.2024 [14:47],

Геннадий Детинич

Уменьшение техпроцессов для производства чипов почти достигло физических ограничений. Отлично показавшая себя в качестве разводки между транзисторами медь при дальнейшем уменьшении сечения проводов начала оказывать току растущее сопротивление. Потенциально её можно заменить графеном. Проблема в том, что современные технологии нанесения графена на чипы несовместимы с КМОП-процессами, применяемыми для массового выпуска чипов. Возможно, решение этой проблемы найдено.

Источник изображения: ИИ-генерация Кандинский 3.1/3DNews Предложенные ранее технологии осаждения углерода на микросхемы (транзисторы) для создания графеновых проводящих линий предполагают использование высоких температур — от 400 °C и выше. Такие температуры губительны для кремниевых транзисторов, изготовленных с применением КМОП-технологий. Необходим иной способ нанесения графена на чип, и такой способ придумали в американской компании Destination 2D. Стоит отметить, что научным консультантом Destination 2D является Константин Новосёлов — один из лауреатов Нобелевской премии по физике за 2010 год и соавтор исследования, приведшего к открытию графена в 2004 году. Предложенная компанией Destination 2D технология нанесения графена на чипы осуществляется в газовой среде под давлением от 410 до 550 кПа. Осаждение происходит не на «голый» чип, а на предварительно нанесённую на кристалл плёнку никеля. Никель выполняет роль расходного материала и впоследствии удаляется с поверхности кристалла. Внесение этого этапа в техпроцесс позволило снизить температуру осаждения графена до приемлемых для КМОП 300 °C. При такой температуре транзисторные структуры на кристалле не разрушаются, а рисунок соединений формируется с использованием графена. Также исследователи из Destination 2D решили проблему повышения проводящих свойств графена. Утверждается, что предложенный компанией особый метод легирования графена — методом интеркаляции — делает его в 100 раз более проводящим, чем медь. Это позволяет сохранить и даже увеличить плотность тока по мере уменьшения размеров транзисторов, а значит, остаётся возможность повышать плотность их размещения на кристалле. Более того, разработчики утверждают, что благодаря интеркаляции проводимость графена увеличивается по мере уменьшения размеров элементов, что даёт шанс продлить действие закона Мура ещё на несколько лет. Руководство Destination 2D верит, что пройдёт немного времени, и предложенный ими графеновый техпроцесс будет внедрён в производство передовых микросхем. Компания активно сотрудничает с рядом производителей чипов, чтобы приблизить этот момент. Intel достигла низкой плотности дефектов для техпроцесса 18A

05.09.2024 [04:27],

Анжелла Марина

На технологической конференции Deutsche Bank 2024 Intel раскрыла информацию о плотности дефектов своего передового техпроцесса 18A (1,8 нм). По словам компании, этот показатель свидетельствует о «здоровом» состоянии технологии и высоком уровне надёжности производственного процесса. Количество потенциальных заказчиков, заинтересованных в использовании 18A, растёт.

Источник изображения: Tom's Hardware Несмотря на недавнюю новость о неудачных тестах, произведённых одним из ключевых игроков в сфере сетевого оборудования и радиочипов компанией Broadcom, Intel утверждает, что количество клиентов, заинтересованных в использовании этой технологии, продолжает расти. По словам генерального директора компании Пэта Гелсингера (Pat Gelsinger), плотность дефектов (D0) уже снизилась до уровня ниже 0,4 дефекта на квадратный сантиметр. «Я рад сообщить, что для этого производственного процесса мы сейчас находимся ниже уровня плотности дефектов 0,4 d0, что свидетельствует о здоровом состоянии процесса», — заявил Гелсингер. В индустрии считается, что значение D0 ниже 0.5 дефекта на квадратный сантиметр (0,5 def/cm²) — это хороший показатель. А с учётом того, что до начала массового производства 18A остаётся ещё несколько кварталов, ожидается, что к этому моменту плотность дефектов станет ещё ниже. Для сравнения, плотность дефектов техпроцессов N7 и N5 тайваньской компании TSMC за три квартала до начала массового производства составляла около 0,33 дефекта на квадратный сантиметр, что примерно соответствует текущему состоянию 18A. При запуске массового производства N5 показатель D0 достиг 0,1 дефекта на квадратный сантиметр. Хотя плотность дефектов N3 на старте массового производства была выше, чем у N5, через пять-шесть кварталов она сравнялась с показателем N5, демонстрируя схожую динамику улучшения. Как сообщает Tom's Hardware, Intel планирует использовать 18A для производства собственных процессоров Panther Lake для персональных компьютеров и Clearwater Forest для дата-центров. Также на этом техпроцессе будет выпускаться процессор Diamond Rapids. Несколько недель назад Intel объявила о выпуске комплекта для разработки продуктов (PDK) версии 1.0 для 18A, что позволит как собственным разработчикам компании, так и её клиентам начать или завершить проектирование чипов на базе 18A. Среди заказчиков интерес к 18A проявили компания Microsoft, которая планирует использовать его для производства своих процессоров, и Министерство обороны США. «Сейчас у нас более десятка клиентов активно работают с нашим комплектом разработки 18A (PDK 1.0)», — сообщил Гелсингер. В общей сложности Intel ожидает запуска в производство восьми продуктов на базе 18A к середине 2025 года. Передовой 1,8-нм техпроцесс Intel 18A не готов к массовому производству, показали тесты Broadcom

04.09.2024 [19:14],

Анжелла Марина

Intel столкнулась с неприятным сюрпризом в рамках своего проекта по развитию контрактного производства чипов, который был запущен в 2021 году. Тесты компании Broadcom показали, что передовой технологический процесс Intel 18A не готов к массовому производству.

Источник изображения: Intel По информации Reuters, испытания передового производственного процесса Intel 18A, проведённые одним из ключевых игроков в сфере сетевого оборудования и радиочипов, компанией Broadcom, оказались неудачными. Broadcom получила от Intel кремниевые пластины с полупроводниками, выполненными по технологии Intel 18A. Но после изучения этих пластин инженеры и руководство Broadcom пришли к выводу, что процесс 18A пока не готов к массовому производству. Неудачные тесты Broadcom нанесли удар по планам Intel по развитию контрактного производства чипов, так как Intel, под руководством нового генерального директора Пэта Гелсингера (Pat Gelsinger), рассматривает контрактное производство как ключевой элемент стратегии по восстановлению своих позиций. Компания вложила около $100 млрд в расширение производственных мощностей на территории США и рассчитывает привлечь крупных контрактных клиентов, таких как Nvidia или Apple, чтобы заполнить эти мощности. Однако, несмотря на заявления представителя Intel о том, что с технологией 18A всё в порядке, и о наличии «большого интереса со стороны отрасли», компания Broadcom пока не готова делать окончательные выводы о сотрудничестве. «Мы оцениваем все предложения Intel Foundry и ещё не завершили эту оценку», — заявил представитель Broadcom. Ситуация осложняется текущими финансовыми трудностями Intel. Во втором квартале компания зафиксировала операционные убытки в подразделении Foundry в размере $7 млрд, что превышает убытки прошлого года в $5,2 млрд, а руководство Intel прогнозирует выход на безубыточность в этом бизнесе только к 2027 году. В условиях падения рыночной капитализации и сокращения инвестиций в строительство новых производств, неудача с Broadcom может ещё больше осложнить ситуацию, тем более на фоне сокращения 15 % рабочих мест и пересмотре капитальных затрат. В середине сентября совет директоров компании рассмотрит ещё один план по сокращению расходов в отдельных бизнес-подразделениях. Что касается компании Broadcom, она хоть и не столь известна широкой публике, является крупным производителем сетевого оборудования и радиочипов, её выручка от продаж чипов в прошлом финансовом году составила $28 млрд. Компания активно участвует в проектах, связанных с искусственным интеллектом, а аналитик J.P. Morgan Харлан Сур (Harlan Sur) прогнозирует, что в этом году её доходы от ИИ составят 11-12 миллиардов долларов, по сравнению с $4 млрд в прошлом году. Интересно, что Broadcom сотрудничает с Google (Alphabet) и Meta✴✴ Platforms в производстве их собственных процессоров для ИИ, что может включать в себя заключение контрактов с производителями, в том числе с Intel или TSMC. Несмотря на трудности, Intel продолжает продвигать свой техпроцесс 18A. Компания выпустила набор инструментов для других производителей чипов и, по словам Гелсингера, около десятка клиентов уже активно изучают его. Intel планирует завершить подготовку производства к концу года и начать серийный выпуск чипов в 2025 году. Однако, ситуация с Broadcom показывает, что переход на новую технологию сопряжён с рисками и может отпугнуть потенциальных клиентов, особенно учитывая стоимость производства на передовых технологических узлах, которая исчисляется несколькими десятками тысяч долларов только за одну пластину. |

|

✴ Входит в перечень общественных объединений и религиозных организаций, в отношении которых судом принято вступившее в законную силу решение о ликвидации или запрете деятельности по основаниям, предусмотренным Федеральным законом от 25.07.2002 № 114-ФЗ «О противодействии экстремистской деятельности»; |