|

Опрос

|

реклама

Быстрый переход

Intel раскрыла техпроцесс 18A-P: быстрее, экономичнее и с улучшенным теплоотводом

01.05.2026 [16:22],

Павел Котов

Компания Intel наращивает выпуск собственных чипов по технологическому процессу 18A (класс 1,8 нм) и параллельно работает над его улучшенной версией 18A-P — в стадию производства она вступит в ближайшие кварталы.

Источник изображения: Rubaitul Azad / unsplash.com Технология Intel 18A-P предусматривает два новых типа транзисторов, более жёсткий контроль вариативности процесса и улучшенный теплоотвод, что обещает повышенную производительность при сниженном энергопотреблении. Возможно, поэтому ходят слухи, что ею заинтересовались в Apple. 18A-P по сравнению с базовым 18A позволит разработчикам чипов либо повысить производительность своих компонентов на 9 % при том же энергопотреблении, либо снизить энергопотребление на 18 %, сохранив те же производительность и сложность. Чтобы добиться этого, Intel перешла на транзисторы нового типа RibbonFET с окружающим затвором и продемонстрировала их версии, оптимизированные как для повышенной производительности, так и для сниженного энергопотребления. Это означает, что можно повышать частоты на критически важных участках и сокращать энергопотребление в менее востребованных областях, что способствует росту общей эффективности системы. Технология 18A-P сохранила тот же шаг затворов транзисторов (50 нм) и те же высоты ячеек (180 нм и 160 нм), что используются в 18A, а также совместимость конструкции с технологией предыдущего поколения. То есть микросхему, которую разрабатывали для 18A, можно портировать на 18A-P и сразу улучшить характеристики чипа; однако для достижения максимальных показателей всё же потребуется повторная оптимизация архитектуры.

Источник изображения: Brecht Corbeel / unsplash.com Ещё одно преимущество 18A-P состоит в том, что Intel удалось на 30 % сократить перекос качества кристаллов в пределах одной пластины: разброс между «быстрыми» и «медленными» уменьшился — оба приблизились к типичному значению; снизилась вариативность от центра к краю пластины. В техпроцессе добавили дополнительные варианты порогового напряжения: если в оригинальном 18A допускались только четыре пары, то теперь их может быть более пяти. Это помогает точнее сортировать кристаллы, обеспечивает более стабильное поведение микросхем, а доля соответствующих целевым спецификациям кристаллов увеличивается. Повышается объём качественного кремния с одной пластины, то есть растёт выход годной продукции. Уменьшение разброса параметров, однако, никак не повлияло на частоту брака, связанную с физическими свойствами пластины и естественными отклонениями при экспозиции — тонкие техпроцессы по своей природе более чувствительны к этим факторам. Сохранив геометрию транзисторов, в Intel изменили показатели сопротивления и ёмкости на металлических линиях, что позволило повлиять на скорость сигнала, энергопотребление и величину задержки, однако конкретных значений компания не привела. Наконец, в 18A-P удалось добиться улучшений в тепловых характеристиках, надёжности и поведении напряжения — это важно как для потребительской, так и для профессиональной продукции. Intel заявила об улучшении теплопроводности на 50 %. Уменьшив тепловое сопротивление, разработчик компенсировал более высокую плотность мощности, характерную для транзисторов с окружающим затвором. Удалось сократить деградацию транзисторов, нарастающую при длительном воздействии высокого напряжения и температуры, что важно для серверной продукции. Наконец, улучшилась согласованность минимального рабочего напряжения (Vmin) логики и SRAM — повысилось качество работы при низком напряжении. Samsung догоняет TSMC: выход годных 2-нм чипов подскочил втрое и превысил 60 %

24.03.2026 [18:24],

Сергей Сурабекянц

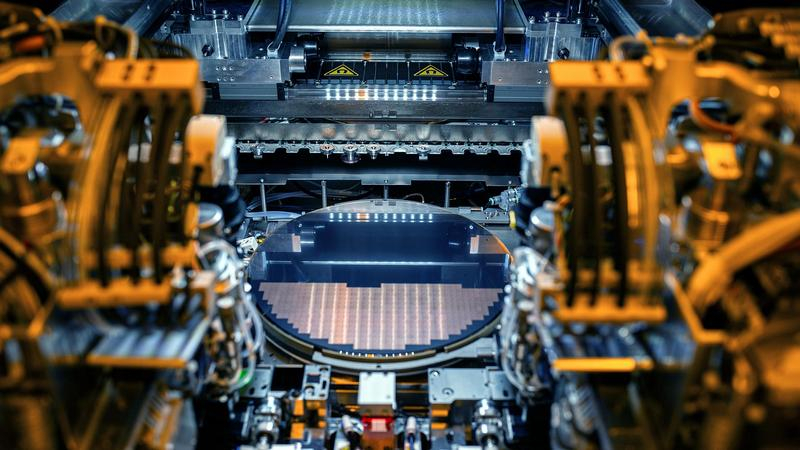

Сегодня стало известно, что Samsung Electronics повысила выход годных изделий по своему 2-нанометровому техпроцессу контрактного производства полупроводников до более чем 60 %. Ещё во второй половине прошлого года выход годных изделий не превышал 20 %. Такое существенное повышение позволит компании резко снизить производственные затраты и открывает больше возможностей для новых заказов. Источник изображения: Samsung Подразделение Samsung Electronics Foundry изготавливает чипы по 2-нм техпроцессу по заказам от подразделения Samsung Electronics System LSI Division и китайских компаний Canaan и MicroBT, которые производят оборудования для майнинга криптовалют. Сообщается, что в течение последних двух кварталов выход годных изделий для Canaan и MicroBT увеличился более чем в три раза и превысил 60 %. Средний выход годных чипов Exynos 2600 для System LSI пока остаётся ниже 50 %, но ситуация также улучшается с каждым днём. Для сравнения — ведущий мировой производитель микросхем компания TSMC в настоящее время добилась для своего 2-нм техпроцесса выхода годных изделий на уровне 60–70 %. Дальнейшее повышение выхода годных изделий для современных техпроцессов затруднено из-за их высокой сложности. Увеличение выхода годной продукции также открывает возможности для привлечения большего числа клиентов. «В последнее время наблюдается тенденция к применению передовых чипов размером менее 5 нм в информационных технологиях, — отметил представитель отрасли. — Если станет известно, что выход годной продукции в 2-нм техпроцессе Samsung Electronics улучшился, весьма вероятно, что другие клиенты заинтересуются». В прошлом году Samsung Electronics заключила контракт на производство 2-нанометрового чипа автономного вождения AI6 для крупнейшего мирового автопроизводителя Tesla. Этот контракт оценивается в $16,5 млрд. Разработан инструмент для поиска дефектов нанометровых транзисторов — отладка техпроцессов пойдёт веселее

04.03.2026 [00:10],

Геннадий Детинич

Группа учёных из Корнеллского университета (Cornell) совместно с компаниями ASM и TSMC представила революционный метод визуализации скрытых атомарных дефектов в передовых полупроводниковых структурах. Технология позволяет оценить повреждения на масштабе нескольких атомов, что важно при отладке техпроцессов производства чипов, чтобы выстроить зрелое производство с минимальным уровнем брака. Визуализация слоёв кремния, диоксида кремния и оксида гафния внутри канала транзистора. Источник изображения: Cornell Для визуализации дефектов были выбраны обработанные пластины с транзисторами Gate-All-Around (GAA) — это самые современные транзисторы с круговым или всеохватывающим затвором. Образцы предоставил бельгийский центр Imec. Каждый транзисторный канал такого транзистора — это как трубочка из 18 атомов в поперечнике. Качество стенок этой «трубочки» — неоднородности, сколы и другие дефекты — определяет характеристики транзистора. В обработанной пластине их уже не изменить, но можно проследить за качеством изготовления в процессе каждого из тысяч этапов техпроцесса, чтобы в среднем количество дефектов оказалось как можно меньше. Но как же увидеть эти дефекты, размеры которых сравнимы с размерами вирусов? Для этого исследователи адаптировали метод многоплоскостной электронной птихографии (multislice electron ptychography) с субангстремным нанометровым разрешением в глубину материала. Прибор улавливает рассеяние электронов в структуре и позволяет собирать данные для визуализации структур атомарного масштаба. По сути, это так называемая вычислительная визуализация, которая строится на скрупулёзном анализе огромного массива данных. Если чуть подробнее, то метод основан на сборе четырёхмерных дифракционных данных с помощью детектора EMPAD в составе сканирующего просвечивающего электронного микроскопа с последующей фазовой реконструкцией и моделированием распространения электронов в множественных «нарезках». В отличие от проекционных методов, птихография позволяет реконструировать полный объём структур из одного набора данных, отслеживая позиции отдельных атомов, измеряя локальные искажения решётки и количественно оценивая параметры раздела сред. Метод даёт прямые количественные оценки для спектра дефектов, ранее доступные только как наборы косвенных данных, и открывает путь к быстрому выявлению и устранению технологических проблем на ранних стадиях разработки техпроцессов. Участие в проекте специалистов тайваньского чипмейкера — компании TSMC — говорит само за себя, насколько это востребовано для отладки современного производства чипов. В Китае разработали перспективную флеш-память для ИИ с уникальным сочетанием скорости и эффективности

19.02.2026 [15:05],

Геннадий Детинич

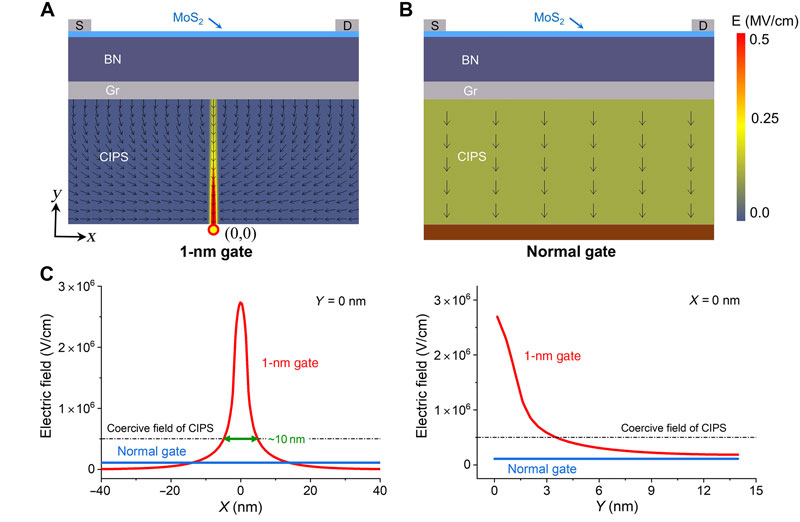

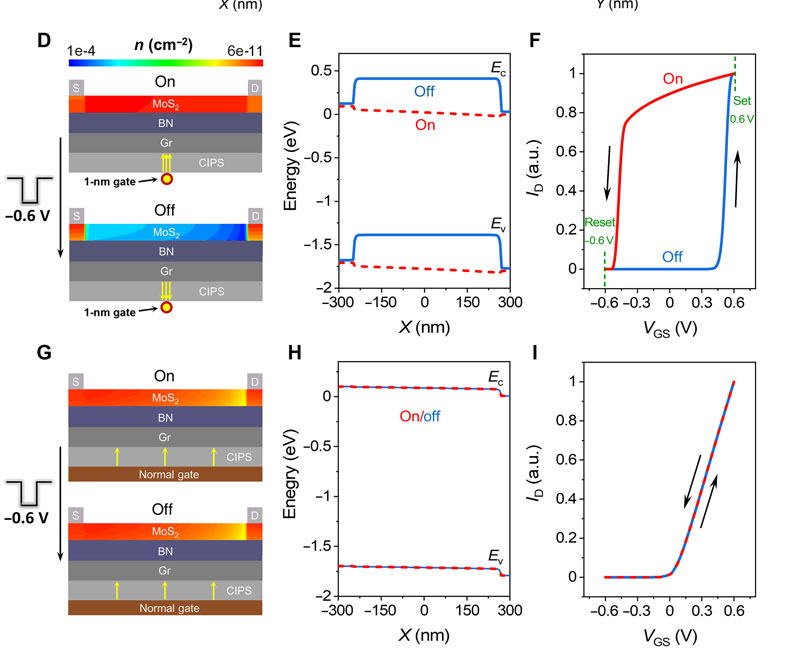

В поисках замены привычной памяти, производимой в рамках техпроцесса КМОП и приблизившейся к границам своих возможностей, разработчики снова и снова обращают взор на память с сегнетоэлектрическими транзисторами FeFET. Они обладают намного большей скоростью переключения, чем обычные полевые транзисторы FinFET, не требуют питания для сохранения состояния и потребляют сравнительно меньше энергии. Но существовали барьеры, которые им мешали. Существовали…

Источник изображений: Science Advances 2026 Команда учёных из Пекинского университета (Peking University) предложила интересное решение для масштабирования техпроцесса производства транзисторов FeFET, которое было больным местом компонентов на основе сегнетоэлектриков (в англоязычной литературе — ферроэлектриков). Также новая разработка значительно снижает управляющее напряжение таких транзисторов, которое долгое время не могло опуститься ниже 1,5 В. Очевидно, что это не позволяло им быть совместимыми с современной малопотребляющей логикой, которая давно оперирует напряжениями ниже 1 В. Китайские исследователи решили задачу оригинально — они повысили концентрацию переключающего поля затвора, за счёт чего удалось преодолеть коэрцитивное поле ферроэлектрика и переключить его поляризацию подачей меньшего напряжения. Концентрацию поля обеспечила металлическая однослойная углеродная нанотрубка (m-SWCNT) длиной 1 нм. Это и есть затвор. За счёт малого диаметра нанотрубки концентрация поля достигла рекордного уровня, и поляризацию материала транзистора удалось изменить подачей управляющего напряжения всего 0,6 В. При этом скорость переключения не пострадала, а энергонезависимые свойства FeFET сохранились. В целом предложенная структура сегнетоэлектрического транзистора с затвором 1-нм длины выглядит следующим образом: канал из MoS₂, тонкий диэлектрик h-BN (5 нм), плавающий затвор из многослойного графена, ферроэлектрический слой CuInP₂S₆ (CIPS) толщиной от 6,5 до 70 нм и затвор в виде металлической однослойной углеродной нанотрубки (m-SWCNT) длиной 1 нм. Благодаря экстремально малому радиусу кривизны нанотрубки происходит сильная концентрация электрического поля (усиление до 2,6 раза), что локально повышает напряжённость поля в сегнетоэлектрике до 2,7 × 10⁶ В/см при внешнем напряжении всего –0,6 В. Скорость программирования предложенной транзисторной архитектуры составляет 1,6 нс (при импульсе 3 В). Удержание данных превышает 10⁴ секунд, а износоустойчивость превышает 10⁴ циклов без заметной деградации. Эти параметры значительно превосходят традиционные FeFET по напряжению, скорости и потреблению.  Обозначенный прорыв позволяет впервые добиться полной совместимости по напряжению сегнетоэлектрической памяти с передовой логикой, устраняя необходимость в высоковольтных цепях и открывая перспективы для сверхэнергоэффективных ИИ-чипов, нейроморфных систем и памяти 3D-NAND. Концепция нанозатворного усиления поля универсальна и может применяться к другим сегнетоэлектрикам (HZO, перовскитам), а также интегрироваться в CMOS-процессы. Работа демонстрирует, что углеродные нанотрубки остаются актуальными для самых продвинутых технологических норм ближайшего будущего и закладывает основу для энергонезависимых технологий с техпроцессом менее 1 нм с минимальными потерями и максимальной производительностью. Кстати, в Samsung придерживаются того же мнения, но это уже другая история. Японская Rapidus начнёт массовое производство 2-нм чипов в 2027 году

15.02.2026 [22:28],

Николай Хижняк

По данным Kyoto News , на которые ссылается DigiTimes , японская компания Rapidus рассчитывает начать полномасштабное производство чипов по 2-нм техпроцессу в 2028 финансовом году. Старт массового выпуска намечен на вторую половину 2027 финансового года.

Источник изображения: Nikkei Asian Review, Rapidus Бизнес-план, представленный в Министерство экономики, торговли и промышленности Японии, предполагает выход на серийное производство к концу 2027 финансового года (до 31 марта). В течение первого года компания намерена увеличить объёмы примерно в четыре раза. Производство и обработка кремниевых пластин будут сосредоточены на заводе Rapidus в Титосэ (Хоккайдо). Площадка рассчитана как на начальные этапы, так и на последующую обработку, включая нарезку и упаковку кристаллов. К началу массового выпуска во второй половине 2027 календарного года компания планирует выйти на объём 6000 пластин в месяц, а в течение следующего года — нарастить его до 25 000 пластин. Для запуска передового производства потребуется установить более 200 единиц оборудования. Как отмечает Kyoto News, ключевой задачей остаётся повышение выхода годных изделий за счёт более точного контроля техпроцессов. Этот показатель напрямую влияет и на себестоимость, и на характеристики микросхем. Как контрактный производитель Rapidus должна обеспечить стабильный поток заказов, чтобы загрузить мощности. Рост выхода годной продукции и привлечение клиентов названы основными условиями реализации плана. Как сообщает Nikkei Asia, старший управляющий директор и глава инженерного центра Rapidus Ясумицу Ории выступил 6 февраля 2026 года на экономическом семинаре в Китакюсю. Он подчеркнул значение технологии чиплетов, позволяющей объединять разные типы микросхем на одной подложке. По его словам, компания намерена развивать автоматизацию производства и создавать высокопроизводительные решения следующего поколения. Этой весной Rapidus планирует запустить пилотную линию финальной сборки, где кристаллы будут монтироваться на подложки. Ории отметил, что подразделения, отвечающие за разные этапы производства, работают как единая цепочка, формируя непрерывный процесс. В отдельном интервью Nikkei Asia Тим Коста, генеральный менеджер по промышленному и вычислительному проектированию в Nvidia, рассказал о применении GPU в разработке и выпуске чипов. По его словам, речь уже идёт не только о литографии. Он отметил, что компания несколько лет развивает библиотеки для ресурсоёмких расчётов и сейчас способна ускорять вычисления для задач литографии до 70 раз. В случае с TSMC моделирование с использованием GPU удалось ускорить до 100 раз. По словам Косты, сфера применения GPU в полупроводниковой отрасли быстро расширяется. Если ещё пару лет назад ускорение касалось в основном литографии, то теперь графические процессоры задействуют при поиске дефектов, контроле качества и моделировании материалов. Nvidia уже сотрудничает с Rapidus и Advantest, а также ведёт переговоры с рядом других японских компаний. Intel придумала интегрированные конденсаторы нового поколения — ключ к стабильному питанию ИИ-чипов будущего

05.02.2026 [19:19],

Геннадий Детинич

В ходе рассказов о новых техпроцессах мы постоянно говорим о транзисторах как о ключевых элементах, которые определяют производительность и энергопотребление чипов. В то же время каждый элемент микросхемы по-своему важен и может считаться ключевым. Сегодня Intel похвалилась разработкой нового поколения конденсаторов — ключевых элементов для стабильной работы и питания чипов. Как и транзисторы, они тоже требуют масштабирования для новых техпроцессов.

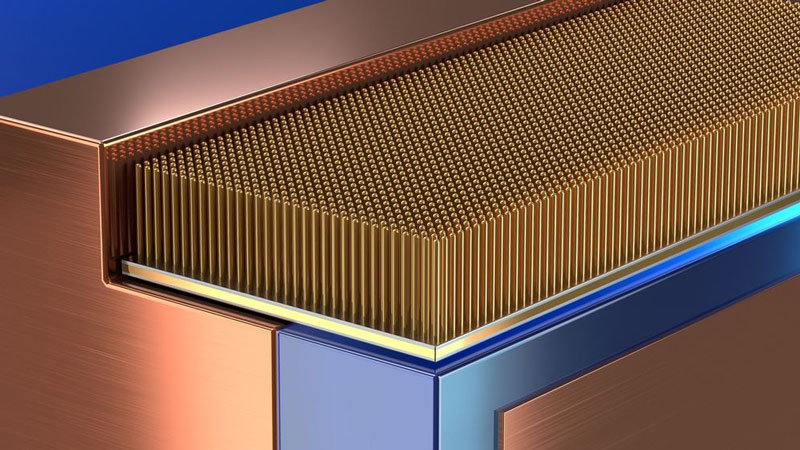

Конденсаторы Omni MIM в техпроцессе Intel 18A. Источник изображения: Intel Foundry По словам разработчиков Intel Foundry — подразделения для контрактного производства чипов, интегрированные конденсаторы нового поколения могут считаться значительным прорывом в технологиях распределения питания в чипах эпохи искусственного интеллекта. Речь идёт о разработке нового поколения MIM-конденсаторов (металл-изолятор-металл), которые позволяют радикально улучшить стабильность питания в современных и будущих процессорах. Согласно публикации в блоге Intel Community, эти конденсаторы демонстрируют почти трёхкратное увеличение плотности ёмкости по сравнению с существующими решениями, не усложняя при этом производственный процесс. По мере миниатюризации транзисторов и роста энергопотребления ИИ- и HPC-чипов проблема стабильной подачи питания становится всё острее. Резкие скачки нагрузки вызывают просадку напряжения, а в процессоре одновременно могут переключаться миллиарды транзисторов, и каждый из них «говорит»: «Дай!» Также в цепях возникает шум, и всё вместе ведёт к снижению эффективности. Традиционно эту задачу решают конденсаторы развязки, выступая как локальные «резервуары заряда»: они мгновенно отдают ток при пиковом спросе и поглощают избыток при снижении нагрузки. Новые материалы MIM, представленные Intel, обеспечивают плотность ёмкости на уровне 60–98 фФ/мкм² (в зависимости от выбора компонентов), что в три или даже большее число раз превосходит текущие показатели, сохраняя при этом крайне низкий уровень утечек — на три порядка ниже требований в отрасли. В работе, ранее представленной на конференции IEDM 2025, Intel выделила три перспективных материала для MIM-структур: ферроэлектрический оксид гафния-циркония (HZO), диоксид титана (TiO₂) и титанат стронция (STO). Эти материалы интегрируются в стандартные «траншейные» структуры на обратной стороне кристалла, что делает технологию совместимой с существующими процессами. Внешне это выглядит как цилиндр со стержнем внутри, между которыми размещён диэлектрик. Такая структура конденсатора фактически однослойная, что упрощает производство. В настоящий момент Intel использует технологию производства конденсаторов Omni MIM, которую иллюстрирует картинка выше. Благодаря новым материалам Intel Foundry рассчитывает существенно повысить производительность на ватт чипов для дата-центров, мобильных устройств и ускорителей ИИ, где требования к мощности и плотности транзисторов растут экспоненциально. Каждый из трёх материалов представляет собой первое масштабное использование сегнетоэлектриков в качестве диэлектрических материалов. Такие материалы меняют значение ёмкости под воздействием внешнего поля, сохраняя стабильность заданных параметров. Улучшенные диэлектрические свойства новых материалов позволяют конденсаторам оставаться стабильными при нагреве до 90 °C в течение 400 000 секунд, всё это время стабилизируя питание транзисторов и самого чипа. Прогнозирование обещает транзисторам с новыми конденсаторами 10 лет непрерывной работы без электрического пробоя даже с постоянным превышением рабочего напряжения, что придётся по душе оверклокерам. Каждый из трёх материалов найдёт свою нишу: HZO представляет практичный вариант на ближайшую перспективу — с хорошей надёжностью и простой интеграцией. TiO₂ выступает как следующий шаг вперёд, предлагая более высокую ёмкость и выдающиеся возможности работы при высоком напряжении. STO же обеспечивает максимальную плотность ёмкости и предназначен для приложений, где приоритет отдаётся достижению наивысшей возможной ёмкости. На новом этапе специалисты Intel разработают техпроцессы, которые помогут встроить изготовление конденсаторов MIM с новыми материалами в действующие техпроцессы. Чуть более подробно об этом можно прочесть в блоге Intel Foundry. Гендиректор Intel рассказал об освоении 14A и работе с заказчиками

10.01.2026 [13:31],

Павел Котов

Основной новинкой от Intel на выставке CES 2026 стали процессоры Core Ultra 3-й серии «Panther Lake», но генеральный директор компании Лип-Бу Тан (Lip-Bu Tan) воспользовался мероприятием как возможностью поговорить о техпроцессе 14A (1,4 нм) и заверить потенциальных клиентов и инвесторов, что работа в этом направлении продвигается успешно.

Источник изображения: Brecht Corbeel / unsplash.com «Активно работаем над технологией 14A. Следите за новостями, 14A отлично проявит себя с точки зрения выхода годной продукции и комплекта решений для качественного обслуживания клиентов», — заявил он. Технология Intel 14A, как ожидается, будет готова к работе в массовом производстве в 2027 году, а первые версии инструментов PDK (Process Design Kit) для клиентов выйдут в начале этого. Заявление господина Тана также может означать, что у Intel уже есть минимум один клиент на производство полупроводниковой продукции с использованием технологии 14A. Актуальный техпроцесс Intel 18A, который применяется при изготовлении чипов Panther Lake, — важный этап в развитии решений компании: он знаменует переход на технологию RibbonFET транзисторов с окружающим затвором (GAA) и PowerVia — схему подачи питания с обратной стороны кристалла. Техпроцесс 14A не менее важен — в его основу ложатся разработки, которые компания сделала при разработке 18A. С появлением 14A компания перейдёт на транзисторы RibbonFET второго поколения и на схему обратной подачи питания PowerDirect второго поколения непосредственно на сток и исток транзисторов, что поможет эффективнее этим питанием управлять. Ещё одним нововведением станут узлы Turbo Cells — они помогут оптимизировать критически важные пути синхронизации, то есть повысить скорость работы чипа без значительных компромиссов по его площади или потреблению энергии. Ещё один важный для Intel момент в отношении техпроцесса 14A состоит в том, что он будет активно предлагаться другим игрокам — компания станет полномасштабным полупроводниковым подрядчиком. С 18A ей не удалось привлечь ни одного крупного клиента с заказами достаточного объёма за исключением в большей мере собственных нужд и в меньшей — нужд Microsoft и Министерства обороны США. С переходом на 14A Intel рассчитывает как минимум ещё на одного клиента с большими объёмами заказов, которые помогут производителю окупить инвестиции в разработку передового техпроцесса. Сложность в том, что утверждённый план капитальных затрат не предусматривает вложений в мощности 14A для сторонних клиентов. То есть если заказ поступит от игрока масштабов Apple, AMD, Nvidia или Qualcomm, ей придётся смириться с инвестициями в дополнительные мощности, и выход производственного подразделения на безубыточность снова будет отложен.

Источник изображения: Rubaitul Azad / unsplash.com «Когда мы привлечём клиента на Intel 14A, нам придётся наращивать расходы задолго до получения дохода. Откровенно говоря, по мере формирования определённого спроса со стороны клиентов, этот этап [выход на безубыточность], вероятно, отложится. Но, думаю, большинство инвесторов отнесётся к этому спокойно, потому что это подтвердит, что мы действительно сможем создать собственное контрактное производство чипов», — заявил в ноябре минувшего года корпоративный вице-президент Intel по корпоративному планированию и связям с инвесторами Джон Питцер (John Pitzer). Контрактные производители полупроводников традиционно обсуждают с клиентами перспективные техпроцессы ещё до введения необходимых мощностей — и наращивают мощности лишь после того, как первые клиенты возьмут на себя соответствующие обязательства. В Intel такая модель пока отсутствует, потому что основной клиент — её собственное подразделение Products Group, и мощности вводятся в первую очередь для удовлетворения собственного спроса. Особенно остро вопрос встаёт, когда речь идёт о передовом производстве: тепроцесс Intel 14A, например, требует низко- и высоко апертурного EUV-оборудования и других дорогостоящих машин. Капитальные затраты оказываются огромными, и производитель просто не может позволить себе простой мощностей — они наращиваются только при гарантированной загрузке более 80 %. С другой стороны, предложение клиентам техпроцесса без доступных мощностей может угрожать планам Intel стать контрактным производителем. Её конкуренты в лице TSMC и Samsung Foundry расширяют предприятия, когда уже есть несколько основных клиентов, и ожидается дальнейший рост спроса. Передовое оборудование, в том числе EUV-сканеры, отличают весьма продолжительные сроки поставки, и если Intel не сможет вовремя предоставить мощности новым клиентам, её план может просто рухнуть. Nvidia протестировала техпроцесс Intel 18А, но до заказов дело не дошло

24.12.2025 [19:16],

Николай Хижняк

Компания Nvidia изучала возможность использования технологического процесса 18A контрактного производителя Intel Foundry, но в итоге никаких соглашений достигнуто не было, сообщает информационное агентство Reuters, ссылаясь на знакомые с ситуацией источники.

Источник изображения: Intel Это не обязательно негативный знак для Intel Foundry, поскольку многие клиенты ранее обращались к Intel с предложением протестировать технологический процесс 18A. Для разработчиков чипов обычное дело оценивать предложения конкурентов TSMC, прежде чем принимать решение о создании дополнительных производственных мощностей. Что касается технологического процесса 18A, то общее впечатление таково, что он в основном предназначен для внутренних продуктов Intel. Будущие версии, такие как 18A-P и 18A-PT, призваны привлечь внешних клиентов и, как ожидается, станут долгосрочными продуктами Intel Foundry. Технологический процесс Intel 14A становится критически важным продуктом для Intel Foundry. Его активная разработка запланирована на 2027 год. По мере того, как Intel сотрудничает с клиентами над проектированием техпроцесса, потенциальные партнёры по производству микросхем оценивают, соответствует ли будущая технология их потребностям. Первые отзывы клиентов свидетельствуют о высокой степени удовлетворенности ходом разработки, а те, кто знаком с техпроцессом, описывают его как действительно конкурентоспособный. Более активное сотрудничество между Intel и Nvidia ожидается в 2026 году. Ранее компании подписали соглашение на $5 млрд, согласно которому чиплеты Nvidia RTX будут интегрироваться в процессоры Intel для ПК и ЦОД. Конкретных деталей на этот счёт пока нет. Технически у Intel уже есть опыт работы с GPU-тайлами в имеющихся процессорах. Поэтому логично предположить, что в будущем компания сможет выпускать процессоры либо с графикой Arc, либо с чиплетами Nvidia RTX на выбор. Как ранее заявил глава Nvidia Дженсен Хуанг (Jensen Huang), сотрудничество между компаниями в рамках создания совместных процессоров началось ещё в прошлом году в условиях повышенной секретности. Журналисты выяснили, как Китай выпускает ИИ-чипы без новейших литографов ASML

19.12.2025 [20:22],

Сергей Сурабекянц

Китайская полупроводниковая промышленность нашла обходной путь для преодоления западного экспортного контроля, модернизируя морально устаревшие литографические сканеры ASML с глубоким ультрафиолетовым излучением (DUV). Такой подход позволяет получать бо́льшую отдачу от оборудования, владение и эксплуатация которого остаются законными, что подчёркивает пробелы в нормативно-правовом режиме, призванном замедлить технологический прогресс Китая.

Источник изображения: SMIC Экспортный контроль США и Нидерландов не позволяет ASML продавать свои самые передовые литографические сканеры в Китай. Продажа установок с экстремальным ультрафиолетом (EUV) полностью запрещена, да и последние поколения DUV-литографов также подпадают под экспортные ограничения. В результате многие китайские заводы используют устаревшие системы, такие как ASML Twinscan NXT:1980i. Сообщается, что китайским производителям удалось применить эти машины для производства 7‑нм чипов, которые вполне пригодны для работы в современных ускорителях искусственного интеллекта. Стоит отметить, что в последние годы в полупроводниковой промышленности нанометры обозначают скорее прогресс поколений, чем буквальные физические размеры. По словам инсайдеров, китайские заводы смогли приобрести улучшенные платформы для пластин, оптические компоненты и датчики выравнивания на вторичном рынке. Эти усовершенствования позволили повысить точность при послойном нанесении схем, улучшить выход годной продукции и производительность без формального нарушения экспортных правил. Источник изображения: Samsung Крупнейший китайский производитель микросхем Semiconductor Manufacturing International Corporation (SMIC) и технологический гигант Huawei входят в число предприятий, которые, по слухам, производят передовые чипы, используя более старые инструменты ASML. Хотя пока остаётся неясным, насколько массовым стал этот процесс, аналитики утверждают, что результаты в виде готовой продукции говорят сами за себя. Технология использует DUV-литографы для многократного экспонирования пластин, что позволяет добиться размера элементов, обычно создаваемых с помощью EUV-машин. Конечно, такой процесс медленнее, дороже и подвержен дефектам, но модернизация компонентов помогает компенсировать некоторые из этих недостатков за счёт повышения точности и эффективности. По мнению аналитиков TechInsights, новейшие процессоры Huawei отражают самые передовые производственные возможности Китая на сегодняшний день, что свидетельствует о дальнейшем прогрессе, несмотря на технологические ограничения.

Источник изображения: Huawei США в попытках ограничить амбиции Китая в полупроводниковой отрасли оказывает давление на союзников, включая Нидерланды, Японию и Южную Корею, требуя ужесточить контроль по всей цепочке поставок и ограничить не только продажи оборудования, но и обслуживание и техническую поддержку ранее поставленных литографических машин. Компания ASML пока сохранила право на обслуживание уже поставленного в Китай оборудования, но ей запрещено повышать точность совмещения или увеличивать производительность сверх установленного уровня. Компания утверждает, что полностью соблюдает все применимые законы и не поддерживает модернизацию, превышающую установленные законом пределы. Однако, по словам осведомлённых источников, сторонние инженерные фирмы проводили модификации на месте с использованием импортных компонентов, что позволяло заводам обходить ограничения без прямого участия ASML. Бюро промышленной безопасности США изучает, какую поддержку получают китайские заводы по производству оборудования ASML, и рассматривает возможность ужесточения правил, ограничивающих даже разрешённое обслуживание. Источник изображения: GlobalFoundries Для ASML Китай остаётся важнейшим рынком. Продажи компании в Китай резко выросли перед введением санкций. На Китай приходилось более трети мировой выручки ASML в 2024 году, по сравнению с чуть более четвертью в 2023-м. ASML предупредила инвесторов, что продажи в Китай, вероятно, резко сократятся по мере полного вступления в силу ограничений, но аналитики говорят, что установленная база оборудования даёт китайским заводам возможность продолжать внедрять инновации. Эксперты отрасли предупреждают, что модернизация устаревшего оборудования не может полностью заменить доступ к передовому оборудованию от таких компаний, как TSMC или Samsung. Затраты остаются выше, а производство менее эффективным. Тем не менее, прогресс Китая свидетельствует о том, что экспортный контроль может замедлить, но не остановить его продвижение. «Стоящее дело»: Intel впечатлила клиентов разрабатываемым 14-ангстремным техпроцессом

03.12.2025 [19:39],

Сергей Сурабекянц

Техпроцесс Intel 14A — критически важный продукт для производственного подразделения Intel Foundry. Он в настоящее время находится в стадии разработки и запланирован к внедрению в массовое производство в 2027 году. Потенциальные клиенты, с которыми Intel Foundry сотрудничает в процессе разработки, высоко оценивают конкурентоспособность техпроцесса 14A не только на рынках центров обработки данных и ПК, но и мобильных чипов.  По словам Патрика Мурхеда (Patrick Moorhead) из Moor Insights & Strategy, который часто взаимодействует с руководителями отрасли, как минимум два клиента Intel очень довольны ходом разработки нового техпроцесса. «Клиенты Intel, с которыми я общался и которые видели этот узел, говорят, что 14A — это действительно стоящее дело. — сообщил Мурхед. — Он должен быть весьма конкурентоспособным не только на рынках центров обработки данных и ПК, но и мобильных чипов, что знаменует собой важный шаг для компании». «Я с нетерпением жду, когда Intel выпустит свой PDK 14A 0.5 и начнёт собирать отзывы. Однако даже без PDK я уже слышу очень позитивные отзывы, особенно учитывая прогресс с 18A, поскольку каждый новый техпроцесс основывается на предыдущих», — заявил Мурхед.

Источник изображений: Intel Техпроцесс Intel 14A будет использовать литографическое оборудование ASML для литографии в сверхжёстком ультрафиолете с высоким значением числовой апертуры (High-NA EUV). При помощи этой технологии компании за один квартал удалось обработать 30 000 кремниевых пластин в рамках тестового мелкосерийного производства. Продолжительность производственного цикла при переходе на оборудование с высокой числовой апертурой существенно сократилась. Например, если ранее на обработку кремниевой пластины тратилось три экспозиции и 40 технологических операций, то теперь их количество удалось сократить до десяти, а экспозиция требуется всего одна. Как ожидает руководство Intel, новый техпроцесс 14A обеспечит улучшение соотношения производительности и энергопотребления на 15–20 % по сравнению с 18A, либо снижение энергопотребления на 25–35 %. Кроме того, в рамках 14A будет внедрена структура транзисторов с окружающим затвором RibbonFET второго поколения и подвод питания с обратной стороны кремниевой пластины. Отдельным новшеством станет внедрение так называемых «турбо-ячеек».  «Потенциальные клиенты, с которыми я общаюсь, — а я недавно поговорил практически со всеми руководителями потенциальных ключевых клиентов Intel Foundry, — хотят быть уверенными в том, что распределение пластин будет абсолютно справедливым», — рассказал Мурхед. По его словам, каждая литографическая система ASML Twinscan EXE:5200B обрабатывает 200 пластин в час на фабриках Intel, что говорит о том, что производительности должно быть достаточно для удовлетворения всех потребностей клиентов. Техпроцесс TSMC A16 оказался никому не нужен кроме Nvidia — Apple сразу перескочит на 1,4 нм

01.12.2025 [21:23],

Николай Хижняк

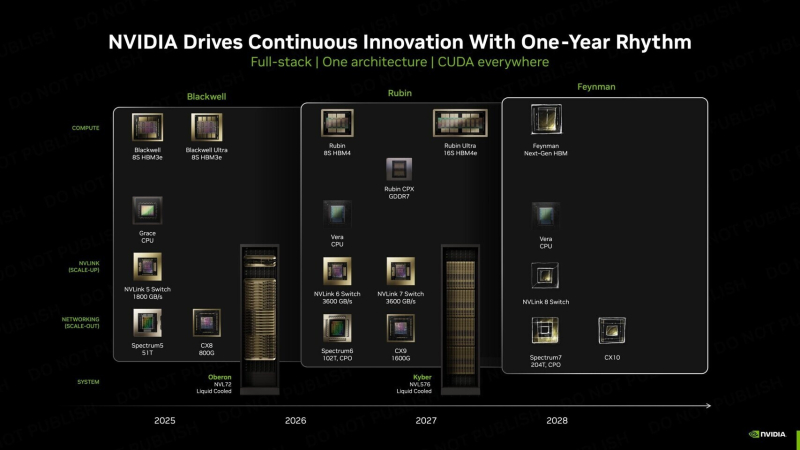

Компания Nvidia оказалась единственным заказчиком в условной очереди на техпроцесс A16 от TSMC. Компания собирается использовать его для своих будущих графических процессоров для ИИ с кодовым именем Feynman. Об этом сообщает издание DigiTimes.

Источник изображения: Nvidia Nvidia планирует начать выпуск образцов Feynman в 2026 году, а к массовому производству приступить в 2027-м. Таким образом, они появятся после ускорителей Rubin, построенных на усовершенствованном 3-нм техпроцессе. Сообщается, что Nvidia станет единственной крупной компанией, выбравшей «переходный» техпроцесс между техпроцессами N2 и A14. В свою очередь Apple резервирует мощности TSMC для выпуска продуктов на основе техпроцесса N2 (2 нм) и планирует перейти на использование техпроцесса A14 (1,4 нм), как только он станет доступен, тем самым минуя технологию A16 (1,6 нм).

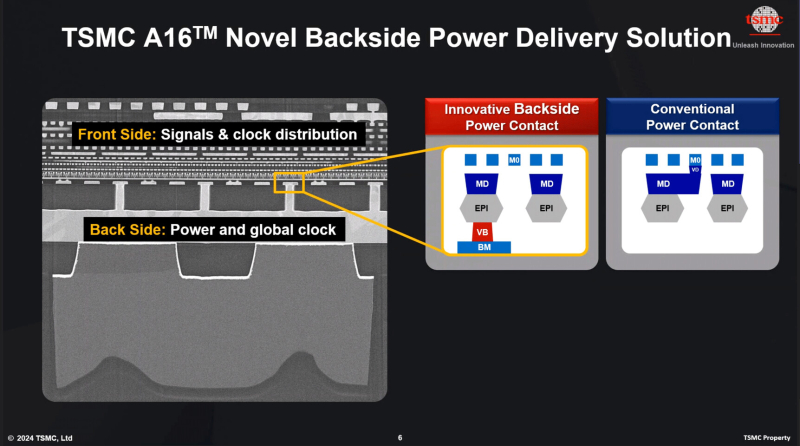

Источник изображения: TSMC Техпроцесс A16 от TSMC подразумевает использование конструкции нанолистовых транзисторов GAA с системой подачи питания с обратной стороны подложки, известной как Super Power Rail (SPR). Последняя отделяет маршрутизацию питания от сигнальных слоёв, что снижает потери при подаче. Техпроцесс обещает тактовую частоту до 10 % выше при том же напряжении, энергопотребление на 15–20 % ниже при той же частоте и сложности чипа и плотность транзисторов — на 7–10 % выше, чем у предшествующего техпроцесса N2P. Для очень больших кристаллов чипов и высокопроизводительных видеокарт эти усовершенствования могут привести к более чистой планировке, более простому управлению температурой, а также увеличению ёмкости памяти и пропускной способности межсоединений. Хотя эти улучшения существенны для чипов Nvidia, предназначенных для центров обработки данных, мобильные и портативные чипы Apple могут получить ещё больше преимуществ от менее дорогого узла N2 и его вариаций.

Источник изображения: Nvidia Помимо Apple, техпроцесс TSMC N2 и его вариации, вероятно, будут использовать AMD и другие разработчики чипов. Одной из особенностей N2 является NanoFlex — метод настройки на уровне ячеек, представленный в техпроцессе N2, который позволяет разработчикам найти баланс между скоростью и эффективностью. Этот подход позволяет добиться 15 % прироста частоты или снижения энергопотребления до 30 %. TSMC ранее подтвердила, что N2 уже находится в серийном производстве. Компания планирует начать наращивать производство по улучшенному техпроцессу N2P со следующего года. TSMC сообщила о старте серийного производства 2-нм чипов

26.11.2025 [20:36],

Николай Хижняк

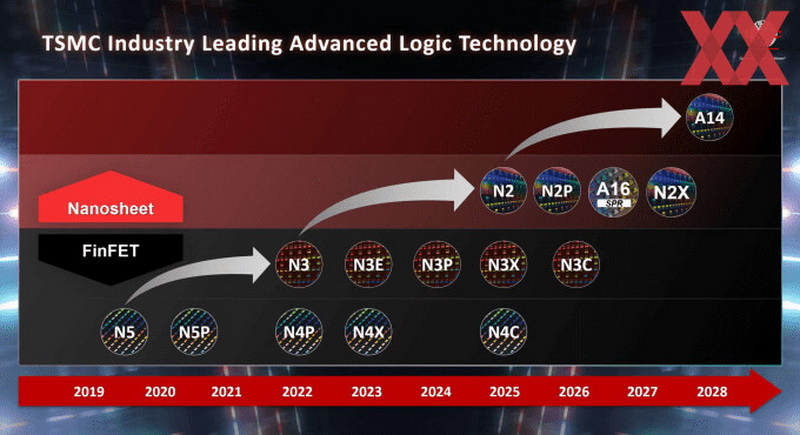

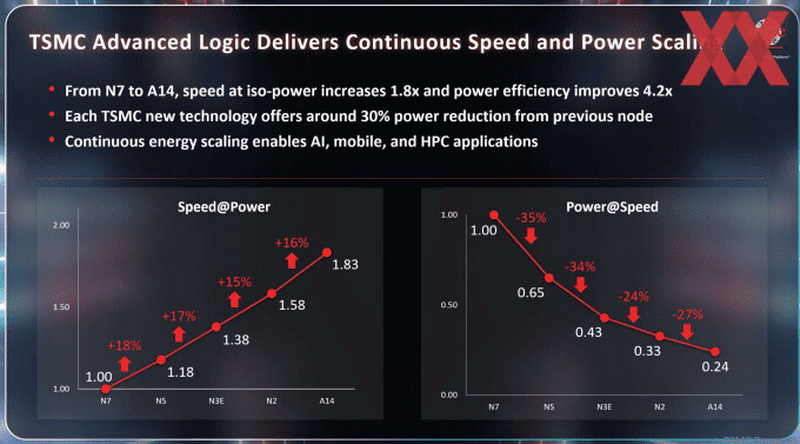

На форуме Open Innovation Platform Ecosystem Forum компания TSMC представила свои ближайшие планы по освоению техпроцессов, подчеркнув, как растущие нагрузки ИИ стимулируют разработку новых технологий с учётом баланса между производительностью и эффективностью. Также компания объявила о запуске серийного выпуска 2-нм чипов.

Источник изображений: TSMC Компания объявила, что техпроцесс N2 (2 нм) уже запущен в серийное производство и ожидает, что начнёт наращивать производство по улучшенному техпроцессу N2P в начале 2026 года. TSMC планирует выпустить первые компоненты на базе техпроцесса A16, которые сочетают транзисторы на основе нанолистов с шиной питания Super Power Rail (SPR) на задней стороне кристалла, к концу 2026 года. В дальнейшем техпроцессы будут переходить от N3 к N2 на основе нанолистов, затем к A16 с SPR и, в конечном итоге, к более продвинутому A14.  TSMC также предоставила данные, показывающие рост производительности примерно в 1,8 раза при переходе с техпроцесса N7 на A14 при постоянной мощности, а также общее повышение эффективности примерно в 4,2 раза за тот же период. Компания прогнозирует, что тактовая частота чипов на техпроцессе A16 будет на 8–10 % выше, чем у продуктов на базе N2P, при том же напряжении, а энергопотребление снизится на 15–20 % при аналогичной пропускной способности.  Для тех, кто хочет продолжать использовать FinFET, компания предлагает усовершенствованные варианты техпроцессов с FinFET, такие как N3C и N4C, причём N4C уже используется заказчиками. TSMC также отметила NanoFlex — метод настройки на уровне ячеек, представленный в техпроцессе N2, который позволяет разработчикам найти баланс между скоростью и эффективностью. Этот подход позволяет добиться 15 % прироста частоты или снижения энергопотребления до 30 %. Сотрудничество TSMC с заказчиками даёт компании значительное преимущество. Команда разработчиков техпроцессов готова вносить нужные изменения по требованию клиентов. TSMC производит чипы Blackwell с использованием технологии 4N (4 нм), разработанной специально для Nvidia. Продукт оснащён восемью стеками памяти HBM3E, помещёнными в корпус CoWoS-S. Таким образом, индивидуальная настройка техпроцессов, тесная интеграция с заказчиками и поставщиками EDA, а также лидерство в области передовых технологий производства и корпусирования чипов позволили TSMC сохранить лидирующие позиции в отрасли производства полупроводников. Японский конкурент TSMC начнёт строительство 1,4-нм фабрики чипов в 2027 году

25.11.2025 [18:32],

Сергей Сурабекянц

Компания Rapidus объявила о начале строительства своей 1,4-нанометровой полупроводниковой фабрики нового поколения в 2027 финансовом году. Rapidus планирует начать полномасштабные исследования и разработки техпроцесса в следующем году, а производство планируется запустить на Хоккайдо в 2029 году. Этот шаг, как ожидается, поможет японскому производителю микросхем сократить отставание от TSMC, которая уже представила свою 1,4-нм технологию ранее в этом году.

Источник изображения: Nikkei Asian Review, Rapidus Инвесторами Rapidus выступают японские компании, включая таких гигантов, как Toyota, Honda , Fujitsu и Sony, а также частные финансовые организации. Японское правительство также вложило значительные средства в стартап, предоставив субсидии и прямую финансовую поддержку. Rapidus уже получила инвестиции в размере 1,7 трлн иен (более $10 млрд) и ожидает дальнейших финансовых вливаний в несколько сотен миллиардов иен. Несмотря на столь существенные инвестиции, Rapidus по-прежнему сталкивается с трудностями, и отстаёт от таких производителей, как TSMC, Samsung и Intel. Intel уже начала производство по 2-нм техпроцессу 18A, в то время как TSMC также наращивает выпуск подобных передовых чипов на своей площадке в Аризоне Rapidus, как ожидается, начнёт массовое производство 2-нм чипов только во второй половине 2027 года на своём заводе в Титосе. Если вспомнить, что все известные производители полупроводников столкнулись с проблемами выхода годных изделий, прежде чем смогли приступить к массовому производству, можно предположить, что вряд ли Rapidus сможет подобных проблем избежать. Одновременно с подготовкой к началу производства по 2-нанометровому техпроцессу, Rapidus нацеливается на следующие технологические этапы — помимо ожидаемого 1,4-нм техпроцесса, на заводе на Хоккайдо в дальнейшем будут выпускаться и более совершенные 1-нм чипы. Rapidus позиционирует себя, как конкурент TSMC, но при этом изначально ориентируется на ограниченное число клиентов — от пяти до десяти. Компания утверждает, что её передовая технология корпусирования упростит производственный цикл и даст преимущество в конкурентной борьбе. Однако, по мнению бывшего генерального директора Intel Пэта Гелсингера (Pat Gelsinger), для успешной конкуренции с известными производителями чипов компании необходимо «предложить нечто более совершенное». Уровень брака у ангстремного техпроцесса Intel 18A падает на 7 % в месяц — процессоры Panther Lake не за горами

19.11.2025 [17:36],

Павел Котов

Вице-президент Intel по корпоративному планированию и связям с инвесторами Джон Питцер (John Pitzer) рассказал, что выход годной продукции — процессоров Panther Lake — с использованием технологии Intel 18A увеличивается примерно на 7 % ежемесячно.

Источник изображения: Intel Эти темпы роста соответствуют отраслевым ожиданиям относительно активного наращивания производства. В течение нескольких месяцев компания докладывала о низком выходе годной продукции, и информация, что соответствующая кривая для техпроцесса Intel 18A в целом улучшается, вселяет надежду на запуск массового производства процессоров Panther Lake в срок. За последние семь–восемь месяцев положительная динамика была стабильной, и если ежемесячный прирост на 7 % сохранится, то у Intel будет шанс обеспечить массовое производство Panther Lake без существенного увеличения себестоимости продукции. Но сроки их поставок клиентам будут зависеть от темпов наращивания производства и решений по мощностям. В отношении технологии Intel 14A господин Питцер также настроен оптимистично. Сейчас эта технология находится в лучшем состоянии, чем была 18A на той же стадии разработки. С развёртыванием Intel 18A компания уже перевела чипы с FinFET на архитектуру транзисторов с окружающим затвором (GAAFET) и добавила схему питания на тыльной стороне кристалла. У Intel 14A оба этих решения уже выполняются по стандартам второго поколения, и по новой технологии компания, заверил её вице-президент, опережает график. Intel показала Arm-процессор на ангстремном техпроцессе 18A

15.08.2025 [16:33],

Анжелла Марина

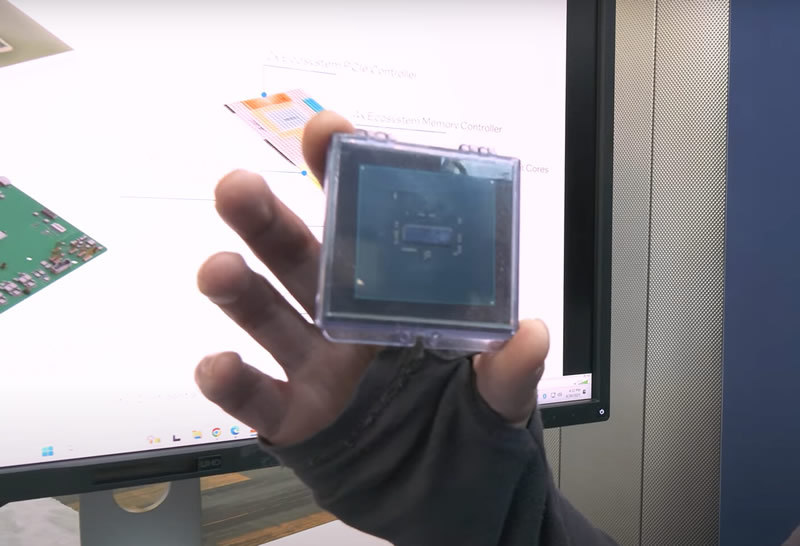

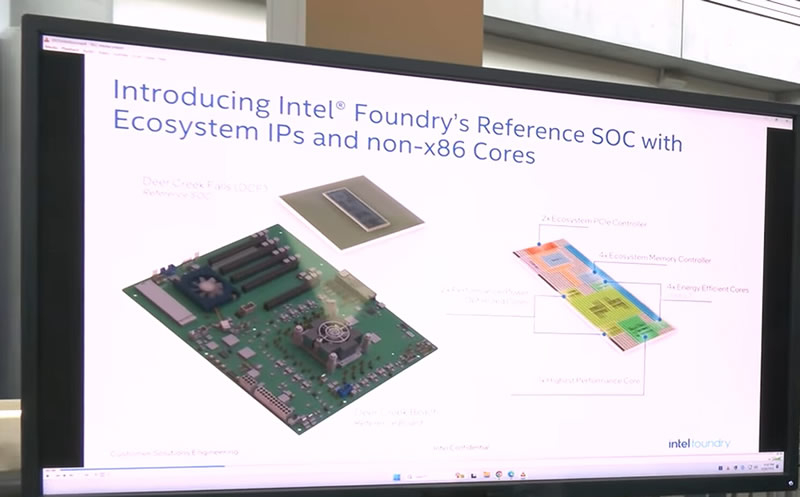

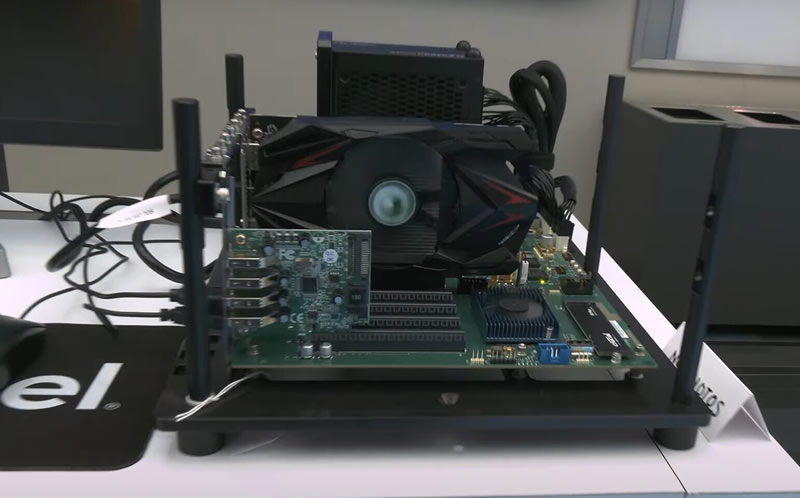

Компания Intel показала эталонный Arm-процессор, произведённый по технологическому процессу 18A. Таким образом компания продемонстрировала расширение возможностей Intel Foundry за пределы x86-архитектуры. Представленный SoC под названием Deer Creek Falls — это гибридный чип с семью ядрами: одним высокопроизводительным, двумя энергоэффективными и четырьмя с низким энергопотреблением, все на архитектуре Arm.

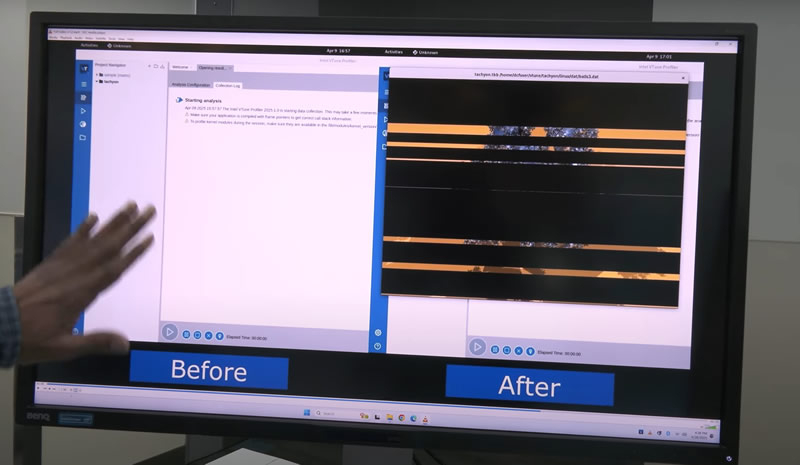

Источник изображений (скриншоты): Intel/YouTube В состав чипа также входят контроллеры памяти, PCIe-интерфейсы и PHY-блоки от партнёров экосистемы. Хотя в презентации Intel официально не акцентировала внимание на Arm-архитектуре, в разделе о настройке производительности появилось упоминание об AArch64 — термине, используемом Arm для обозначения 64-битной версии своей архитектуры, что явно указывает на её принадлежность к Arm. Интересно, что к моменту публикации Intel удалила ролик, в котором демонстрировала эталонный чип. Неизвестно, с чем это связано, однако стараниями TechPowerUp в Сети остались скриншоты.  Intel показала, что её инструменты оптимизации чипов применимы не только к x86-процессорам, но и к решениям на других архитектурах. Таким образом, клиенты Intel Foundry — подразделения Intel, занимающегося контрактным производством полупроводников, — смогут настраивать и оптимизировать свои платформы перед производством, независимо от используемой архитектуры набора инструкций (ISA).  Несмотря на то, что техпроцесс Intel 18A пока не вызвал большого ажиотажа у внешних заказчиков, компания планирует активно использовать его в собственных продуктах. Ранее рассматривалась возможность отложить наращивание мощностей 14A до подтверждения спроса, но, по всей видимости, этот подход отменён. Теперь Intel продолжит развитие передовых узлов без привязки к предварительным заказам. Также сообщается, что Apple и Nvidia уже изучают возможности 14A, что может дать Intel Foundry долгожданный импульс для роста.  В ближайшие кварталы поток заказов Intel может увеличиться, особенно с учётом поддержки со стороны властей США в рамках программы по развитию отечественного полупроводникового производства. |